Изобретение относится к области вычислительной техники и может использовано при построении арифметических устройств вычислительных маишн с плаваю- uieft запятой.

Целью изобретения является повышение точности результата при сложении числа, имеющего отрицательный порядок, с нулевым числом.

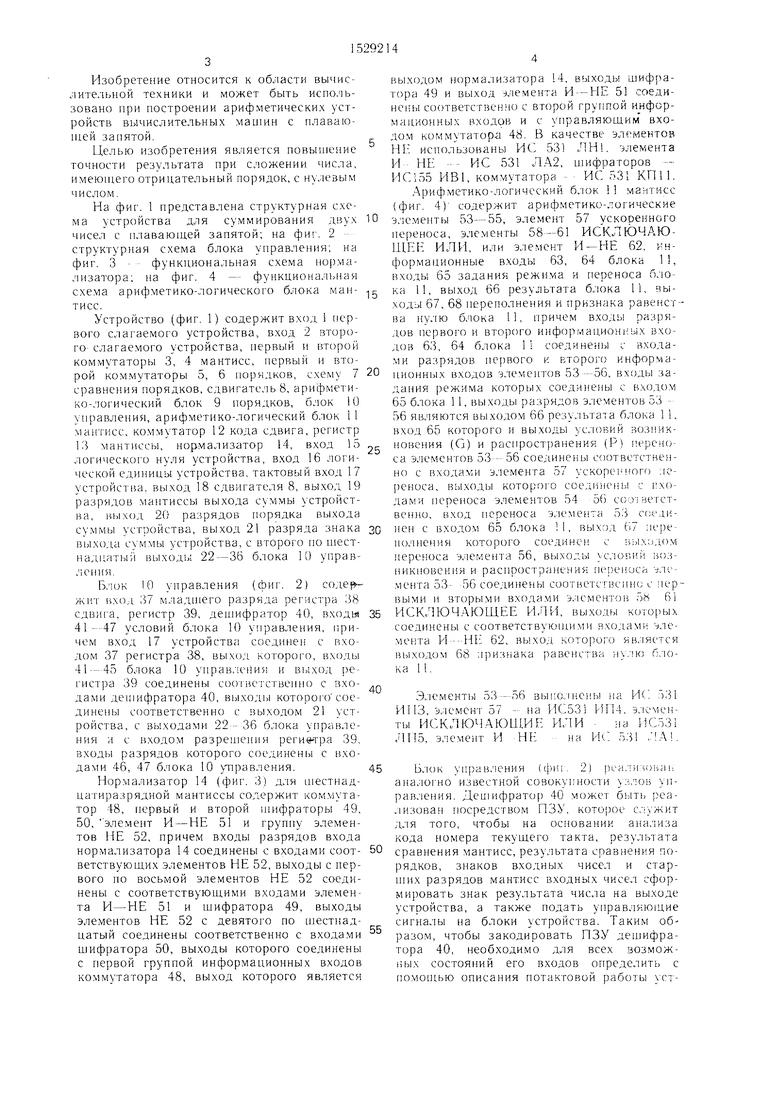

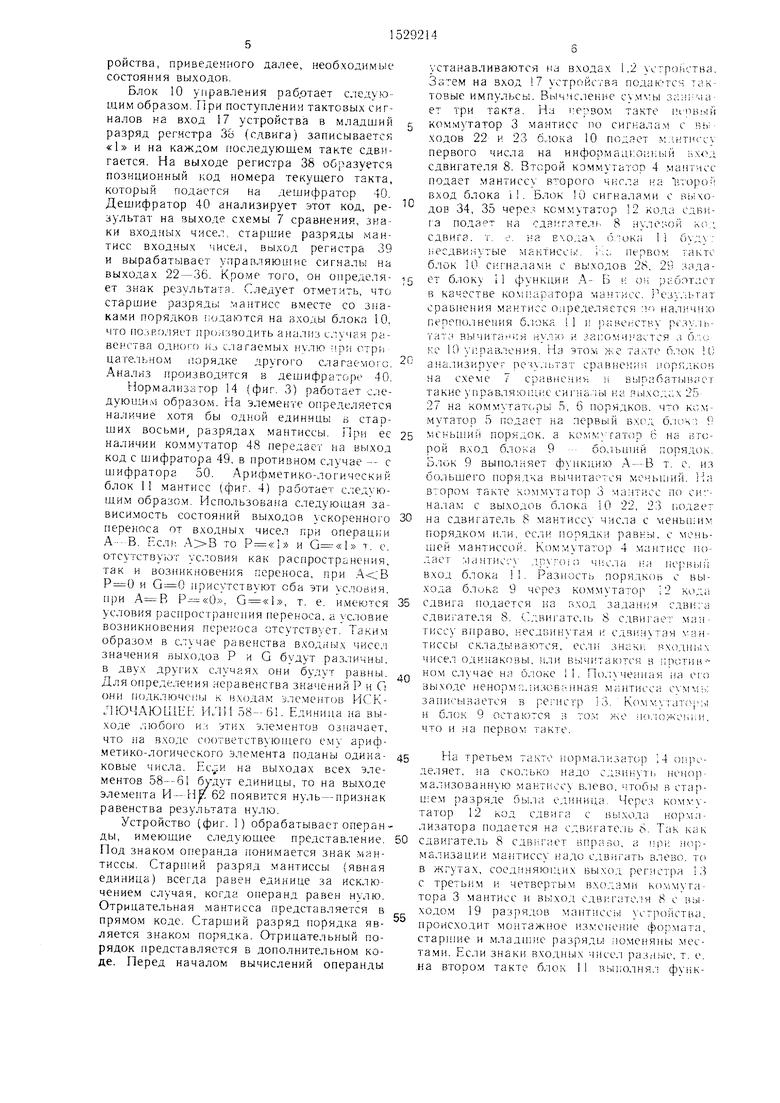

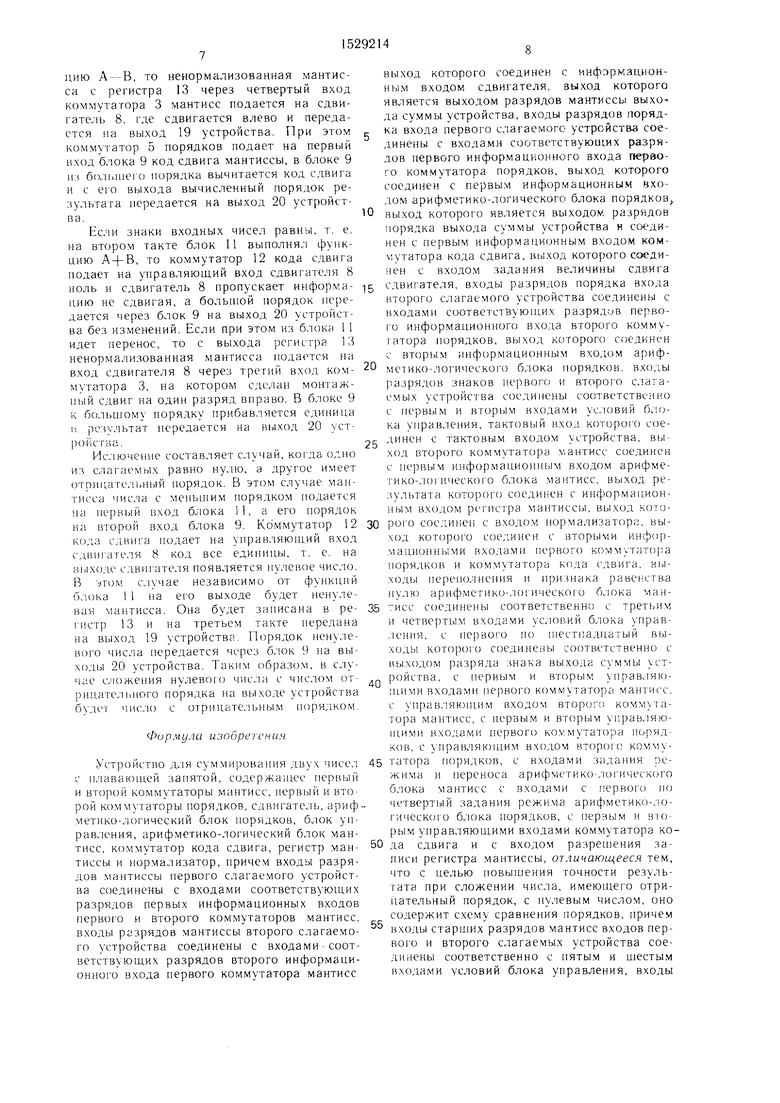

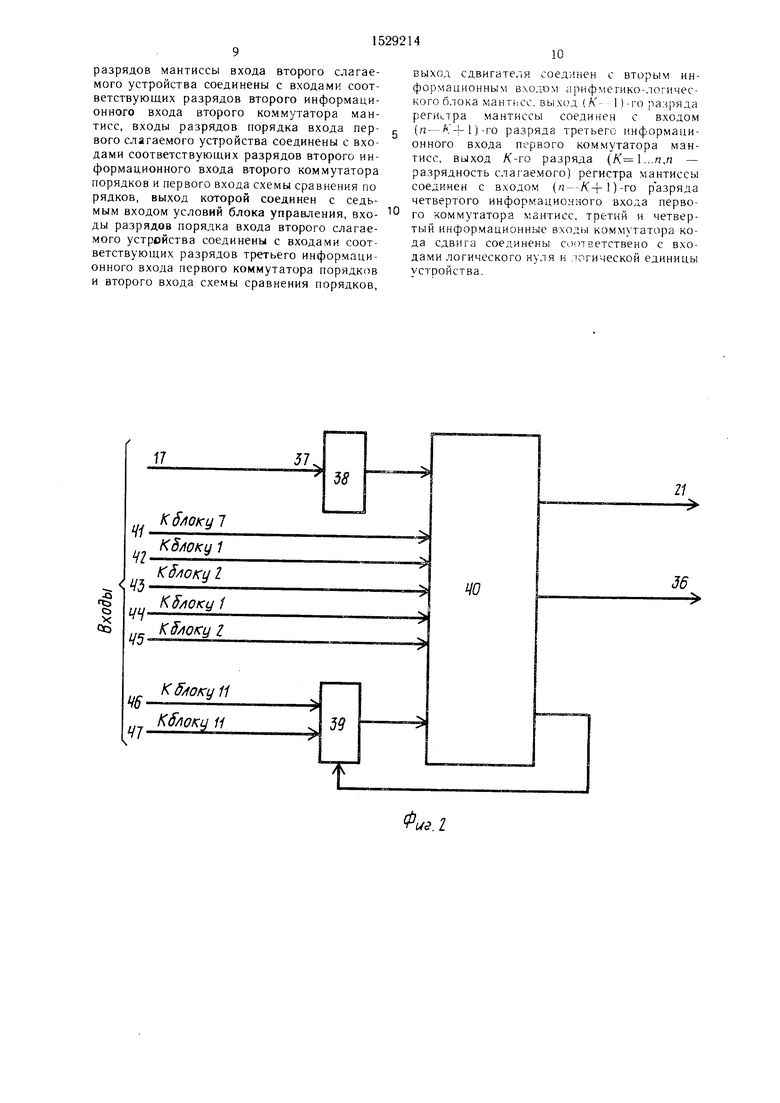

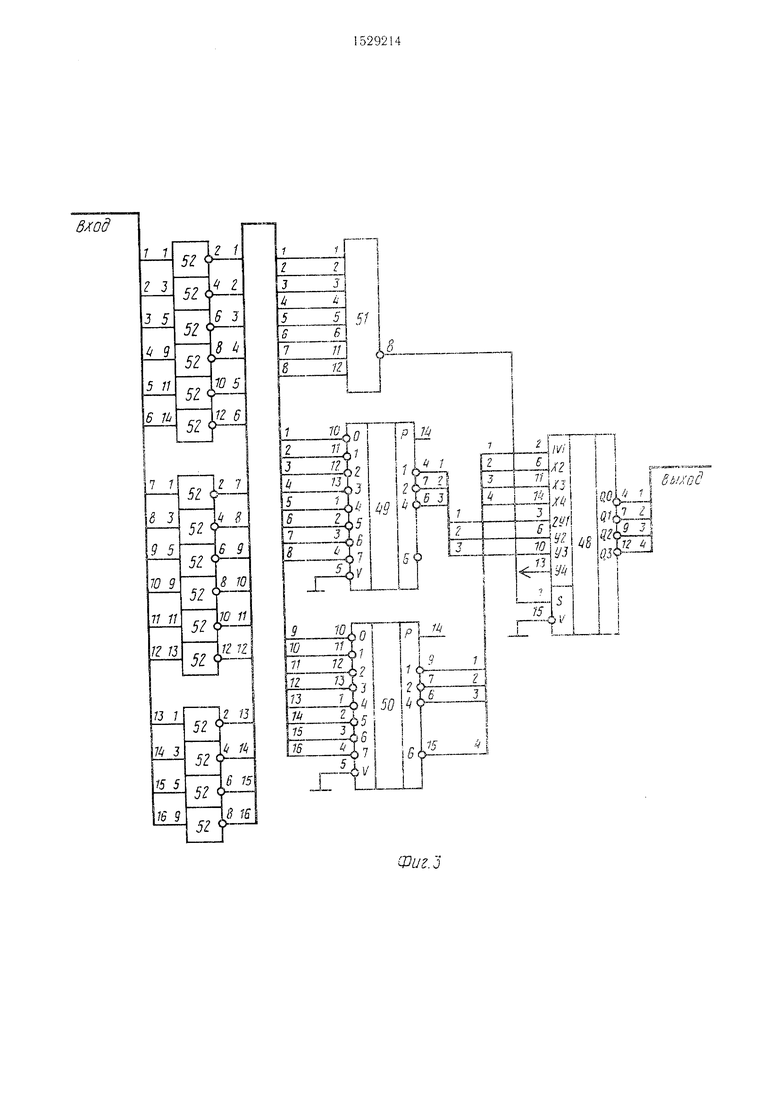

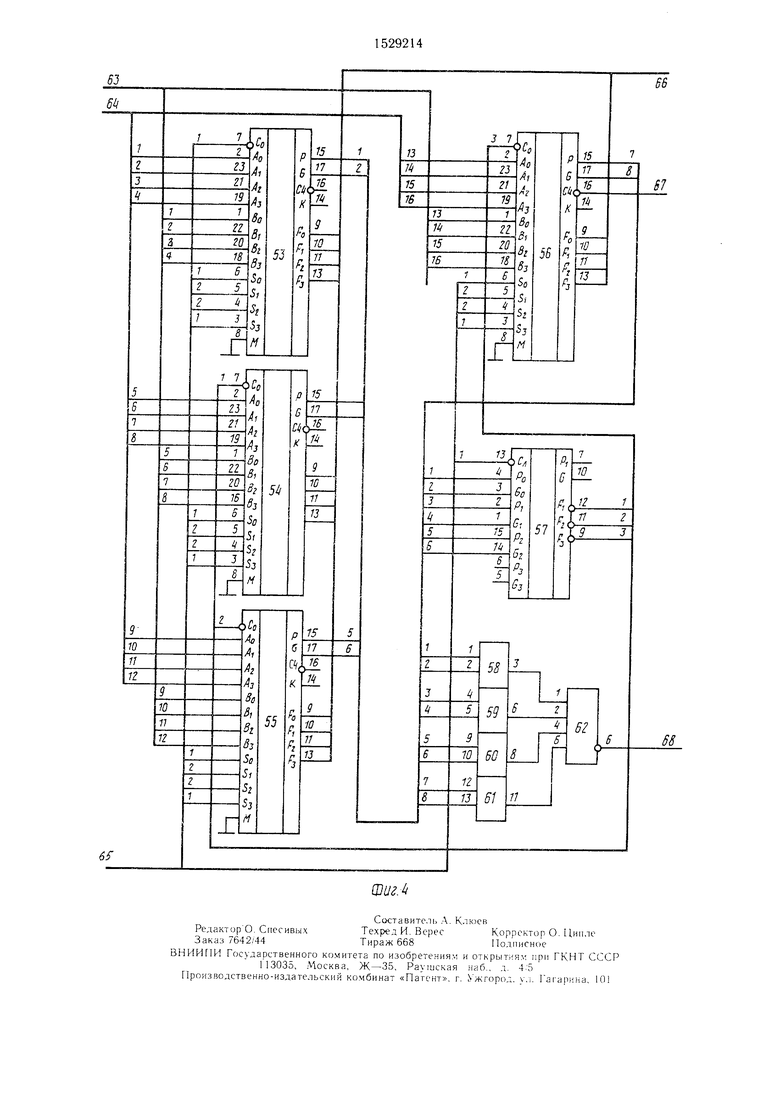

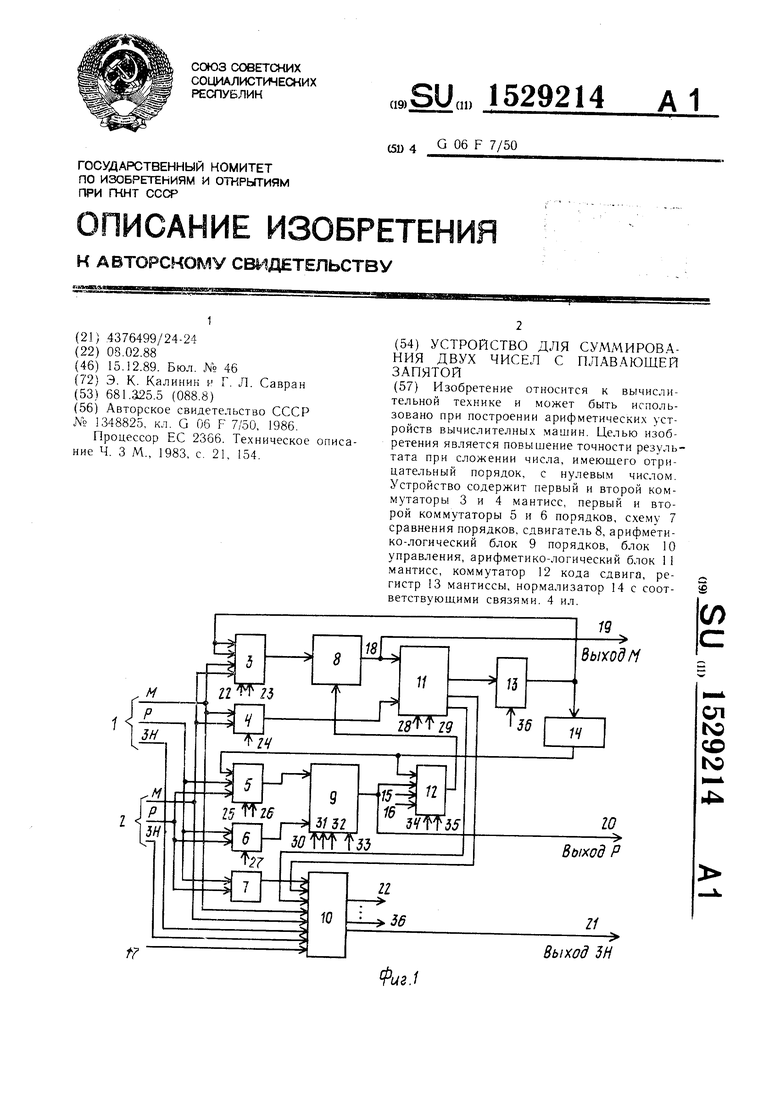

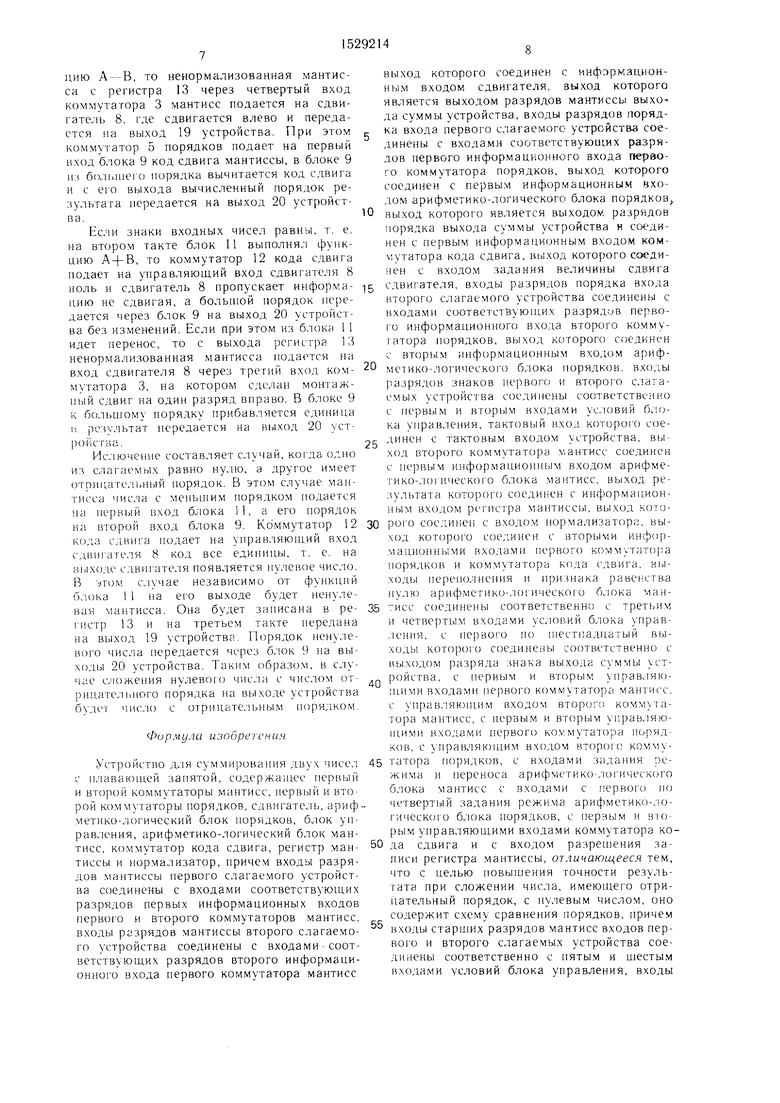

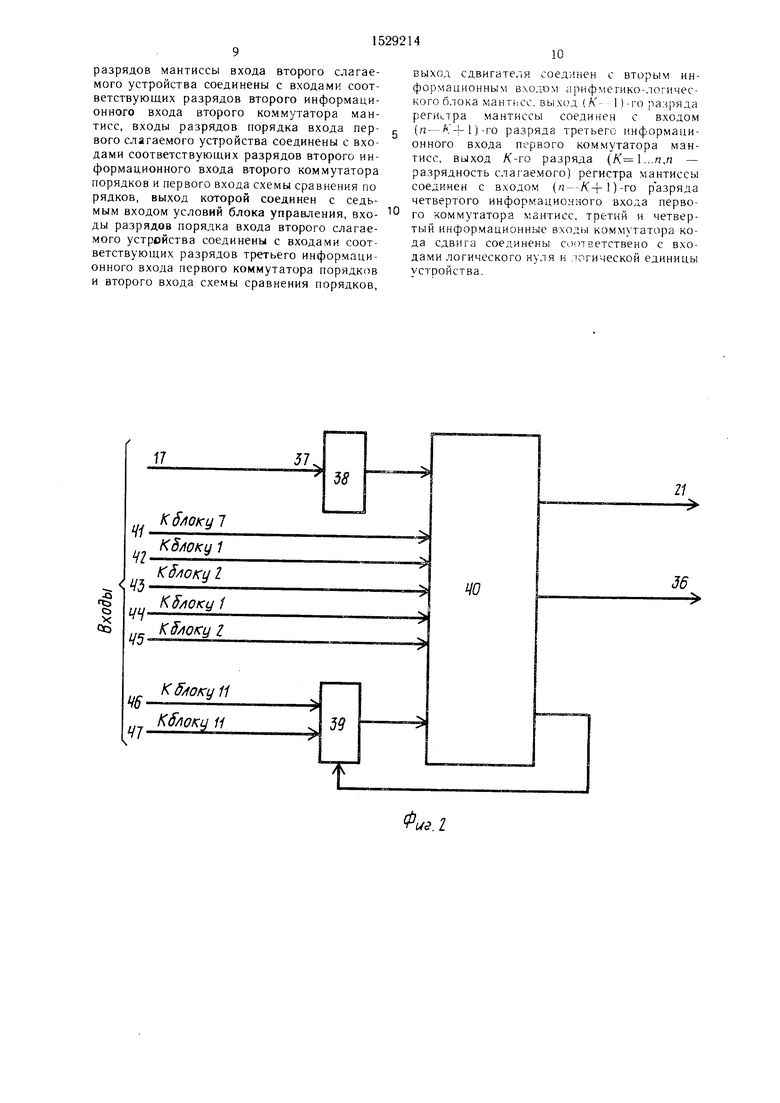

На фи1 1 представлена структурная схема устройства для суммирования двух чисел с плавающей запятой; на фиг. 2 структурная схема блока управления; на фиг. 3 - - функциональная схема но)1а- лизатора; на фиг. 4 - функциональная схема арифметико-логического блока ман- тисе.

Устройство (фиг. 1) содержит вход 1 первого слагаемого устройства, вход 2 второго- слагаемого устройства, первый и второй коммутаторы 3, 4 мантисс, первый и второй коммутаторы 5, 6 порядков, схему 7 сравнения порядков, сдвигатель8, арифметико-логический блок 9 порядков, блок 10 управления, арифметико-логический блок 11 мантисс, коммутатор 12 кода сдвига, регистр 13 мантиссы, нормализатор 14, вход 15 логического нуля устройства, вход 16 логической единицы устройства, тактовый вход 17 устройст(а. выход 18 сдвигателя 8, выход 19 разрядов мантиссы выхода суммы устройства, выход 20 разрядов порядка выхода суммы устоойства, выход 21 разряда знака В1)1хода суммы устройства, с второго по шестнадцать ;i вьгходь 22-36 блока 10 угфав- лення.

Б. юк Ш унравления (фиг. 2) соде(- жнт вход младшего разряда регистра 38 сдвш а, регистр 39, дешифратор 40, входи 41--47 условий блока И) управления, причем вход 17 устройства соединен с входом 37 регистра 38, выход которого, входы 41--45 блока 10 управления и выход е- гистра 39 соединены соответственно с вхо- дами дешифратора 40, выходы которого соединены соответственно с выходом 21 устройства, с выходами 22--36 блока унравления и с в.чодом разрешения регие-тра 39, входы разрядов которого соединены с входами 46, 47 блока 10 управления.

Нормализатор 14 (фиг. 3) для шестнадцатиразрядной мантиссы содержит коммутатор 48, первый и второй шифраторы 49, 50, элемент И - НЕ 51 и rpynriy элементов НЕ 52, причем входы разрядов входа нормализатора 14 соединены с входами соот- ветствующих элементов НЕ 52, выходы с нер- вого но восьмой элементов НЕ 52 соединены с соответствующими входами элемента И-НЕ 51 и шифратора 49, выходы элементов НЕ 52 с девятого по шестнадцатый соединены соответственно с входами шифратора 50, ВЬЕХОДЫ которого соединены с первой группой информационных входов коммутатора 48, выход которого является

0 с о

5 , 5

0

5

выхг)дом нор.мализатора 14, выходы шифратора 49 и выход -Jлeмeнтa И- -НЕ 51 соединены соответствен; 10 с второй гругтой информационных входов и с управляющим входом коммутатора 48. В качестве элементов НН использованы ИС 531 ЛН1. элемента И- НЕ -- ИС 531 ЛА2, шифраторов -- ИС;55 ИВ1, коммутатора - - ИС 53S КНИ. Арифметико-логический блок i 1 (фиг. 4) содержит арифметико-логические элементы 53-55, элемент 57 ускоренного нереноса, элементы 58--61 ИСКЛЮЧАЮЩЕЕ ИЛИ, или элемент 62. информационные входы 63, 64 блока 11, входы 65 задания режима и переноса блока 11, выход 66 результата б;1ока 11, выходы 67, 68 нереполнения и признака равенства ну:1Ю б. Юка 11, причем входы разрядов первого и второго информап,ион1 ;ых входов 63, 64 блока 1 соединены - входами разрядов и второго информационных входов элементов 53--56, входы задания режима которых соеди)(ены с входом 65 блока 11, выходы разрядов элементов 53 - 56 яв.пяются выходом 66 резу;1ьта1а 1 1, вход 65 которого и выходы ус.товий зозпнк- новения (G) и расгфост1)анения (Р) переноса элементов 53--- 56 соединены соответственно с входами э:1емента 57 vcKopeiMioro ;ie- JCHOca, выходы которого соединеш) с кхо- дами переноса элементов 54 5(5 соответственно, вход п.ереноса э.пе.мен.та 53 сг;еди- с входом 65 блока 1, выход 67 ;:ере- нолнения которого соединен с )До.м Hepefioca элемента 56, выходы vc;ior.iui i()3- никповен1 я и распространения i(s)eHoca элемента 53- 56 соединены соответственно с первыми и вторыми входами э. 1ементо15 58 61 ИСКЛЮЧАЮЩЕЕ И,ПИ, выходы которых соединены с соответствуюпАими входами; элемента И----НЕ 62, выход ;чоторого является выходом 68 признака равенства блока П.

Элементы 53-56 .лн. на ИС, 531 ИНЗ, элемент 57 - на HC53i ИГ14, элементы ИСКЛЮЧАЮЩИЕ ИЛИ - ;.ia И С 531 JH15, элемент И НЕ }га ИС 531 ,.

Блок управления (()И1. 2) pea. uriOiiai-. а налоги о известной совокупности ун- рав.1ения. Дешифрато ;| 40 может быть реа- ,лизован посредством ИЗУ, которое схлужит для того, чтобы на основании анализа кода номера текущего такта, результата сравнения мантисс, результата сравнения порядков, знаков входных чисел и стар- 1ИИХ разрядов мантисс входных чисел сформировать знак результата числа на выходе устройства, а также подать управляющие сигналы на блоки устройства. Таким образом, чтобы закодировать НЗУ дешифратора 40, необходимо для всех возможных состояний его входов определить с помощью описания потактовой работы стройства, приведенного далее, необходимые состояния выходов.

Блок 10 управления раб.отает следующим образом. При поступлении тактовых сигналов на вход 17 устройства в младший разряд регистра 38 (сдвига) записывается «1 и на каждом гюследующем такте сдвигается. На выходе регистра 38 образуется позиционный кол номера текущего такта, который подается на дешифратор 40. Дешифратор 40 анализирует этот код, ре- зультат на выходе схемы 7 сравнения, знаки вход(ых чисел, старшие разряды мантисс входных чисел, выход регистра 39 и вырабатывает управляющие сигналь; на выходах 22 - 36. Кроме того, он определи- ет знак результата. Следует отметить, что старшие разряды .ма нтисс вместе со зпа- ками порядков ;одаются на входы блока 10, что позволяет 11ро:-1:)3одкть анализ случая равенства одь()г() Hj слагаемых НУЛЮ ирн стр(1 дательном порядке другого слагаемого. Анализ производится в дешифраторе 40.

Нормализатор 14 (фиг. 3) работает сле- дуюпхим образом. На элементе определяется наличие хотя бы одной единицы ь старших восьми разрядах мантиссы. При ее наличии коммутатор 48 передает на выход код с шифратора 49. в противном случае - с шифратора 50. Арифметико-логический блок 11 мантисс (фиг. 4) работает следующим образом. Использована следующая зависимость состояний выходов ускоренного переноса от входных чисел при операции А-- В. Есл.ь. то Р «Ь и т. е. отсутствуют условия как распространения, так и возникновения переноса, при Р 0 и G 0 присутствуют оба эти условия, при , G «l, т. е. имеются условия распространения переноса, а хт.ювие возникновения переноса отсутствует. Таким образо.м в с. тучае равенства входных чисел значения выходов Р и G будут различны. в двух друг их случаях они будут равны. Для определения неравенства значений Р и G они гк.)дключе1:ы к входам элементов ИСКЛЮЧАЮ ШКН ИЛИ 58--61. Единица на выходе из этих э.1ементов означает, что на входе соответствующего ариф- .метико-логического эле.мента поданы одина- ковые числа. Если на выходах всех элементов 5861 бу-дут единицы, то на выходе

элемента появится нуль-признак равенства результата нулю.

Устройство (фиг. 1) обрабатывает операнды, имеющие следующее представление. Под знако.м операнда понимается знак мантиссы. Старший разряд мантиссы (явная единица) всегда равен единице за исключением случая, когда операнд равен нулю. Отрицательная .мантисеа представляется в прямом коде. Старший разряд порядка яв- ляется знаком порядка. Отрицательный порядок представляется в дополнительном коде. Перед началом вычислений операнды

/етанавливаются па входах 1,2 ycrpoiiCTBa. Зат ем на вход 7 устройства подаются тактовые импульсы. Вь1чмсление с.п:ы зан1; /|а- ет три такта. На первом такте 1н-пв 1Й коммутатор 3 мантисс по сигналам с выходов 22 и 23 блока 10 подает м.игтнссу первого числа на информацко1 1-:ый ьх. сдвигателя 8. Второй коммутатор 4 ма1ггисс по.дает мантиссу в т орого чис.а на irropoi -i вход блока 11. Блок К) сигналами с выходов 34, 35 через коммутатор 12 кода сдви- гз подает на сдаигател - 8 нулевой; ло.: сдвига, т. е. на входах (З -ока 11 : 11есдви;-|утые мантисс). Си, первом гакто блок 10 с ;гналами с выходов 28, 29 задает блоку П функции А- Б к он работает в качестве компаратора мантисс. Резу. а-гат сравнения мантисс определяется :ь 1 нал. переполнения блока И и равенству рсзу.1ь- тат;1 вычитания HV.TK) и за1;оми1 астся з б;и.; ке 10 Г:павления. На этом же тахте блок 0 а 1ализируег результат сравне ; я iu )ps;, на схеме 7 еравнениь и вырабатьп ает такие л1равляюп1ие си1 на. 1ы кз .выходах 25 27 на ,ры 5, 6 порядков, что коммутатор 5 подг ет на первый вхсу б.юч ; 9. меньший порядок, а коммутатор 6 на ито- рой вход блока 9 - бо.лыпий поря;и)к. 5,ток 9 выпол: -;яет ф 11кцию А-В т. е. из больше|-о порядка вычитается меньший, ii; . в: ором такте коммутатор 3 маптисс по си: - налам е выходов блока 10 22, 23 подает на сдвигатель 8 мантисс чис,1а с меньшим порядком или, если порядки равны, с меньшей мантисеой. Коммутатор 4 мантисс подает :.iaHTffcc- - друг()О числа на вход блока 11. Разность порядков с выхода блока 9 через коммутатор 12 код;; сдвига подается на в.ход задан1-:я гдв1-:га сдвигателя 8. Сдви| атсль 8 сдвигает ман- вправо, несдвин тая i N an- тиссы складываются, ec,iii , входных чисел )вы. или вычитаются в против- - ном н: блоке 11. По:;ученная па его выходе ненор.м ;;.;изов; иная мантисса загпк ывается в pei iicTp 13. Ко 1 татс Ы и блок 9 остаются ; тол- по/южении. что и на первом такте.

На третье.м такте нормал1 ;затор 14 определяет, па CKO. ibKO надо сдви1;уть HCt-iop- мализованпую мант1 Ссу в.чево, - .тобы в ста|1- п;ем разряде был;; единица. Через коммутатор 12 код сдвига с выхода нор чп- лизатора подается на сдвигатель 8. Так сдвигатель 8 сдвигает впразо, а npi; нормализации маптисс надо сдвигать влево. т( в жгутах, соединяющих выход регистра 13 е третьи:м и четвертым входами ко.ммуга- тора 3 мантисс и выход сдвигатс, 1Я 8 с выходом 19 разрядов мантиссы устройства, происходит монтажное lUiN eneinie формата, стари1ие и младп1ие разряды по.мепяны местами. Если знаки входных чисел раз.-имс, т. е. ,на втором такте блок I 1 выполня, ф нкцию А--В, то ненормализованная мантисса с регистра 13 через четвертый вход коммутатора 3 мантисс подается на сдви- гатель 8, где сдвигается влево и передастся на выход 19 устройства. При этом коммутатор 5 порядков подает на первый вход блока 9 код сдвига мантиссы, в блоке 9 из большего иорядка вычитается код сдвига и с его выхода вычисленный порядок результата передается на выход 20 устройства.

Если знаки входных чисел равны, т. е. на втором такте блок 11 выполнял функцию А + В, то коммутатор 12 кода сдвпга подает на управляющий вход сдвигателя 8 ноль и сдвигатель 8 пропускает информацию не сдвигая, а больпюй порядок передается через блок 9 на выход 20 устройства без изменений. Если при этом из блока 1 1 ид«т перенос, то с выхода регистра 13 ненормализованная мантисса подается на вход сдвигателя 8 через третий вход коммутатора 3, на котором сделан монтажный сдвиг па один разряд вправо. В блоке 9 к большому порядку прибавляется едипица I результат передается на 20 устройства.

Ис;1Ючение составляет случай, когда одно из слагаемых равно нулю, а другое имеет отрпцате.тьный порядок, тисса числа с мепыпим на первый вход блока на второй вход блока ко.ча сдвига подает на сдвигателя 8 код все ньгчоде сдвнгателя появляется пулевое число. В с.лучае независимо от функций б. юка 1 1 на его выходе будет ненулевая мантисса. Она будет записана в ре- |-истр 13 и на третьем такте передана на выход 19 устройства. Порядок ненуле- Boi o числа передается через б.юк 9 на выходы 20 устройства. Таким образом, в случае сложения пулевог о пкма с числом от- рицате; ьного порядка на выходе устройства будет чис;1О с отрицательным порядком.

Формула изобретения

Устройство д,ля суммирова)ця двух чисе.1 с плавающей запятой, содержащее первый и второй коммутаторы маптисс, первый и второй коммутаторы порядков, сдвигатель, арифметико-логический блок порядков, блок управления, арифметико-логический блок мантисс, коммутатор кода сдвига, регистр мантиссы и нормализатор, причем входы разрядов маптиссы первого слагае.мого устройства соединены с входами соответствующих разрядов первых информационных входов первого и второго коммутаторов мантисс, входы разрядов мантиссы второго слагаемого устройства соединены с входами соответствующих разрядов второго информационного входа первого коммутатора мантисс

В этом случае май- порядком подается 11, а его порядок 9. Коммутатор 12 управляюпгий вход единицы, т. е. на

0

5

0

5

0

5

0

5

выход которого соединен с информационным входом сдвигателя, выход которого является выходом разрядов мантиссы выхо да суммы устройства, входы разрядов порядка входа первого слагаемого устройства соединены с входами соответствующих разрядов первого информационного входа первого коммутатора порядков, выход которого соединен с первым информационным входом арифметико-логического блока порядков, выход которого является выходом разрядов порядка выхода суммы устройства и сш ди- нен с тервым информационным входом коммутатора кода сдвига, выход которогосоеди- нен с входом задания величины сдвига сдвигателя, входы разрядов порядка входа второго слагаемого устройства соединены с входами соответствующих разрядов первого информационного входа второго коммутатора порядков, выход которого соединен е вторым информационным входом арифметико-логического блока порядков, входы )азрядов знаков первого и второго c.iara- емых устройства соединены соответственно с первым и вторым входами условий 6.:io- ка управления, тактовый вход которого соединен с тактовым входом устройства, выход второго коммутатора мантисс соединен с |ервым информационным входом арифме- тико-ло1 ическо1-о блока .мантисс, выход результата кото)ог о соеди1{ен с информационным входом регис ) ра мантисс, вьгход которого сосди11ен с входе)м нормализатора, выход которого соединен с вторыми инфор- MaiuioHHbiMH вхс:)дами первого KOMMVTaTC)|)a порядк(и и коммутатора кода сдвига, выходы пере 1олнения и признака |)аве1-ства нулю арифметико-, 1О1 ическо| 0 блока тисс соединены соответственно с третьим и четве{)тым входами услов.ий блока управ- .ления, с первого по Н1ест1 адцатый выходы которого соединены соответственно с выходом разряда знака выхода устройства, с первым и вторым управляющими входами первого коммутатора мантисс, с управляк)П1ИМ входом второго тора мантисс, с первым и вторым управляющими входа.ми первого ко мутато;)а п(;ряд- ков, с управляющим входом второго коммутатора порядков, с входами задапия ое- жима и переноса арифметико-.логического блока маптисс с входами с .червог о по четвертый задания режима арифметико-.ю- гического блока порядков, с первым и вло- рым управляюп,ими входами коммутатора кода сдвига и с входом разрешения записи регистра мантиссы, отличающееся тем, что с целью повыщения точноети результата при сложении числа, имеюпаего отрицательный порядок, е пулевым числом, оно содержит схему сравнения порядков, причем входы старших разрядов мантисс входов первого и второго слагае.мых устройства соединены соответственно с пятым и шестым входами условий блока управления, входы

разрядов мантиссы входа второго слагаемого устройства соединены с входами соответствующих разрядов второго информационного входа второго коммутатора мантисс, входы разрядов порядка входа первого слагаемого устройства соединены с входами соответствующих разрядов второго информационного входа второго коммутатора порядков и первого входа схемы сравнения по рядков, выход которой соединен с седьмым входом условий блока управления, входы разрядов порядка входа второго слагаемого устройства соединены с входами соответствующих разрядов третьего информационного входа первого коммутатора порядков и второго входа схемы сравнения порядков.

выход сдвигателя соединен с вторым информационным входом арифмегико-логичес- кого блока мантисс, вы.с)д (А - - 1 )-го разряда регистра мантиссы соединен с входом (п-А -|-1)-го разряда третьего информационного входа первого коммутатора мантисс, выход /(-го разряда (/(...«,« - разрядность слагаемого) регистра мантиссы соединен с входом (п-/С+П-го р азряда четвертого информационного входа первого коммутатора мантисс, третий и четвертый информационные входы коммутатора кода сдвига соединены соответствено с входами логического нуля и логической единицы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционное устройство | 1985 |

|

SU1367012A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1290300A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин. Целью изобретения является повышение точности результата при сложении числа, имеющего отрицательный порядок, с нулевым числом. Устройство содержит первый и второй коммутаторы 3 и 4 мантисс, первый и второй коммутаторы 5 и 6 порядков, схему 7 сравнения порядков, сдвигатель 8, арифметико-логический блок 9 порядков, блок 10 управления, арифметико-логический блок 11 мантисс, коммутатор 12 кода сдвига, регистр 13 мантиссы, нормализатор 14 с соответствующими связями. 4 ил.

и.2

JLj

Фиг. 2

| Устройство для суммирования чисел с плавающей запятой | 1986 |

|

SU1348825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бетонный полый камень | 1925 |

|

SU2366A1 |

| Техническое описание Ч | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1989-12-15—Публикация

1988-02-08—Подача