Изобретение относится к вычислительной технике и может быть использовано в многоканальных (многопроцессорных) вычислительных системах при формировании временных диаграмм переключения и управления устройствами в каналах.

Целью изобретения является повышение достоверности работы устройства.

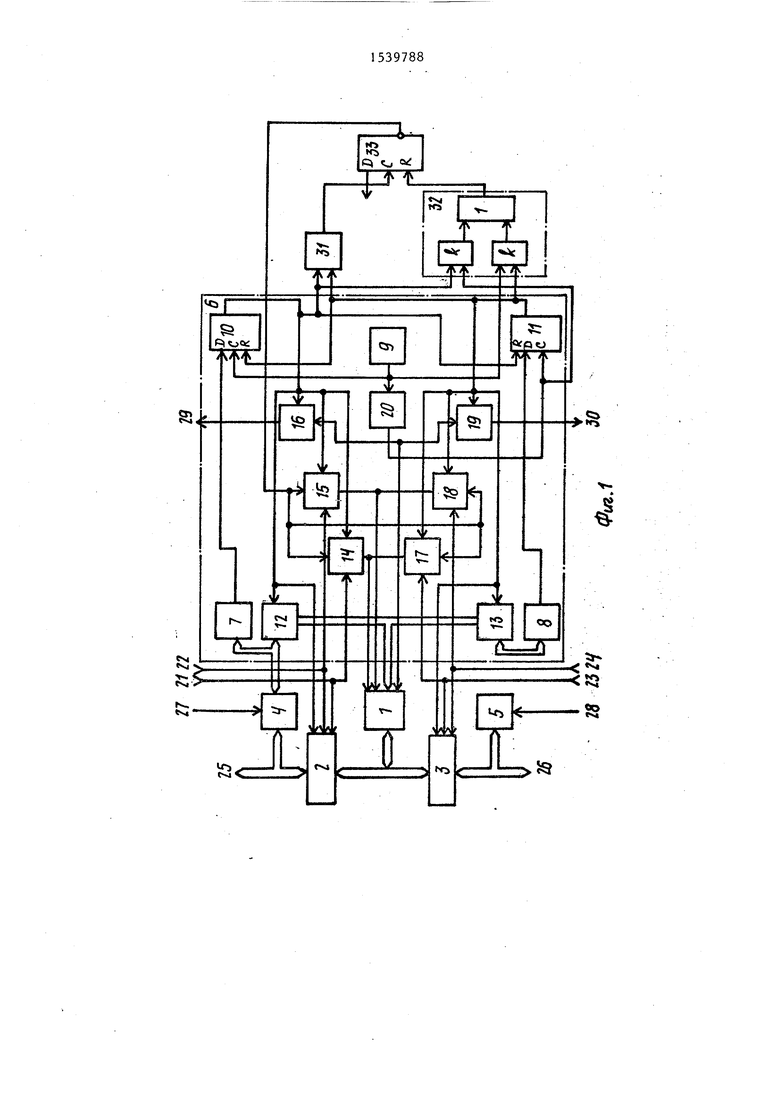

На фиг. 1 приведена блок-схема предлагаемого устрфйства; на фиг. 2 - временные диаграммы его работы.

Устройство содержит (фиг. 1) блок 1 памяти, коммутаторы 2 и 3 магистралей, регистры 4 и 5 адреса, блок 6 коммутаторов, состоящий из дешифраторов 7 и 8 зоны, генератора 9 импульсов, триггеров 10 и 11, элементов И 12 и 13 первой и второй групп, первого 14, третьего 15, пятого 16, второго 17, четвертого 18 и шестого 19 элементов И и элемента НЕ 20, шины 21, 22 и 23, 24 чтения и записи первой и второй магистралей, информационно-адресные шины 25 и 26, шины 27 и 28 управления обменом и шины 29 и 30 синхронизации ответа первой и второй магистралей, элемент ИЛИ 31, элемент И-ИЛИ 32 и триггер 33.

Устройство работает следующим образом.

В регистры- 4 и 5 по фронтам импульсов Обмен на шинах 27 и 28 заносятся коды адресов с шин 25 и 26, При появлении адреса, совпадающего с зоной адресов блока 1 памяти, дешифраторы 7 и 8 зоны выдают сигналы, которые удерживаются на информационных входах триггеров 10 и II до тех пор, пока не изменится содержимое регистров 4 и 5. Всегда срабатывает только один из триггеров 10 и И, так как на их син- хровходы сигналы генератора 9 подаются инверсно благодаря элементу НЕ 20, Например, при срабатывании триггер.а

сл

со со

00 00

1Ч)

10 на вход сброса триггера 11, поступает сигнал блокирующего сброса, запрещающий срабатывание триггера 11 до момента, пока триггер 10 не будет установлен в исходное состояние, т.е. пока присутствует сигнал с дешифратор ра 7. После снятия этого сигнала триггер 10 очередным управляющим фронтом импульса от генератора 9 устанавлива- ется в исходное состояние и блокировка триггера И снимается.

В момент срабатывания одного из триггеров 10 и 11 открываются соответствующие коммутаторы 2 или 3. При этом направление передачи их определяется наличием одного из внешних сигналов Чтение или Запись. Эти внешние импульсы управляют режимом работы блока 1, т.е. в двунаправленной ма- гистрали либо появляется слово для записи в блок 1, либо слово читается из блока 1 и поступает на магистраль.

Адрес в блок 1 поступает через элемент И 12 или 13 с регистра 4 или 5 в зависимости от того, включен триггер 11.

Управляющие сигналы, определяющие режим работы блока 1 (Чтение или Запись), поступают через элемент И 14 или 15, 17- или 18. Элемент И 16 или 19 управляет поступлением на соответствующую шину 29 или 30 сигнала Синхронизация ответа из памяти, ко- торый несет информацию об окончании обращения к памяти.

При обращении к блоку 1 памяти сигналы с выходов триггеров 10 и 11 подаются на входы элемента ИЛИ 31, вы- ход которого подключен на синхровход триггера 33. При этом на информационный вход триггера 33 подан потенциал, соответствующий 1. Триггер 33 устанавливается по переднему фронту сиг- налов на его синхровходе от одного из триггеров 10 и 11. Одновременно они работать не могут.

Когда триггер 33 устанавливается, то на его инверсном выходе появляет- ся сигнал, запрещающий работу элементов И 14, 15, 17 и.18.

Вместе с тем соответствующие коммутаторы подключаются к совмещенной магистрали, с регистра 4 или 5 адреса через элемент И 12 или 13 подается адрес к блоку 1 памяти. Предположим, что вв-еден триггер 10. Тем не менее, хотя на первом входе первого элемента и элемента И-ИЛИ 32 имеется разрешающий потенциал, триггер 33 не сбрасывается до тех пор, пока не появится разрешающий синхросигнал на втором входе этого элемента И. Поэтому сигнал Чтение или Запись с элемента И 14 или 15 в блок 1 памяти не поступает, что позволяет установиться на информационных входах блока 1 памяти корректным сигналам..

При появлении сигнала на втором хвходе первого элемента И элемента 32 триггер 33 сбрасывается и сигнал Чтение или Запись поступает на вход блока 1 памяти. При этом осуществляется требуемый цикл обмена с памятью.

Аналогично работает устройство при одновременном запросе совмещенной магистрали от двух временных устройств (магистралей) , так как доступ получает вначале только одна из магистралей.

Ф -ор мула изобретения

Устройство для сопряжения двух магистралей по авт.св. № 1283781, о т- личающееся тем, что, с целью повышения достоверности работы устройства, в него введены третий триггер, элемент ИЛИ и элемени И-ИЛИ, причем первый и второй входы элемента ИЛИ подключены соответственно к выходам первого и второго триггеров, а выход - к синхровходу третьего триггера, входом сброса соединенного с выходом элемента И-ИЛИ, первый, второй, третий и четвертый входы которого подключены соответственно к выходу первого триггера, выходу элемента НЕ, выходу генератора импульсов и выходу второго триггера, выход третьего триггера соединен с третьими входами первого, второго, третьего и четвертого элементов И.

я ъ.

§ & Iе § ъ

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1522224A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1545225A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619286A1 |

| Устройство для сопряжения двух магистралей | 1985 |

|

SU1283781A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619285A1 |

| Устройство для сопряжения магистралей | 1990 |

|

SU1737460A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1575193A2 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для сопряжения двух магистралей | 1990 |

|

SU1778760A1 |

Изобретение относится к вычислительной технике, может быть использовано в многоканальных (многопроцессорных) системах для получения доступа к общему разделяемому ресурсу и является усовершенствованием известного устройства по авт.св.N1283781. Целью изобретения является повышение достоверности работы устройства. Цель достигается тем, что в устройство по авт.св.N1283781 введены элемент ИЛИ, третий триггер и элемент И-ИЛИ, которые формируют сигналы разрешения на предоставление доступа к совмещенному ресурсу и обеспечивают подачу управляющих сигналов "Запись", "Чтение" от выбранной магистрали на вход блока памяти только после установления корректных значений адреса и данных. 2 ил.

| Устройство для сопряжения двух магистралей | 1985 |

|

SU1283781A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1988-05-03—Подача