(Я

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1985 |

|

SU1298806A1 |

| Триггер на МДП-транзисторах | 1985 |

|

SU1330654A1 |

| Триггер на МДП-транзисторах | 1985 |

|

SU1330655A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Генератор импульсов | 1973 |

|

SU561293A1 |

| Генератор импульсов | 1975 |

|

SU570185A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

Изобретение относится к вычислительной технике и может быть использовано в регистрах сдвига на основе приборов с переносом. Целью изобретения является повышение быстродействия регистра сдвига. Поставленная цель достигается за счет введения усилительного транзистора 14 и форсирующего конденсатора 15, а в блок регенерации четвертого разрядного 13 и четвертого зарядного транзисторов 12. 2 ил.

:л

GO СО 00

Изобретение относится к вычислительной технике и может быть использовано в регистрах сдвига на основе приборов с переносом заряда.

Целью изобретения является повышение быстродействия регистра сдвига.

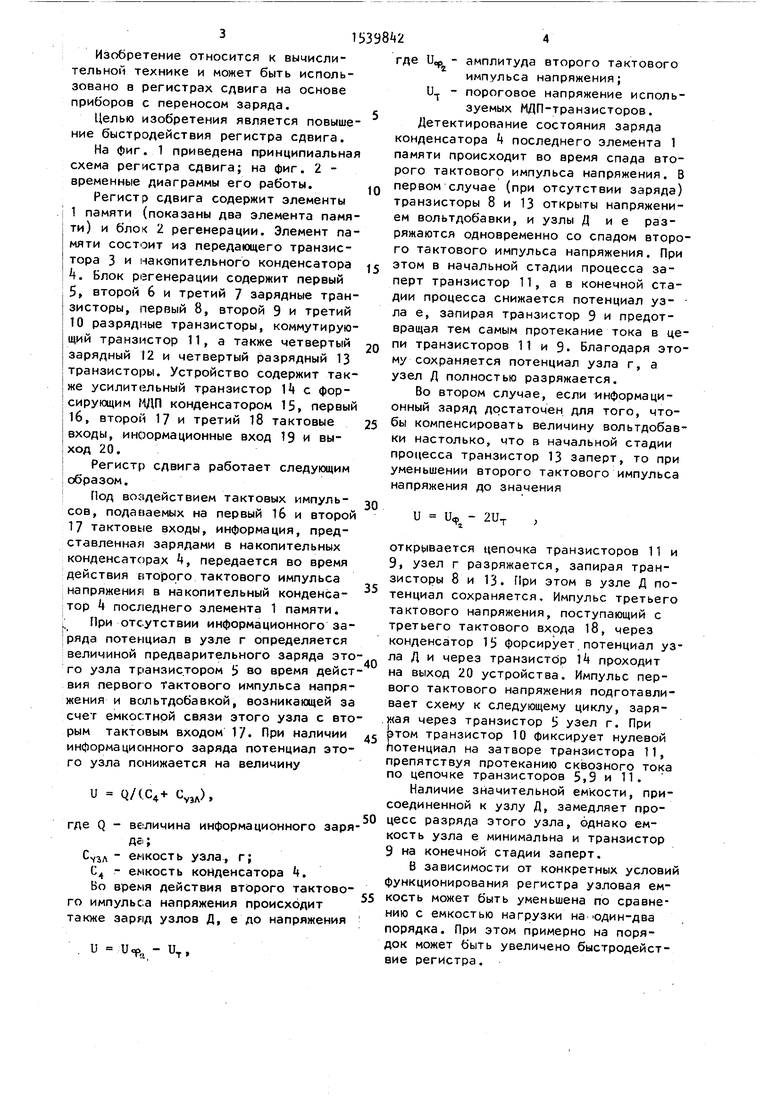

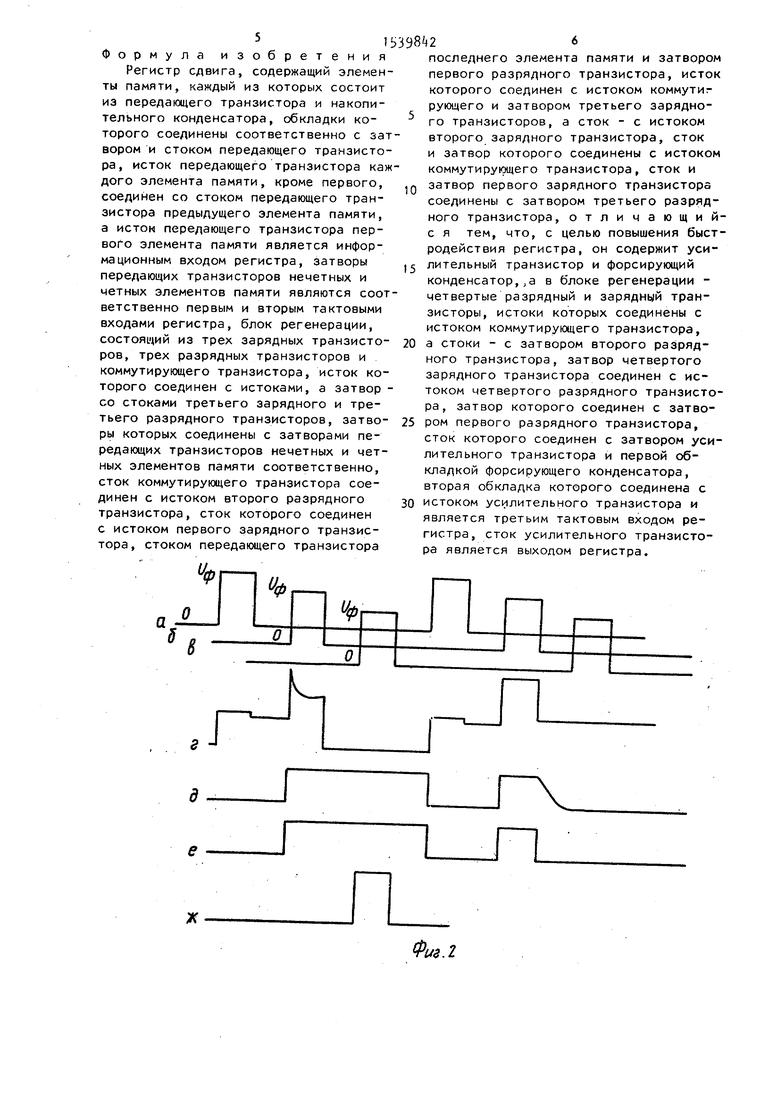

На фиг. 1 приведена принципиальная схема регистра сдвига; на фиг. 2 - временные диаграммы его работы.

Регистр сдвига содержит элементы 1 памяти (показаны два элемента памяти) и блок 2 регенерации. Элемент памяти состоит из передающего транзистора 3 и накопительного конденсатора Ц. Блок регенерации содержит первый 5, второй 6 и третий 7 зарядные транзисторы, первый 8, второй 9 и третий 10 разрядные транзисторы, коммутирующий транзистор 11, а также четвертый зарядный 12 и четвертый разрядный 13 транзисторы. Устройство содержит также усилительный транзистор 14 с форсирующим МДП конденсатором 15 первый 16, второй 17 и третий 18 тактовые входы, информационные вход 19 и выход 20.

Регистр сдвига работает следующим образом.

Иод воздействием тактовых импульсов, подаваемых на первый 16 и второй 17 тактовые входы, информация, представленная зарядами в накопительных конденсаторах 4, передается во время действия второго тактового импульса напряжения в накопительный конденсатор 4 последнего элемента 1 памяти.

При отсутствии информационного заряда потенциал в узле г определяется

где

чит 10

15

20

25

30

35

амплитуда второго тактовог импульса напряжения; пороговое напряжение испол зуемых МДП-транзисторов. Детектирование состояния заряда конденсатора k последнего элемента памяти происходит во время спада вт рого тактового импульса напряжения. первом случае (при отсутствии заряд транзисторы 8 и 13 открыты напряжен ем вольтдобавки, и узлы Д и е раз ряжаются одновременно со спадом вто го тактового импульса напряжения. П этом в начальной стадии процесса за перт транзистор 11, а в конечной ст дии процесса снижается потенциал уз ла е, запирая транзистор 9 и предот вращая тем самым протекание тока в пи транзисторов 11 и 9. Благодаря э му сохраняется потенциал узла г, а узел Д полностью разряжается.

Во втором случае, если информаци онный заряд достаточен для того, чт бы компенсировать величину вольтдоб ки настолько, что в начальной стади процесса транзистор 13 заперт, то п уменьшении второго тактового импуль напряжения до значения

U U«p - 2UT )

открывается цепочка транзисторов 11 9, узел г разряжается, запирая тран зисторы 8 и 13. При этом в узле Д по тенциал сохраняется. Импульс третье тактового напряжения, поступающий с третьего тактового входа 18, через конденсатор 15 форсирует.потенциал у

величиной предварительного заряда это- ла Д и через транзистор 14 проходит

го узла транзистором 5 во время действия первого тактового импульса напряжения и вольтдобавкой, возникающей за счет емкостной связи этого узла с вторым тактовым входом 17. При наличии информационного заряда потенциал этого узла понижается на величину

U Q/(C4+ CV3A),

на выход 20 устройства. Импульс пер вого тактового напряжения подготавли вает схему к следующему циклу, заря жая через транзистор 5 узел г. При

45 ртом транзистор 10 фиксирует нулевой потенциал на затворе транзистора 11 препятствуя протеканию сквозного ток по цепочке транзисторов 5,9 и 11.

Наличие значительной емкости, при соединенной к узлу Д, замедляет про

где Q - величина информационного заряда;

CV3A - емкость узла, г; С4 - емкость койденсатора 4. Во время действия второго тактового импульса напряжения происходит также заряд узлов Д, е до напряжения

и

и- - и.

т

539842

где

чит 10

15

20

25

30

35

амплитуда второго тактового импульса напряжения; пороговое напряжение используемых МДП-транзисторов. Детектирование состояния заряда конденсатора k последнего элемента 1 памяти происходит во время спада второго тактового импульса напряжения. В первом случае (при отсутствии заряда) транзисторы 8 и 13 открыты напряжением вольтдобавки, и узлы Д и е разряжаются одновременно со спадом второго тактового импульса напряжения. При этом в начальной стадии процесса заперт транзистор 11, а в конечной стадии процесса снижается потенциал узла е, запирая транзистор 9 и предотвращая тем самым протекание тока в цепи транзисторов 11 и 9. Благодаря этому сохраняется потенциал узла г, а узел Д полностью разряжается.

Во втором случае, если информационный заряд достаточен для того, чтобы компенсировать величину вольтдобав- ки настолько, что в начальной стадии процесса транзистор 13 заперт, то при уменьшении второго тактового импульса напряжения до значения

U U«p - 2UT )

открывается цепочка транзисторов 11 и 9, узел г разряжается, запирая транзисторы 8 и 13. При этом в узле Д потенциал сохраняется. Импульс третьего тактового напряжения, поступающий с третьего тактового входа 18, через конденсатор 15 форсирует.потенциал узна выход 20 устройства. Импульс первого тактового напряжения подготавливает схему к следующему циклу, заряжая через транзистор 5 узел г. При

5 ртом транзистор 10 фиксирует нулевой потенциал на затворе транзистора 11, препятствуя протеканию сквозного тока по цепочке транзисторов 5,9 и 11.

Наличие значительной емкости, присоединенной к узлу Д, замедляет про0 цесс разряда этого узла, однако емкость узла е минимальна и транзистор 9 на конечной стадии заперт.

В зависимости от конкретных условий функционирования регистра узловая ем5 кость может быть уменьшена по сравнению с емкостью нагрузки на один-два порядка. При этом примерно на порядок может быть увеличено быстродействие регистра.

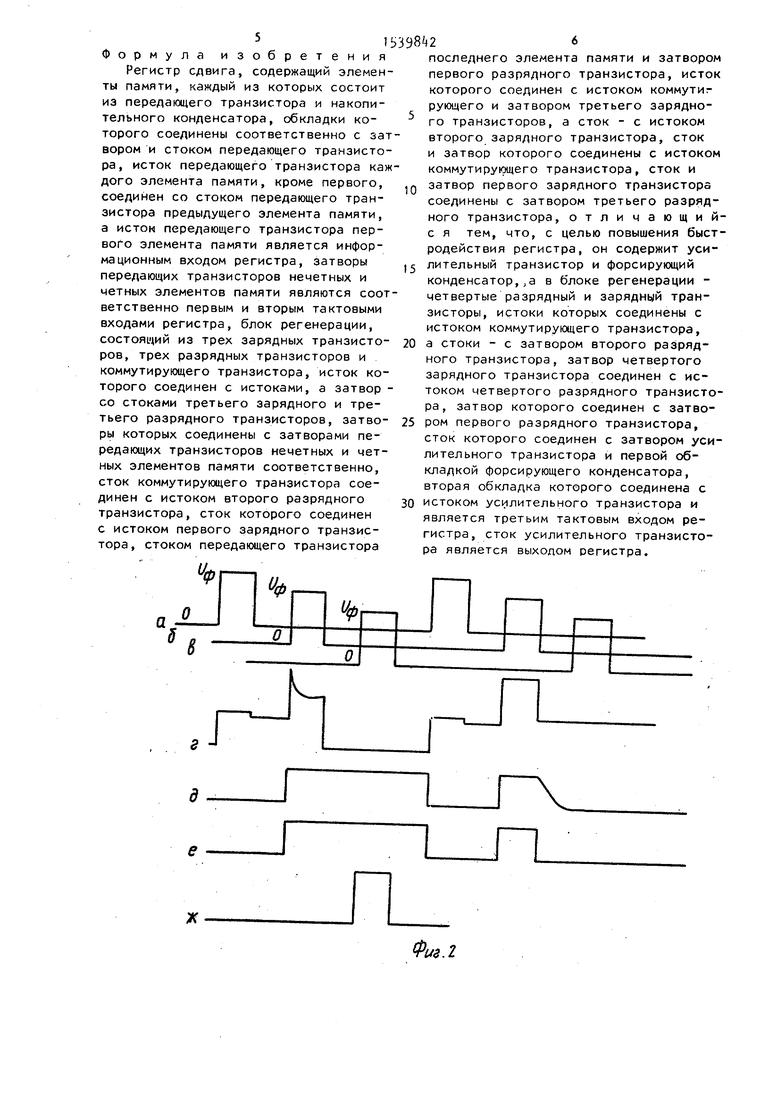

5 Формула изобретения

Регистр сдвига, содержащий элементы памяти, каждый из которых состоит из передающего транзистора и накопительного конденсатора, обкладки которого соединены соответственно с затвором и стоком передающего транзистора, исток передающего транзистора каждого элемента памяти, кроме первого, соединен со стоком передающего транзистора предыдущего элемента памяти, а истом передающего транзистора первого элемента памяти является информационным входом регистра, затворы передающих транзисторов нечетных и четных элементов памяти являются соответственно первым и вторым тактовыми входами регистра, блок регенерации, состоящий из трех зарядных транзисторов, трех разрядных транзисторов и коммутирующего транзистора, исток которого соединен с истоками, а затвор - со стоками третьего зарядного и третьего разрядного транзисторов, затворы которых соединены с затворами передающих транзисторов нечетных и четных элементов памяти соответственно, сток коммутирующего транзистора соединен с истоком второго разрядного транзистора, сток которого соединен с истоком первого зарядного транзистора, стоком передающего транзистора

1Ь

г

10

последнего элемента памяти и затвором первого разрядного транзистора, исток которого соединен с истоком коммутиг рующего и затвором третьего зарядного транзисторов, а сток - с истоком второго зарядного транзистора, сток и затвор которого соединены с истоком коммутирующего транзистора, сток и затвор первого зарядного транзистора соединены с затвором третьего разрядного транзистора, отличающий- с я тем, что, с целью повышения быстродействия регистра, он содержит уси15 лительный транзистор и форсирующий конденсатор,,а в блоке регенерации - четвертые разрядный и зарядный транзисторы, истоки которых соединены с истоком коммутирующего транзистора,

20 а стоки - с затвором второго разрядного транзистора, затвор четвертого зарядного транзистора соединен с истоком четвертого разрядного транзистора, затвор которого соединен с затво25 ром первого разрядного транзистора, сток которого соединен с затвором усилительного транзистора и первой обкладкой форсирующего конденсатора, вторая обкладка которого соединена с истоком усилительного транзистора и является третьим тактовым входом регистра, сток усилительного транзистора является выходом регистра.

30

| Патент США № 3582909, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Регистр сдвига | 1985 |

|

SU1298806A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-01-30—Публикация

1988-04-04—Подача