Изобретение относится к вычислительной технике и может быть использовано при проектировании регистров сдвига на основе приборов с переносом заряда.

Цель изобретения - уменьшение потребляемой мощности и упрощение регистра сдвига за счет уменьшения числа транзисторов и блоке регенерации и уменьщения числа тактовых входов регистра.

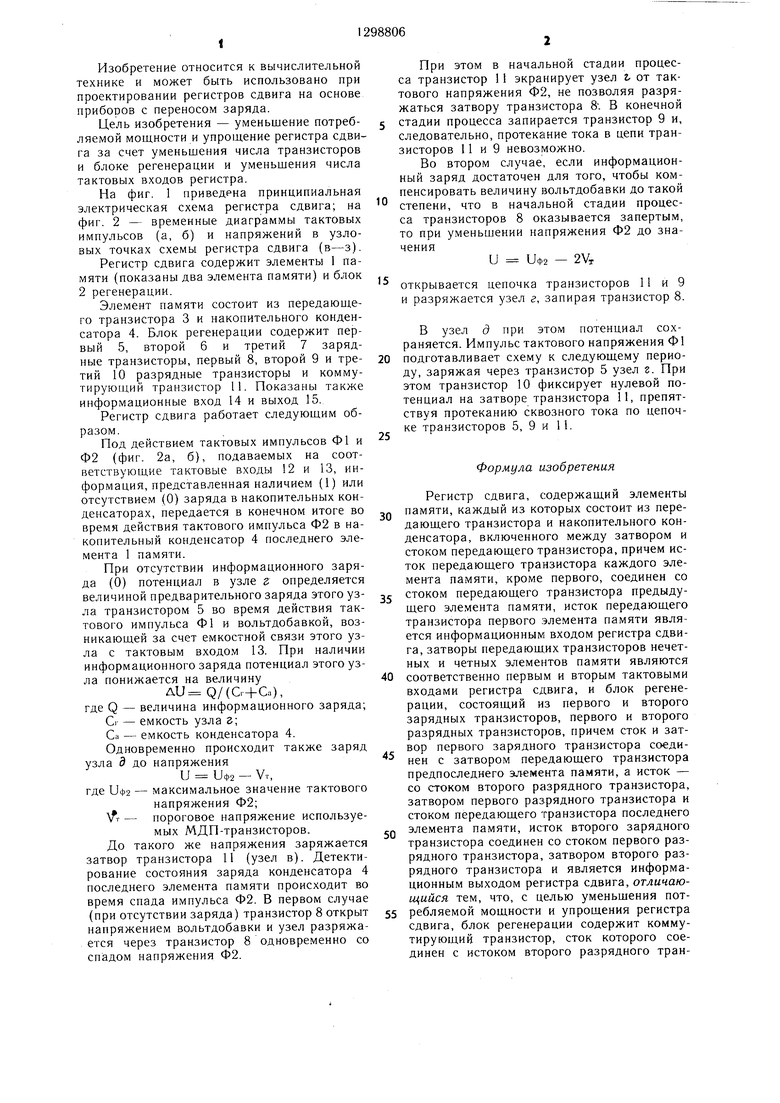

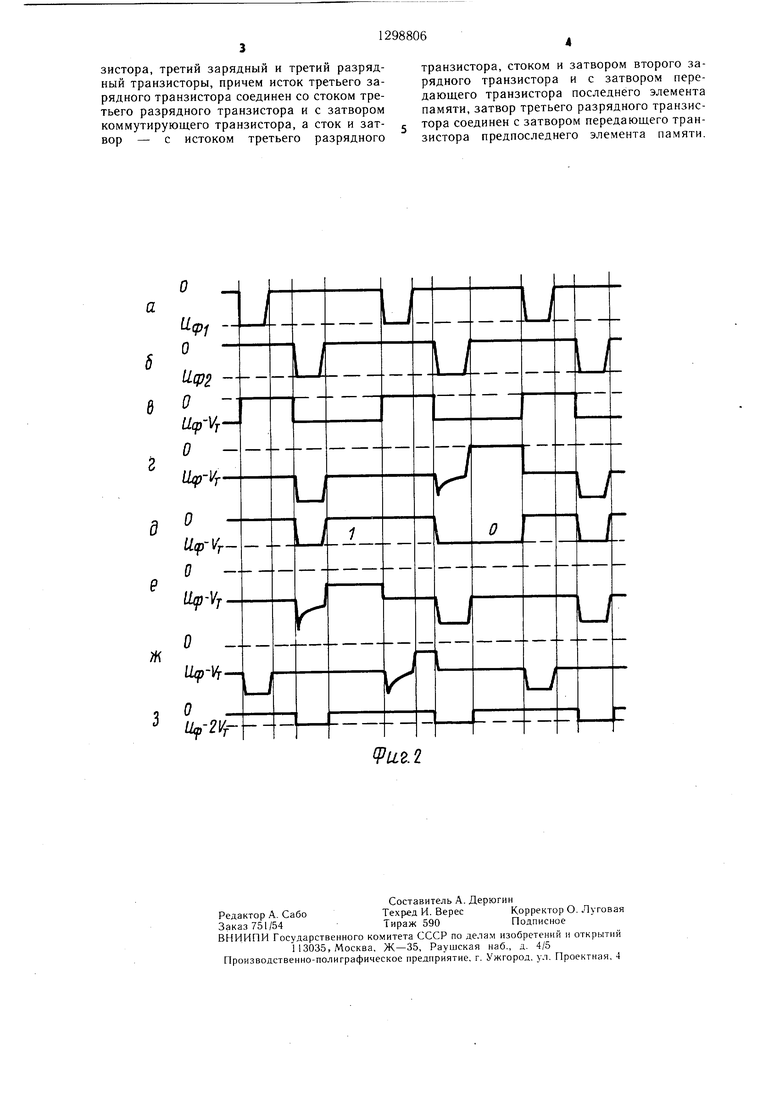

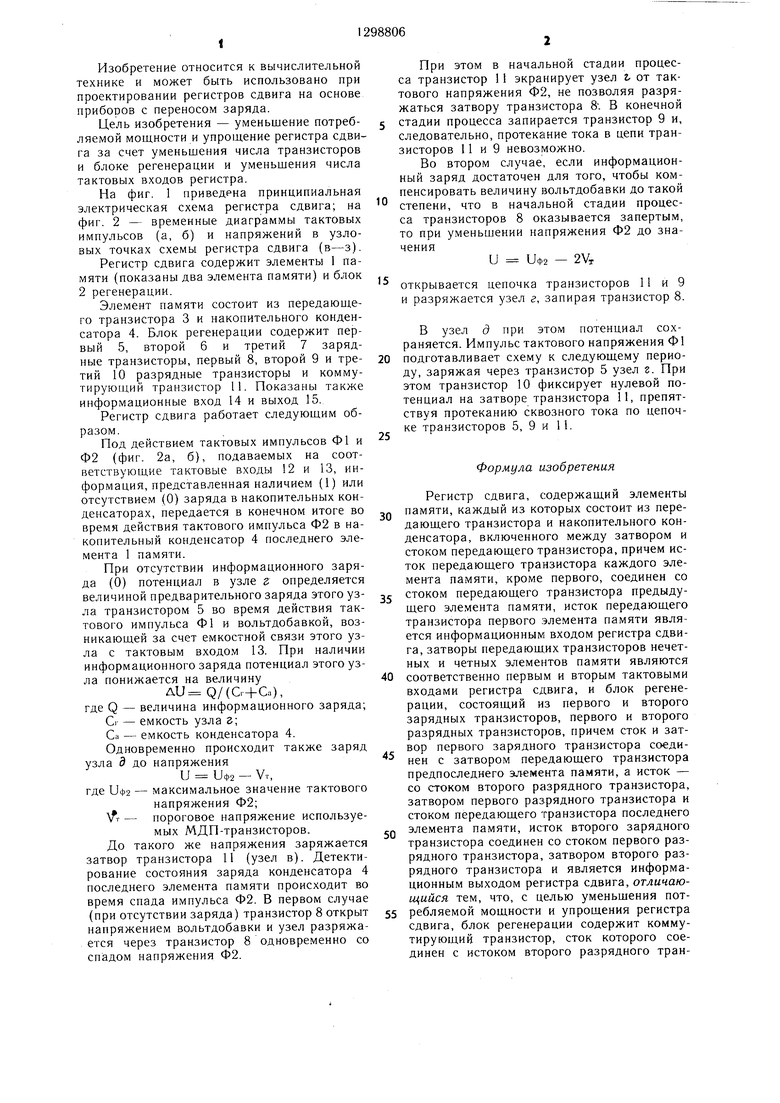

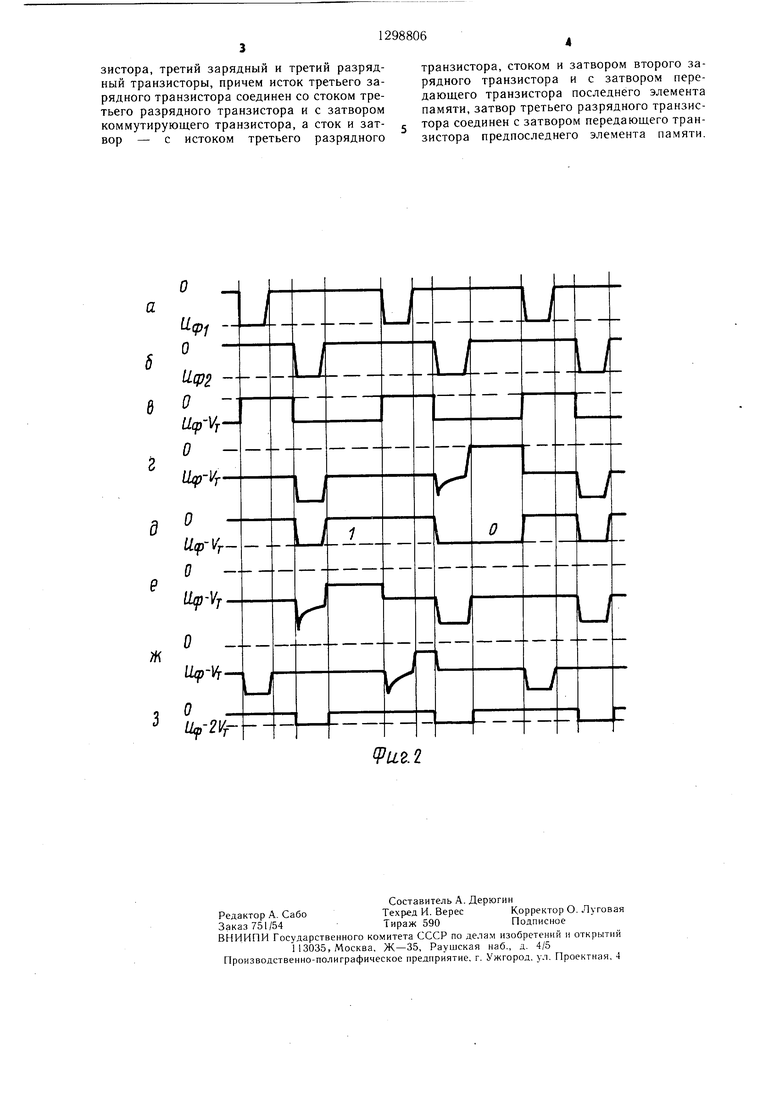

На фиг. 1 приведена принципиальная электрическая схема регистра сдвига; на фиг. 2 - временные диаграммы тактовых импульсов (а, б) и напряжений в узловых точках схемы регистра сдвига (в-з).

Регистр сдвига содержит элементы 1 памяти (показаны два элемента памяти) и блок 2 регенерации.

Элемент памяти состоит из передающего транзистора 3 и накопительного конденсатора 4. Блок регенерации содержит первый 5, второй 6 и третий 7 зарядные транзисторы, первый 8, второй 9 и третий 10 разрядные транзисторы и коммутирующий транзистор 11. Показаны также информационные вход 14 и выход 15.

Регистр сдвига работает следующим образом.

Под действием тактовых импульсов Ф1 и Ф2 (фиг. 2а, б), подаваемых на соответствующие тактовые входы 12 и 13, информация, представленная наличием (1) или отсутствием (0) заряда в накопительных конденсаторах, передается в конечном итоге во время действия тактового импульса Ф2 в накопительный конденсатор 4 последнего элемента 1 памяти.

При отсутствии информационного заряда (0) потенциал в узле г определяется величиной предварительного заряда этого узла транзистором 5 во время действия тактового импульса Ф1 и вольтдобавкой, возникающей за счет емкостной связи этого узла с тактовым входом 13. При наличии информационного заряда потенциал этого узла понижается на величину

ди Q/(G+Ca), где Q - величина информационного заряда;

Сг - емкость узла г;

Са - емкость конденсатора 4.

Одновременно происходит также заряд узла 9 до напряжения

и иф2 - VT,

где иФ2 - максимальное значение тактового напряжения Ф2;

fr - пороговое напряжение используемых МДП-транзисторов.

До такого же напряжения заряжается затвор транзистора 11 (узел в). Детектирование состояния заряда конденсатора 4 последнего элемента памяти происходит во время спада импульса Ф2. В первом случае (при отсутствии заряда) транзистор 8 открыт напряжением вольтдобавки и узел разряжается через транзистор 8 одновременно со спадом напряжения Ф2.

0

При этом в начальной стадии процесса транзистор 11 экранирует узел ь от тактового напряжения Ф2, не позволяя разряжаться затвору транзистора 8. В конечной стадии процесса запирается транзистор 9 и, следовательно, протекание тока в цепи транзисторов 11 и 9 невозможно.

Во втором случае, если информационный заряд достаточен для того, чтобы компенсировать величину иольтдобавки до такой степени, что в начальной стадии процесса транзисторов 8 оказывается запертым, то при уменьщении напряжения Ф2 до значения

и иф2 - 2Уг

открывается цепочка транзисторов 11 и 9 и разряжается узел г, запирая транзистор 8.

В узел д при этом потенциал сохраняется. Импульс тактового напряжения Ф1 0 подготавливает схему к следующему периоду, заряжая через транзистор 5 узел г. При этом транзистор 10 фиксирует нулевой потенциал на затворе транзистора 11, препятствуя протеканию сквозного тока по цепочке транзисторов 5, 9 и 11.

Формула изобретения

Регистр сдвига, содержащий элементы

Q памяти, каждый из которых состоит из передающего транзистора и накопительного конденсатора, включенного между затвором и стоком передающего транзистора, причем исток передающего транзистора каждого элемента памяти, кроме первого, соединен со

стоком передающего транзистора предыдущего элемента памяти, исток передающего транзистора первого элемента памяти является информационным входом регистра сдвига, затворы передающ,их транзисторов нечетных и четных элементов памяти являются

0 соответственно первым и вторым тактовыми входами регистра сдвига, и блок регенерации, состоящий из первого и второго зарядных транзисторов, первого и второго разрядных транзисторов, причем сток и затвор первого зарядного транзистора соединен с затвором передающего транзистора предпоследнего ал-емента памяти, а исток - со стоком второго разрядного транзистора, затвором первого разрядного транзистора и стоком передающего транзистора последнего

Q элемента памяти, исток второго зарядного транзистора соединен со стоком первого разрядного транзистора, затвором второго разрядного транзистора и является информационным выходом регистра сдвига, отличающийся тем, что, с целью уменьшения пот5 ребляемой мощности и упрощения регистра сдвига, блок регенерации содержит коммутирующий транзистор, сток которого соединен с истоком второго разрядного тран5

зистора, третий зарядный и третий разрядный транзисторы, причем исток третьего зарядного транзистора соединен со стоком третьего разрядного транзистора и с затвором коммутирующего транзистора, а сток и затвор - с истоком третьего разрядного

транзистора, стоком и затвором второго зарядного транзистора и с затвором передающего транзистора последнего элемента памяти, затвор третьего разрядного транзистора соединен с затвором передающего транзистора предпоследнего элемента памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1988 |

|

SU1539842A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Полупроводниковая линия задержки | 1974 |

|

SU527739A1 |

| Генератор импульсов | 1973 |

|

SU561293A1 |

| Формирователь импульсов регенерации для запоминающих устройств на мдп-транзисторах | 1974 |

|

SU500581A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании регистров сдвига на основе приборов с переносом заряда. Целью изобретения является уменьшение потребляемой мощности и упрощение регистра сдвига за счет уменьшения числа транзисторов в блоке регенерации и уменьшения числа тактовых входов регистра сдвига. Поставленная цель достигается тем, что блок регенерации содержит коммутирующий транзистор 11, третий зарядный 7 и первый разрядный 8 транзисторы. 2 ил. 00 00 о о Риг.1

а

ж

Уиг.г

| Запоминающий элемент | 1979 |

|

SU786741A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3979603, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1987-03-23—Публикация

1985-02-05—Подача