Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения делительной операции над числами, представленными в двоичной системе счисления с фиксированной точкой.

Цель изобретения - повышение быстродействия для случаев незначительных приращений аргументов.

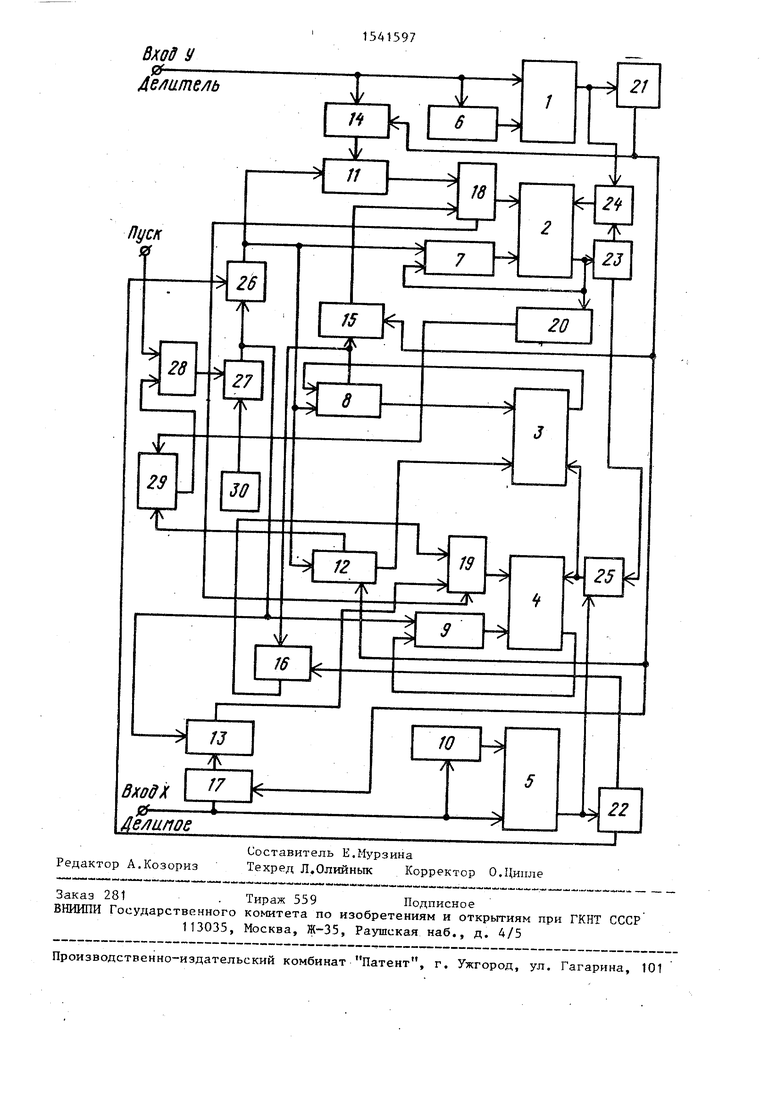

На чертеже представлена функциональная схема устройства для деления

Устройство для деления содержит пять сумматоров 1-5, регистр 6 текущего значения делителя, регистр 7 остатка, сдвигающий регистр 8 множителя, регистр 9 частного, регистр 10 текущего значения делимого, три сдвигающих регистра 11-13, четыре сдвигателя 14-17, два мультиплексора 18 и 19, дешифратор 20 определения нулевого кода, две схемы 21 и 22

поиска левой единицы, первый триггер 23, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24 и 25, два элемента И 26 и 27, второй триггер 28, элемент ИЛИ 29 и генератор 30 тактовых импульсов.

Устройство функционирует следующим образом.

Предположим, что в некоторый j.-мо- мент времени в регистрах 6 и 10 записаны делитель у- и делимое х-. Частное Ui и остаток X; , вычисленные устройством к j-му моменту времени, хранятся в регистрах 9 и 7. На информационные входы устройства поступают новые значения делителя у + , и делимого Xj+(, из которых в сумматорах 1 и 5 образуются разности (приращения)

СП Јь

N-A

сл со J

- i .i XJ

(1)

1+1 ° 3 15iV ti

Эти разности (|ДХА| 2 / ,д у,0 , где |t| 1 ,2,.. . ,п) из сумматоров 1 и 5 передаются для анализа в схемы 21

и 22 поиска левой единицы. Смысл анализа состоит в определении номера разряда fa в кодах разности Д xj, ду , в которых записана единица. Знаки разностей Л Xj , A yj через элементы ИСКЛЮЧАЮЩЕЕ 11ЛИ 24 и 25 соответственно определяют работу сумматоров 2 и 4 в подготовительном такте, определяющем канальные условия частичных остат- кои и частичного

U}+«,B -4yjWj ; , (2)

xi,,xi,n- +AxjW5 .

Для этого предыдущее значение общего множителя Wj , , хранящееся в регистре 8, передается со сдвигом на (4 у разрядов вправо через мульти - плексор 18 на вход сумматора 2 к на |ЫдХ разрядов вправо через мультиплексор 19 на вход сумматора 4 (что соот- ветствует умножению U; пн на Дх; и АУл ). Управление сдвигателями 15 и 16 осуществляется схемами 21 и 22 поиска левых единиц соответственно. Кр,оме того, значения делителя у , и дели- мого xj+, запоминаются в регистрах 6 и 10 и передаются через сдвигатели 14 и 17 со сдвигом на () разрядов вправо в сдвигающие регистры 11 и 13, а в сдвигающий регистр 12 загружает- ся 1 в ((Мду-З)-й разряд, что соответствует формированию начальных кон-

гтянт v , о-С + . 9-С1 °и

стант Xj /. , yit, и 2i( , где i(|M4y-3). С приходом управляющего сигнала Пуск в триг- гере 28 устанавливается .1, что открывает элемент И 27 и разрешает прохождение импульсов с генератора 30 на элементы устройства.

Таким образом происходит формиро- вание приращений сумматором 4 к ранее вычисленному (находящемуся в регистре 5) результату IL . , согласно выэ, п

ражению

Ui4«,,«4 +

Hi2

- ()

(3)

Причем знак первого приращения в j+1-м цикле определяется знаком у- ig хранимым в триггере 23, значение которого представляет собой закодированную величину q., и мультиплексоры 18 и 19 подключают к входам сумматоров 2 и 4 выходы сдвигающих регистров 11 и 13, хранящих yj + 1 и х, соответственно. При ixj 0 и д (во всех разрядах нупя) значение Uj, равно уже вычисленному значению U$ xj(n, и вычисления не производятся , зна

Q

5 0 5 n

,

Q

5

0

5

чение Uj+ быстро корректируется по выражению (2) за время подготовительного такта, при производится только (п-р+3) итераций для определения Uj-4, и устройство функционирует аналогично известнрму устройству, отличаясь от него усеченным итерационным циклом, зависящим от величины |Мду, и начальными условиями Ни-д

У.У,п-| nyiWi; (4)

yB -AyjWj} i(U4y-3.

Итерационный процесс протекает до выполнения п-1 итераций, что обеспечивает вычисление частного с погрешностью IД Ul4 . Для устранения возможного накопления ошибки при многократном определении частного целесообразно иметь удвоенную разрядность регистров 7, сдвигающего регистра 11, сумматора 2 и У0 определять с учетом (п-1)-го остатка, характеризующего выполнение (j) -ro вычисления, т.е.

V,h-, -AyjWj.(5)

Таким образом, алгоритм работы предлагаемого устройства имеет вид

x,-4,x.+qrx-2 m° , h,

) У,-4, У ЧГУ-2 УП-,

+ 1, если If, 0;

j -1, если У,- 0:

останов, если lf,s О, Y,41 ,-Ч;-.у2-( «п.,, с учетом условий (4) и (5) и начальных значений . , + , , wi + ,n-i и выражения W|4( -W.+q; - .

Первоначальные значения U и W могут вычисляться в предлагаемом устройстве аналогично известному или заноситься извне.

Формула изобретения

Устройство для деления, содержащее регистры частного и остатка, первый и второй сумматоры, первый и второй сдвигающие регистры, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход регистра остатка соединен с входом первого слагаемого первого сумматора, выход которого соединен с информационным входом регистра остатка, а управляющий-вход - с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход регистра частного соединен с входом первого ела-

5154

гаемого второго сумматора, выход ко- торого соединен с информационным входом регистра частного, о т л и - ч ающееся тем, что, с целью повышения быстродействия для незначительных приращений аргументов, в него введены регистр текущего значения делимого, регистр текущего значения делителя, два мультиплексора, третий, четвертый и пятый сумматоры, четыре сдвигателя, две схемы поиска левой единицы, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два триггера, сдвигающий регистр множителя, третий сдвигающий регистр, два элемента И, элемент ИЛИ, дешифратор определения нулевого кода и генератор тактовых импульсов, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с управляющими входами первого и второго мультиплексоров и выходом первого триггера, установочный вход которого соединен с входом пуска устройства, а вход сброса - с выходом элемента ИЛИ, первый вход которого соединен с выходом дешифратора определения нулево.го кода, вход которого соединен с выходом первого сумматора и входом второго триггера, инверсный выход которого -соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход второго слагаемого первого сумматора соединен с выходом первого мультиплексора, первый информационный вход которого соединен с выходом первого сдвигающего регистра, информационный вход которого соединен с1 выходом первого сдвигателя, информационный вход которого соединен с входом делителя устройства, информационным входом регистра текущего значения делителя и входом первого .слагаемого третьего сумматора, вход второго слагаемого которого соединен с выходом регистра текущего значения делителя, а выход - с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ШШ и входом первой схемы поиска левой единицы, выходы .которой соединены с (1-3)-ми управляющими входами первого и второго сдвигателей, i-ми управляющими входами третьего сдвигателя (,..., п, где п - разрядность операндов и

0

976

информационными входами второго сдвигающего регистра, выход n-го разряда , которого соединен с вторым входом элемента ИЛИ, а управляющий вход - с управляющими входами сдвигающего регистра множителя, регистра остатка, первого сдвигающего регистра и выходом второго элемента И, первый вход которого соединен с выходом первого элемента И и управляющими входами регистра частного и третьего сдвигающего регистра, информационный вход которого соединен с выходом

5 вт-ррого сдвигателя, информационный вход которого соединен с входом делимого устройства, информационным входом регистра текущего значения делимого и входом первого слагаемого

0 четвертого сумматора, вход второго слагаемого которого соединен с выходом регистра текущего значения делимого, а выход - с входом второй схемы поиска левой единицы и первым вхо5 дом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом первого триггера, а выход - с управляющими входами второго и пятого сумматоров, вход второго

0 слагаемого второго сумматора соединен с выходом второго мультиплексора, первый информационный вход которого соединен с выходом третьего сдвигающего регистра, а второй информационный вход - с выходом четвертого сдви- гателя, информационный вход которого соединен с информационным входом третьего сдвигателя и выходом сдвигающего регистра множителя, информационный вход которого соединен с выходом пятого сумматора, входы первого и второго слагаемых которого соединены соответственно с выходами сдвигающего регистра множителя и второго сдвигающего регистра, выходы разрядов второй схемы поиска левой единицы соединены с i-ми управляющими входами четвертого сдзигателя, выход третьего сдвигателя соединен

д с вторым информационным входом первого мультиплексора, выход регистра текущего значения делителя соединен с входом второго слагаемого третьего сумматора.

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления | 1990 |

|

SU1742815A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1264167A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

Устройство относится к вычислительной технике, предназначено для выполнения операции деления над двоичными числами с фиксированной точкой и может быть использовано как самостоятельно, так и в составе специализированных ЭВМ. Цель изобретения - повышение быстродействия для случаев незначительных приращений аргументов, которая достигается за счет выполнения не N итераций, а только N-(*98M-3) при обработке не самих операндов, а их приращений, сохраняя при этом возможность работы в обычных условиях аналогично прототипу. 1 ил.

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М.: Наука, 1969, с.496-498 | |||

| Оранский A.M | |||

| Аппаратные методы в цифровой вычислительной технике | |||

| Минск, БГУ, 1977, с | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

Авторы

Даты

1990-02-07—Публикация

1987-11-09—Подача