Изобретение относится к вычислительной технике и может быть использовано в устройствах обмена систем обработки данных с промежуточным хранением информации.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения обмена кадрами переменной длины.

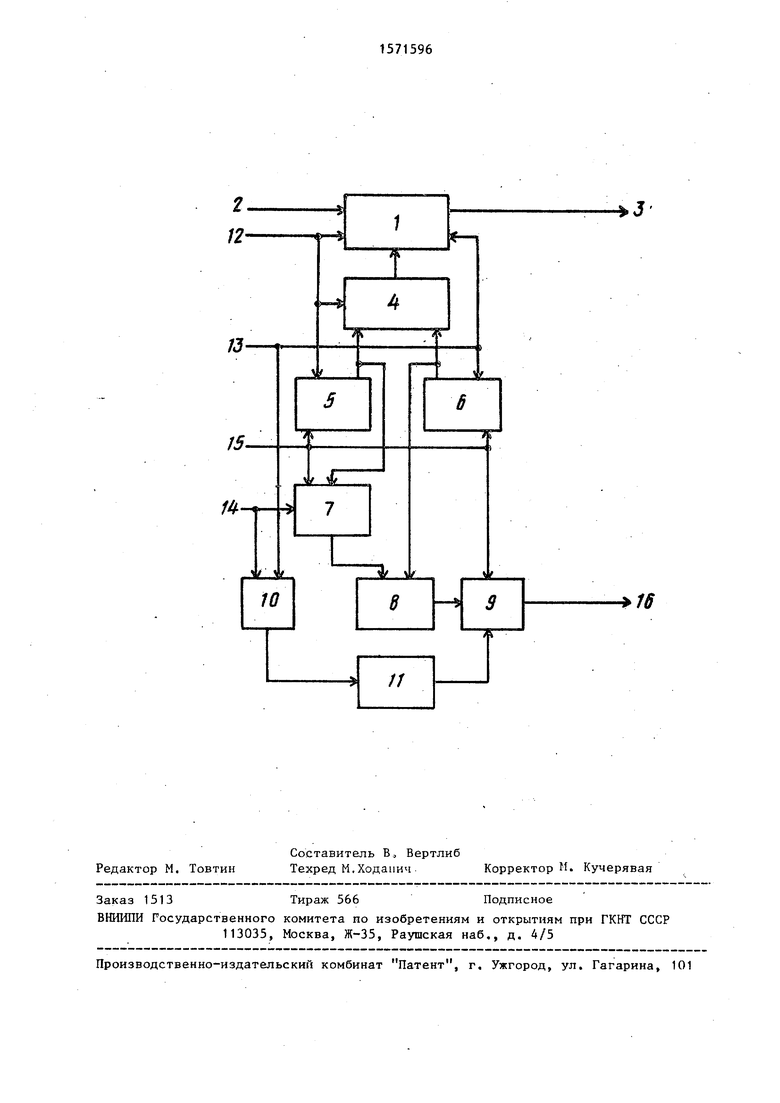

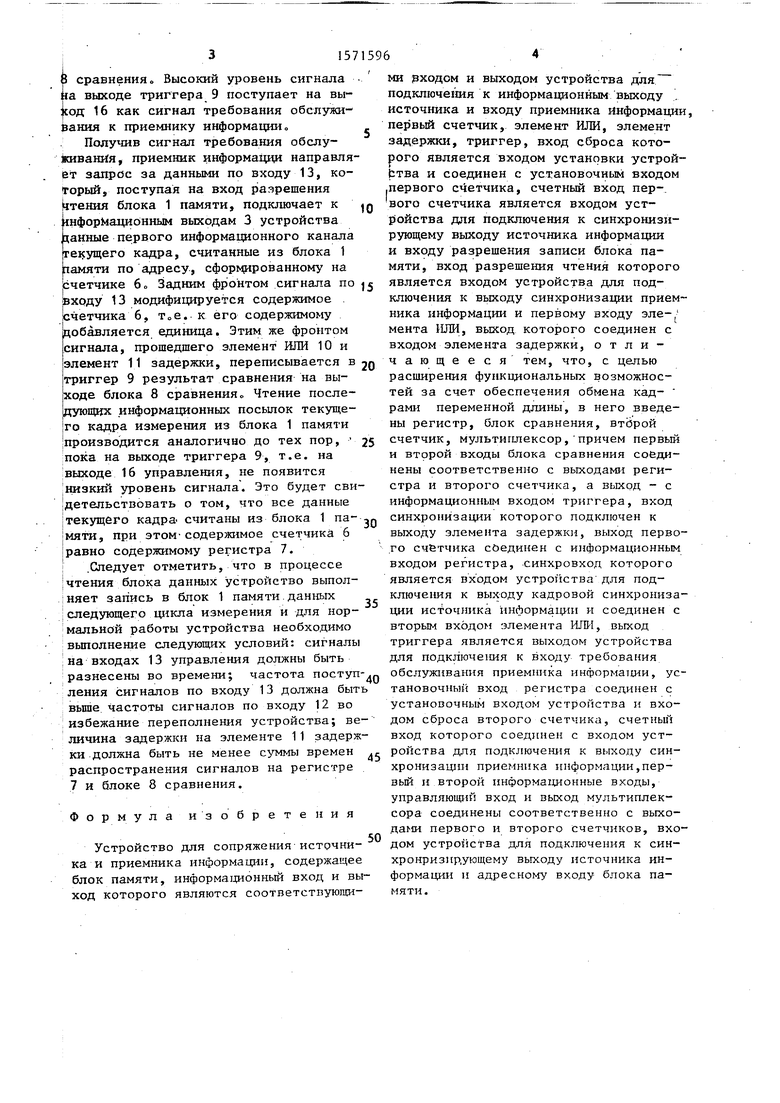

На чертеже представлена функциональная схема устройства.

Устройство содержит блок 1 памяти, информационные вход 2 и выход 3, мультиплексор 4, счетчики 5 и 6, регистр 7, блок 3 сравнения, триггер 9, элемент ИЛИ 10, элемент 11 задержки, входы 12-1А управления, вход 15 установки,, выход 16 управления.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 15 установки счетчики 5 и 6, регистр 7 и триггер 9 устанавливаются в нулевое состояние.

При выполнении операции записи записываемые данные поступают на вход 2 в сопровождении сигнала на входе 12 управления Сигнал на входе 12 управления, воздействуя на вход управления мультиплексора 4 и вход разрешения записи/чтения блока 1 памяти, обеспечивает запись данных, находящихся на входе 2, в блок 1 памяти по адресу, сформированному на счетчике 5 Задним фронтом сигнала на входе 12 модифицируется содержимое счетчика 5 (добавляется единица). Запись последующих информационных посыпок кадра выполняет ся устройством аналогично. По окончании текущего измерительного цикла на ,вход 14 поступает сигнал, который переписывает в регистр 7 содержимое счетчика 5 и, проходя через элемент ИЛИ 10 и элемент 11 задержки, фиксирует в триггере 9 выходной сигнал блока 8 сравнения. На выходе триггера 9 появляется высокий уровень сигнала при неравенстве кодов на входах блока

(Л

с

ел

4

01

so

Oi

1

8 сравнения Высокий уровень сигнала на выходе триггера 9 поступает на выход 16 как сигнал требования обслужи- ранил к приемнику информации

Получив сигнал требования обслуживания, приемник информации направляет запрос за данными по входу 13, который, поступая на вход разрешения Чтения блока 1 памяти, подключает к информационным выходам 3 устройства данные первого информационного канала текущего кадра, считанные из блока 1 памяти по адресу, сформированному на счетчике 6 Задним фронтом сигнала по входу 13 модифицируется содержимое счетчика 6, т„е. к его содержимому добавляется единица. Этим же фронтом сигнала, прошедшего элемент ИЛИ 10 и элемент 11 задержки, переписывается в 2 триггер 9 результат сравнения на выходе блока 8 сравнения« Чтение последующих информационных посылок текуще- го кадра измерения из блока 1 памяти производится аналогично до тех пор, 2 пока на выходе триггера 9, т.е. на выходе 16 управления, не появится низкий уровень сигнала. Это будет сви- детельствовать о том, что все данные текущего кадра считаны из блока 1 па- мяти, при этом содержимое счетчика 6 равно содержимому регистра 7.

Следует отметить, что в процессе чтения блока данных устройство выполняет запись в блок 1 памяти данных следующего цикла измерения и для нормальной работы устройства необходимо выполнение следующих условий: сигналы на входах 13 управления должны быть разнесены во времени; частота поступления сигналов по входу 13 должна быть выше частоты сигналов по входу 12 во избежание переполнения устройства; величина задержки на элементе 11 задержки должна быть не менее суммы времен распространения сигналов на регистре 7 и блоке 8 сравнения.

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее блок памяти, информационный вход и выход которого являются соответствующее-

0

0 5

50

ми рходом и выходом устройства для подключения к информационным выходу источника и входу приемника информации, первый счетчик, элемент ИЛИ, элемент задержки, триггер, вход сброса которого является входом установки устрой- Ьтва и соединен с установочным входом .первого счетчика, счетный вход пер- вого счетчика является входом устройства для подключения к синхронизирующему выходу источника информации и входу разрешения записи блока памяти, вход разрешения чтения которого является входом устройства для подключения к выходу синхронизации приемника информации и первому входу элемента ИЛИ, выход которого соединен с входом элемента задержки, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения обмена кадрами переменной длины, в него введены регистр, блок сравнения, второй счетчик, мультиплексор, причем первый и второй входы блока сравнения соединены соответственно с выходами регистра и второго счетчика, а - с информационным входом триггера, вход синхронизации которого подключен к выходу элемента задержки, выход первого счетчика соединен с информационным входом регистра, синхровход которого является входом устройства для подключения к выходу кадровой синхронизации источника инАормацин и соединен с вторым входом -элемента ИЛИ, выход триггера является выходом устройства для подключения к входу требования обслуживания приемника информации, установочный вход регистра соединен с установочным входом устройства и входом сброса второго счетчика, счетный вход которого соединен с входом устройства для подключения к выходу синхронизации приемника информации,первый и второй информационные входы, управляющий вход и выход мультиплексора соединены соответственно с выходами первого и второго счетчиков, входом устройства для подключения к син- хронризир.ующему выходу источника информации и адресному входу блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1647579A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1658160A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Устройство для сопряжения источника и приемника информации | 1989 |

|

SU1730630A2 |

| Устройство сопряжения источника и приемника информации | 1991 |

|

SU1824639A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

Изобретение относится к вычислительной технике. Цель изобретения состоит в расширении функциональных возможностей за счет обеспечения обмена кадрами переменной длины. Это достигается тем, что устройство содержит блок памяти, мультиплексор, два счетчика, триггер, регистр, блок сравнения, элемент ИЛИ, элемент задержки с соответствующими связями. 1 ил.

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1416988A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1236491A1 |

Авторы

Даты

1990-06-15—Публикация

1988-01-04—Подача