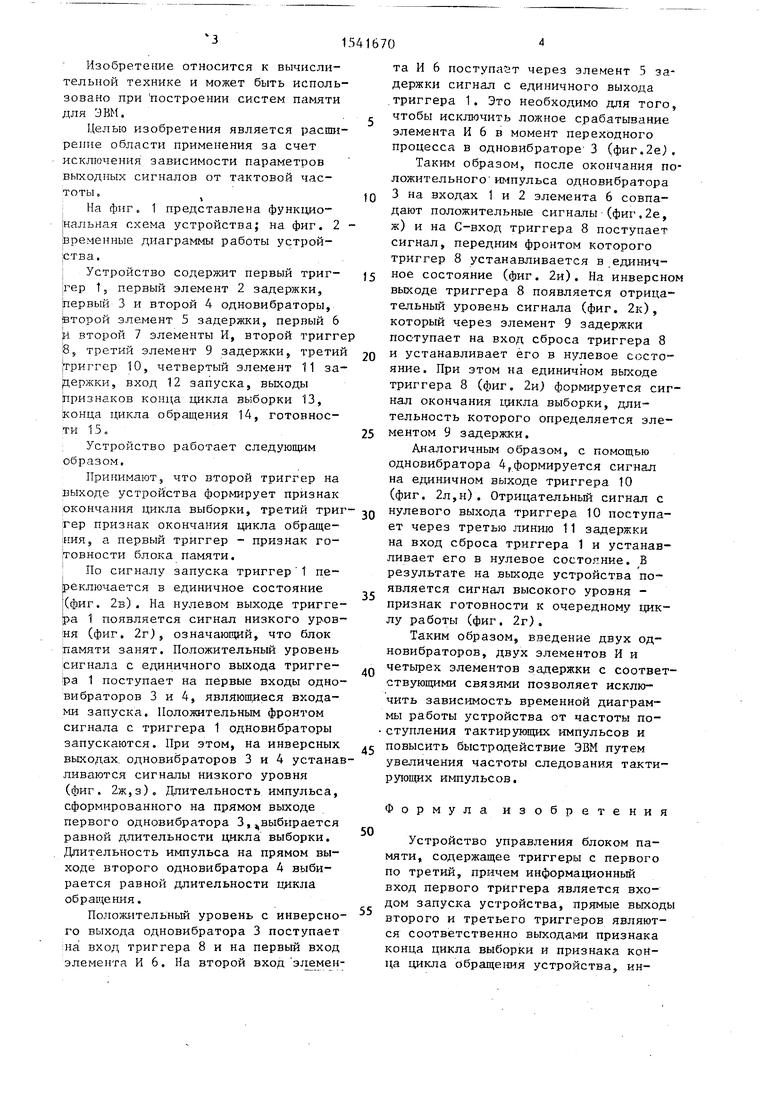

Фиг.1

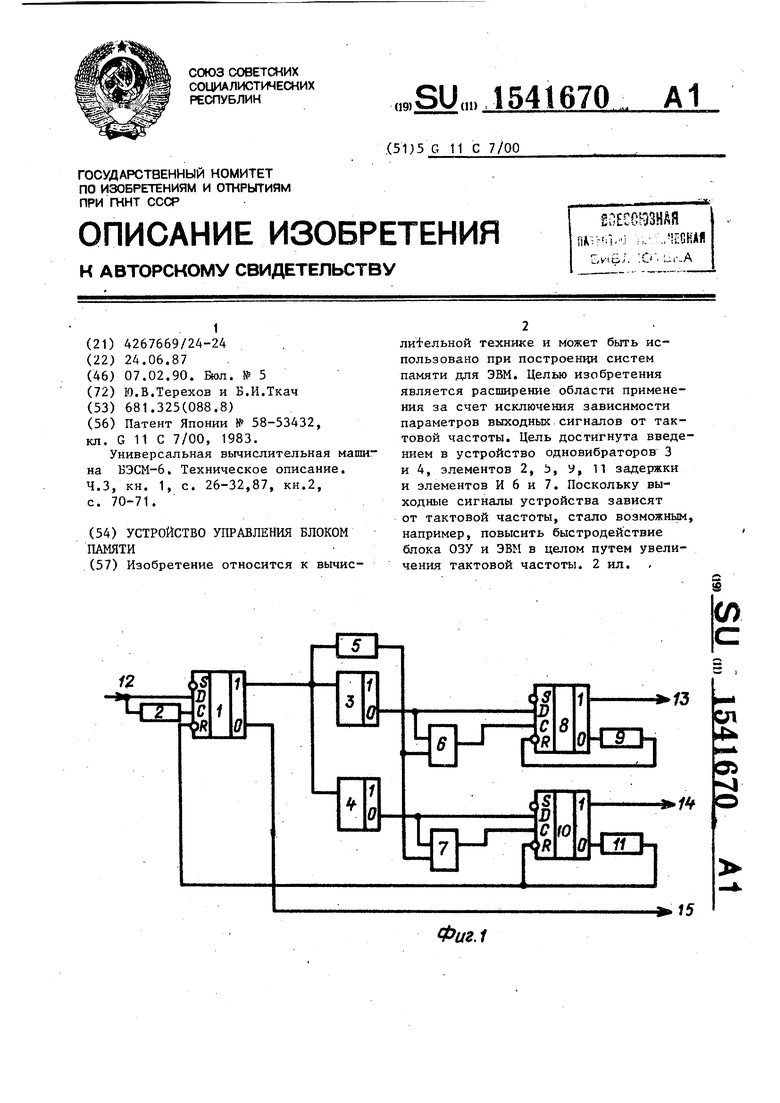

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти для ЭВМ.

Целью изобретения является расширение области применения за счет исключения зависимости параметров выходных сигналов от тактовой частоты.г

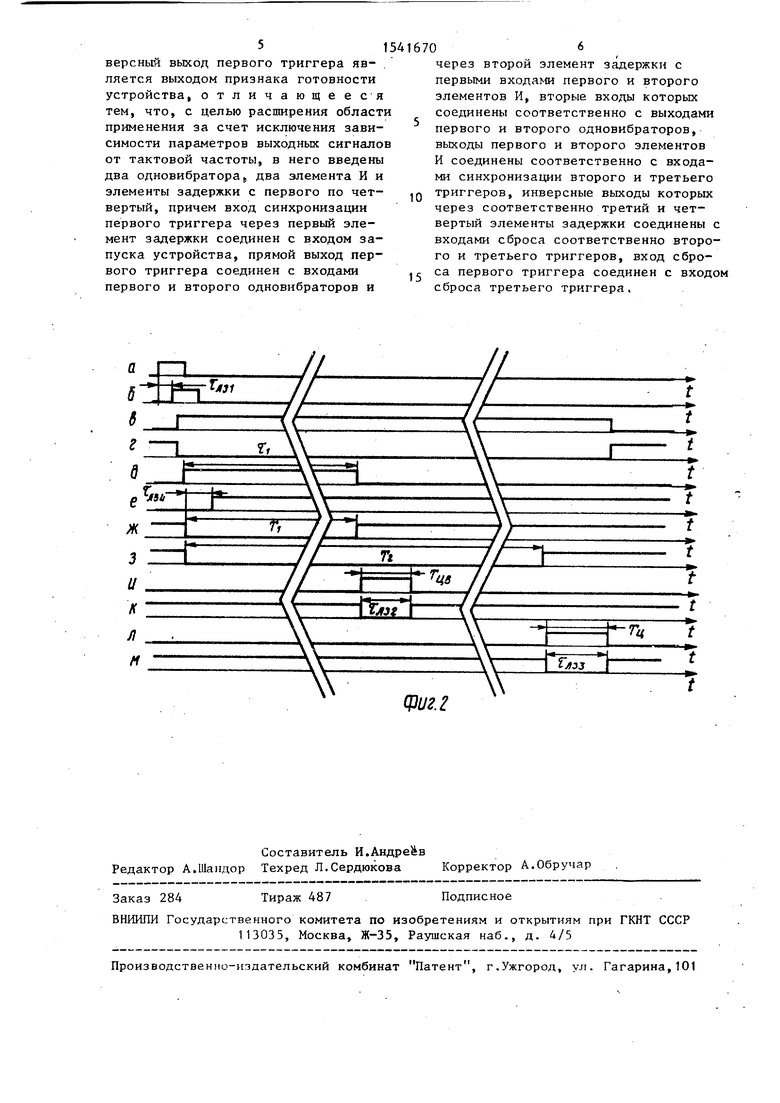

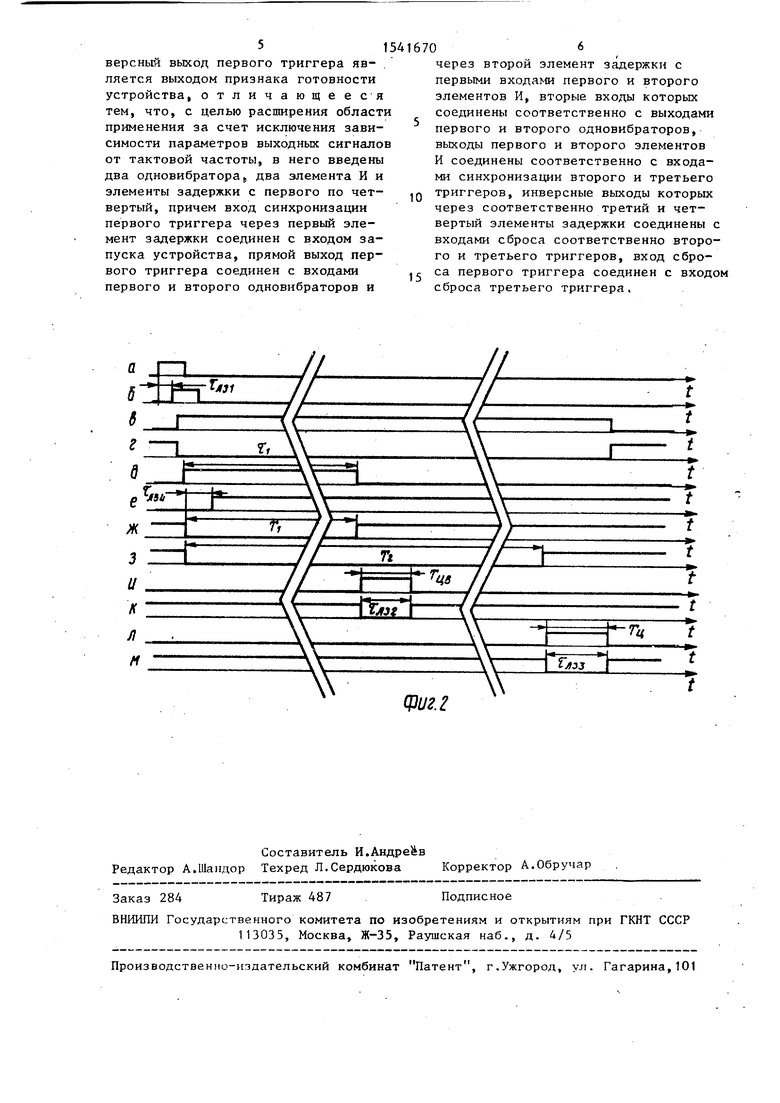

На фиг. 1 представлена функцио- нальная схема устройства; на фиг. 2 - временные диаграммы работы устройства.

Устройство содержит первый триг- гер 1, первый элемент 2 задержки, первый 3 и второй 4 одновибраторы, второй элемент 5 задержки, первый 6 Јi второй 7 элементы И, второй триггер 8 s третий элемент 9 задержки, третий Триггер 10, четвертый элемент 11 задержки, вход 12 запуска, выходы признаков конца цикла выборки 13, конца цикла обращения 14, готовности 15,

Устройство работает следующим образом.

Принимают, что второй триггер на выходе устройства формирует признак окончания цикла выборки, третий триг гер признак окончания цикла обращения, а первый триггер - признак готовности блока памяти.

По сигналу запуска триггер 1 переключается в единичное состояние (фиг. 2в) . На нулевом выходе тригге- |ра 1 появляется сигнал низкого уровня (фиг. 2г), означающий, что блок памяти занят. Положительный уровень сигнала с единичного выхода тригге- ра 1 поступает на первые входы одно- вибраторов 3 и 4, являющиеся входами запуска. Положительным фронтом сигнала с триггера 1 одновибраторы запускаются. При этом, на инверсных выходах одновибраторов 3 и 4 устанавливаются сигналы низкого уровня (фиг. 2ж,з). Длительность импульса, сформированного на прямом выходе первого одновибратора 3,выбирается равной длительности цикла выборки. Длительность импульса на прямом выходе второго одновибратора 4 выбирается равной длительности цикла обращения.

Положительный уровень с инверсного выхода одновибратора 3 поступает на вход триггера 8 и на первый вход элемента И 6. На второй вход элемента И 6 поступает через элемент 5 задержки сигнал с единичного выхода триггера 1. Это необходимо для того, чтобы исключить ложное срабатывание элемента И 6 в момент переходного процесса в одновибраторе 3 (фиг.2е).

Таким образом, после окончания положительного импульса одновибратора 3 на входах 1 и 2 элемента 6 совпадают положительные сигналы (фиг,2е, ж) и на С-вход триггера 8 поступает сигнал, передним фронтом которого триггер 8 устанавливается в единичное состояние (фиг. 2и). На инверсно выходе триггера 8 появляется отрицательный уровень сигнала (фиг. 2к), который через элемент 9 задержки поступает на вход сброса триггера 8 и устанавливает его в нулевое состояние. При этом на единичном выходе триггера 8 (фиг. 2и) формируется сигнал окончания цикла выборки, длительность которого определяется элементом 9 задержки.

Аналогичным образом, с помощью одновибратора 4,формируется сигнал на единичном выходе триггера 10 (фиг. 2л,н). Отрицательный сигнал с нулевого выхода триггера 10 поступает через третью линию 11 задержки на вход сброса триггера 1 и устанавливает его в нулевое состояние. В результате на выходе устройства появляется сигнал высокого уровня - признак готовности к очередному циклу работы (фиг. 2г),

Таким образом, введение двух одновибраторов, двух элементов И и четырех элементов задержки с соответствующими связями позволяет исключить зависимость временной диаграммы работы устройства от частоты поступления тактирующих импульсов и повысить быстродействие ЭВМ путем увеличения частоты следования тактирующих импульсов.

Формула изобретения

Устройство управления блоком памяти, содержащее триггеры с первого по третий, причем информационный вход первого триггера является входом запуска устройства, прямые выходы второго и третьего триггеров являются соответственно выходами признака конца пикла выборки и признака конца цикла обращения устройства, инверснын выход первого триггера является выходом признака готовности устройства, отличающееся тем, что, с целью расширения област применения за счет исключения зависимости параметров выходных сигнало от тактовой частоты, в него введены два одновибратора8 два элемента И и элементы задержки с первого по четвертый, причем вход синхронизации первого триггера через первый элемент задержки соединен с входом запуска устройства, прямой выход первого триггера соединен с входами первого и второго одновибраторов и

5

через второй элемент задержки с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с выходами первого и второго одновибраторов, выходы первого и второго элементов И соединены соответственно с входами синхронизации второго и третьего триггеров, инверсные выходы которых через соответственно третий и четвертый элементы задержки соединены с входами сброса соответственно второго и третьего триггеров, вход сброса первого триггера соединен с входом сброса третьего триггера .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для управления вводом изображения | 1989 |

|

SU1751738A1 |

| Электронная вычислительная машина с прямым доступом в память | 1990 |

|

SU1751776A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти для ЭВМ. Целью изобретения является расширение области применения за счет исключения зависимости параметров выходных сигналов от тактовой частоты. Цель достигнута введением в устройство одновибраторов 3 и 4, элементов 2,5,9,11 задержки и элементов И 6 и 7. Поскольку выходные сигналы устройства не зависят от тактовой частоты, стало возможным, например, повысить быстродействие блока ОЗУ и ЭВМ в целом путем увеличения тактовой частоты. 2 ил.

Составитель И.Андреев Редактор А.Шандор Техред Л.Сердюкова Корректор А.Обручар

Заказ 284

Тираж 487

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Щи г. 2

Подписное

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Техническое описание | |||

| Ч.З, кн | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

Авторы

Даты

1990-02-07—Публикация

1987-06-24—Подача