ftl

1бр

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для коррекции информации вблОКАХ пОСТОяННОй пАМяТи | 1979 |

|

SU849308A1 |

| Постоянное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1642524A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения накопителя с каналом ввода/вывода | 1984 |

|

SU1251094A1 |

Изобретение относится к вычислительной технике и может быть использовано для коррекции информации в блоках постоянной памяти. Цель изобретения - упрощение устройства. Устройство содержит накопитель 4, блок преобразования кодов 5, мультиплексор 6, блок памяти корректора 7, выходной мультиплексор 8. Введение мультиплексора и его связей с блоком памяти корректора и блоком преобразования кодов позволяет упростить устройство. 1 з.п. ф-лы, 2 ил.

fa

iSfД

ГР

п

8

4СП

4Ь

СО 4 Од

б

V

4

1бр

W

м

VP

фиг.1

Изобретение относится к вычислительной технике и может быть использовано для коррекции информации в блоках постоянной памяти, выполнен- , ЙОй, например, на масочных БИС ПЗУ. Цель изобретения - упрощение устройства.

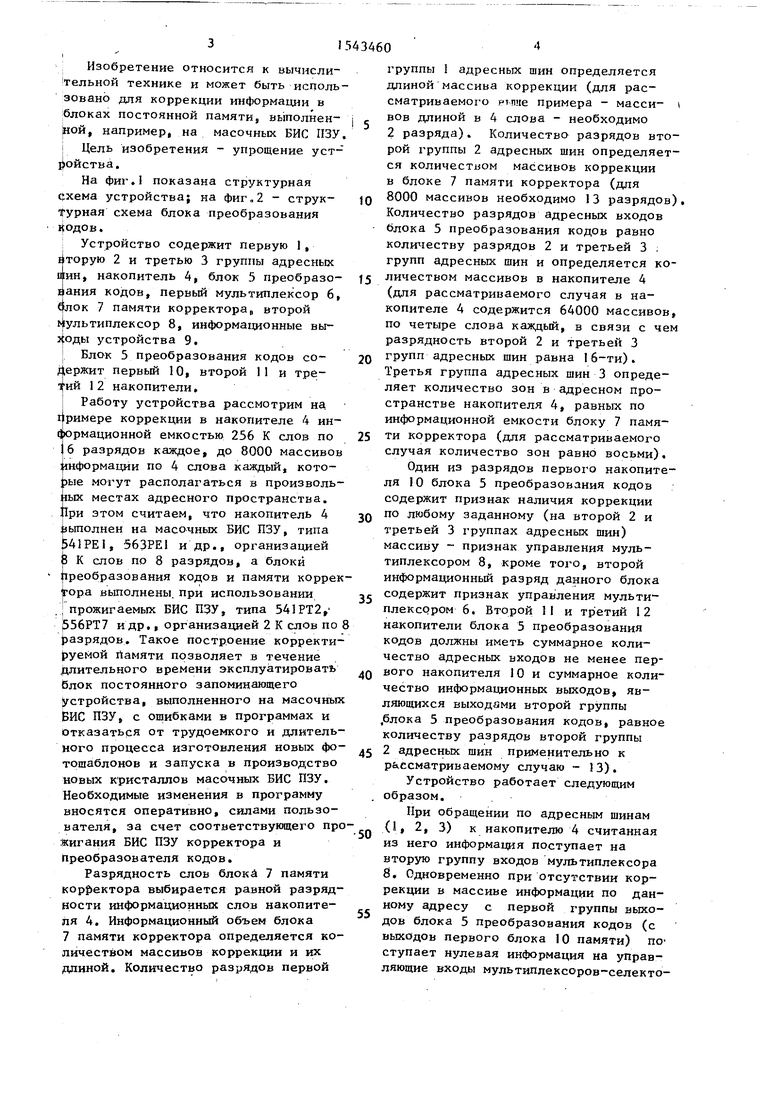

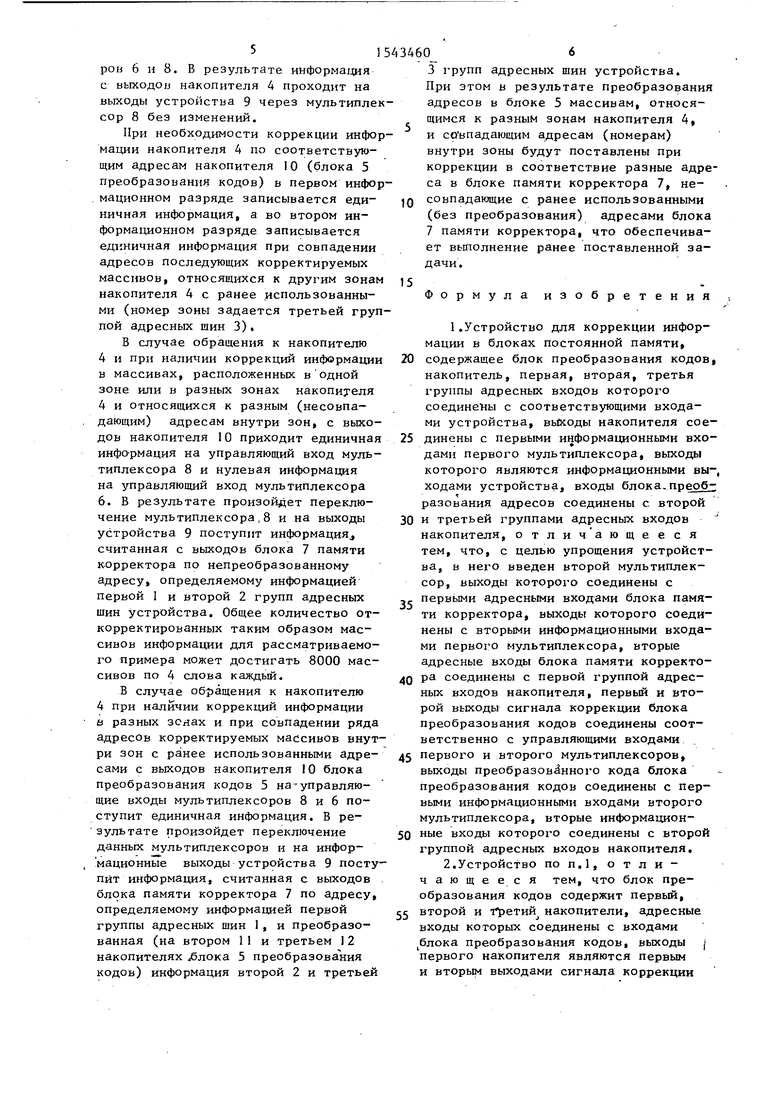

На фиг.1 показана структурная схема устройства; на фиг,,2 - структурная схема блока преобразования «одов.

Устройство содержит первую 1, йторую 2 и третью 3 группы адресных шин, накопитель 4, блок 5 преобразования кодов, первый мультиплексор 6, блок 7 памяти корректора„ второй мультиплексор 8, информационные вы- устройства 9.

Блок 5 преобразования кодов со- Держит первый 10, второй 11 и тре- ий 12 накопители.

Работу устройства рассмотрим на примере коррекции в накопителе 4 информационной емкостью 256 К слов по 6 разрядов каждое, до 8000 массивов информации по 4 слова каждый, которые могут располагаться в произвольных местах адресного пространства. Три этом считаем, что накопитель 4 выполнен на масочных БИС ПЗУ, типа 541РЕ1, 563РЕ1 и др., организацией 3 К слов по 8 разрядов, а блоки преобразования кодов и памяти коррек- t-opa выполнены при использовании

прожигаемых БИС ПЗУ, типа 541РТ2,- 556РТ7 и др., организацией 2 К слов по 8 разрядов. Такое построение корректируемой памяти позволяет в течение длительного времени эксплуатировать блок постоянного запоминающего устройства, выполненного на масочных

45

ВИС ПЗУ, с ошибками в программах и отказаться от трудоемкого и длительного процесса изготовления новых фотошаблонов и запуска в производство новых кристаллов масочных БИС ПЗУ. Необходимые изменения в программу вносятся оперативно, силами пользователя, за счет соответствующего про- Кигания БИС ПЗУ корректора и Преобразователя кодов.

Разрядность слов блока 7 памяти корректора выбирается равной разрядности информационных слов накопителя 4. Информационный объем блока 7 памяти корректора определяется ко личеством массивов коррекции и их длиной. Количество разрядов первой

15434604

группы 1 адресных шин определяется длиной массива коррекции (для рассматриваемого мпче примера - масси- BOB длиной в 4 слова - необходимо 2 разряда). Количество разрядов второй группы 2 адресных шин определяется количеством массивов коррекции в блоке 7 памяти корректора (для

10 8000 массивов необходимо 13 разрядов). Количество разрядов адресных входов блока 5 преобразования кодов равно количеству разрядов 2 и третьей 3 групп адресных шин и определяется ко15 личеством массивов в накопителе 4 (для рассматриваемого случая в накопителе 4 содержится 64000 массивов, по четыре слова каждый, в связи с чем разрядность второй 2 и третьей 3

20 групп адресных шин равна 16-ти).

Третья группа адресных шин 3 определяет количество зон в адресном пространстве накопителя 4, равных по информационной емкости блоку 7 памя-

25 ти корректора (для рассматриваемого случая количество зон равно восьми).

Один из разрядов первого накопителя 10 блока 5 преобразования кодов содержит признак наличия коррекции по любому заданному (на второй 2 и третьей 3 группах адресных шин) массиву признак управления мультиплексором 8, кроме того, второй информационный разряд данного блока

,г содержит признак управления мультиплексором 6. Второй II и третий 12 накопители блока 5 преобразования кодов должны иметь суммарное количество адресных входов не менее пер40 в°го накопителя 10 и суммарное количество информационных выходов, являющихся выходами второй группы .блока 5 преобразования кодов, равное количеству разрядов второй группы 2 адресных шин применительно к рассматриваемому случаю - 13).

Устройство работает следующим образом.

При обращении по адресным шинам (, 2, 3) к накопителю 4 считанная из него информация поступает на вторую группу входов мультиплексора 8. Одновременно при отсутствии коррекции в массиве информации по данному адресу с первой группы выходов блока 5 преобразования кодов (с выходов первого блока 10 памяти) по ступает нулевая информация на управляющие входы мультиплексоров-селекто30

55

ров 6 и 8. В результате информация с выходов накопителя 4 проходит на выходы устройства 9 через мультиплексор 8 без изменений.

При необходимости коррекции информации накопителя 4 по соответствующим адресам накопителя 10 (блока 5 преобразования кодов) в первом информационном разряде записывается единичная информация, а во втором информационном разряде записывается единичная информация при совпадении адресов последующих корректируемых массивов, относящихся к другим зонам накопителя 4 с ранее использованными (номер зоны задается третьей группой адресных шин 3).

В случае обращения к накопителю 4 и при наличии коррекций информации в массивах, расположенных в одной зоне или в разных зонах накопителя 4 и относящихся к разным (несовпадающим) адресам внутри зон, с выходов накопителя 10 приходит единичная информация на управляющий вход мультиплексора 8 и нулевая информация на управляющий вход мультиплексора 6. В результате произойдет переключение мультиплексора и на выходы устройства 9 поступит информация., считанная с выходов блока 7 памяти корректора по непреобразованному адресу, определяемому информацией первой 1 и второй 2 групп адресных шин устройства. Общее количество откорректированных таким образом массивов информации для рассматриваемого примера может достигать 8000 массивов по 4 слова каждый.

В случае обращения к накопителю 4 при наличии коррекций информации в разных зснах и при совпадении ряда адресов корректируемых массивов внутри зон с ранее использованными адресами с выходов накопителя 10 блока преобразования кодов 5 на управляющие входы мультиплексоров 8 и 6 поступит единичная информация. В результате произойдет переключение данных мультиплексоров и на информационные выходы устройства 9 поступит информация, считанная с выходов блока памяти корректора 7 по адресу, определяемому информацией первой группы адресных шин 1, и преобразованная (на втором 11 и третьем 12 накопителях яблока 5 преобразования кодов) информация второй 2 и третьей

3 групп адресных шин устройства. При этом в результате преобразования адресов в блоке 5 массивам, относящимся к разным зонам накопителя 4, и совпадающим адресам (номерам) внутри зоны будут поставлены при коррекции в соответствие разные адреса в блоке памяти корректора 7, несовпадающие с ранее использованными (без преобразования) адресами блока 7 памяти корректора, что обеспечивает выполнение ранее поставленной задачи.

Формула изобретения

0

5

0

5

0

5

715434608

блока преобразования адресов выходы ются выходами преобразованного кода

второго и третьего накопителей являблока преобразования адресов,

I

блока преобразования адресов,

Щиг.2

| Устройство для коррекции информации вблОКАХ пОСТОяННОй пАМяТи | 1979 |

|

SU849308A1 |

| Солесос | 1922 |

|

SU29A1 |

| Устройство для коррекции информации в блоке постоянной памяти | 1978 |

|

SU752501A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1990-02-15—Публикация

1988-02-29—Подача