Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1236559A1 |

| Постоянное запоминающее устройство с самоконтролем | 1988 |

|

SU1532979A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Постоянное запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1317482A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство | 1988 |

|

SU1547035A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1644233A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих постоянных запоминающих устройств с коррекцией ошибок. Целью изобретения является повышение быстродействия постоянного запоминающего устройства. Поставленная цель достигается тем, что устройство содержит блок анализа синдрома, выходы второго дешифратора соединены с третьей группой информационных входов мультиплексо- ра,выходы накопителя соединены с первой группой информационных входов мультиплексора, а выходы группы блоков ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с второй группой информационных входов мультиплексора, в результате чего информационные сигналы при отсутствии ошибок минуют группы блоков ИСКЛЮЧАЮЩЕЕ ИЛИ. 3 ил.

Изобретение относится к вычислительной технике и может быть использовано при проектировании быстродействующих постоянных запоминающих устройств с коррекцией ошибок.

Целью изобретения является повышение быстродействия постоянного запоминающего устройства.

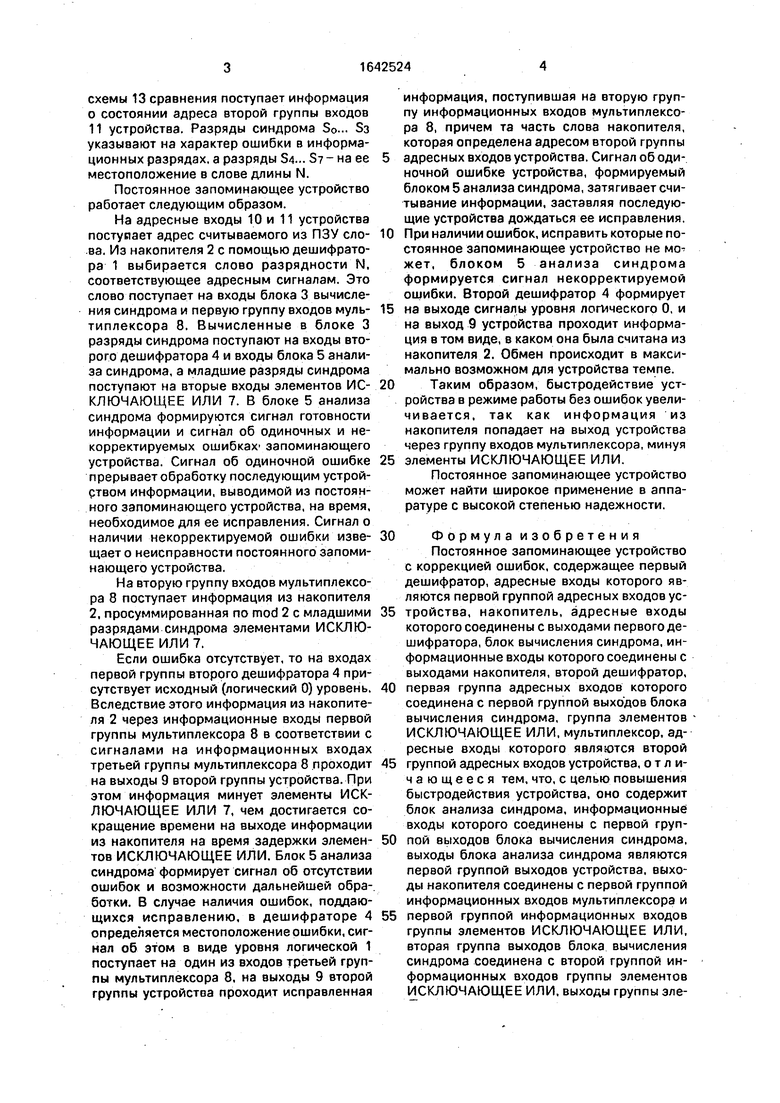

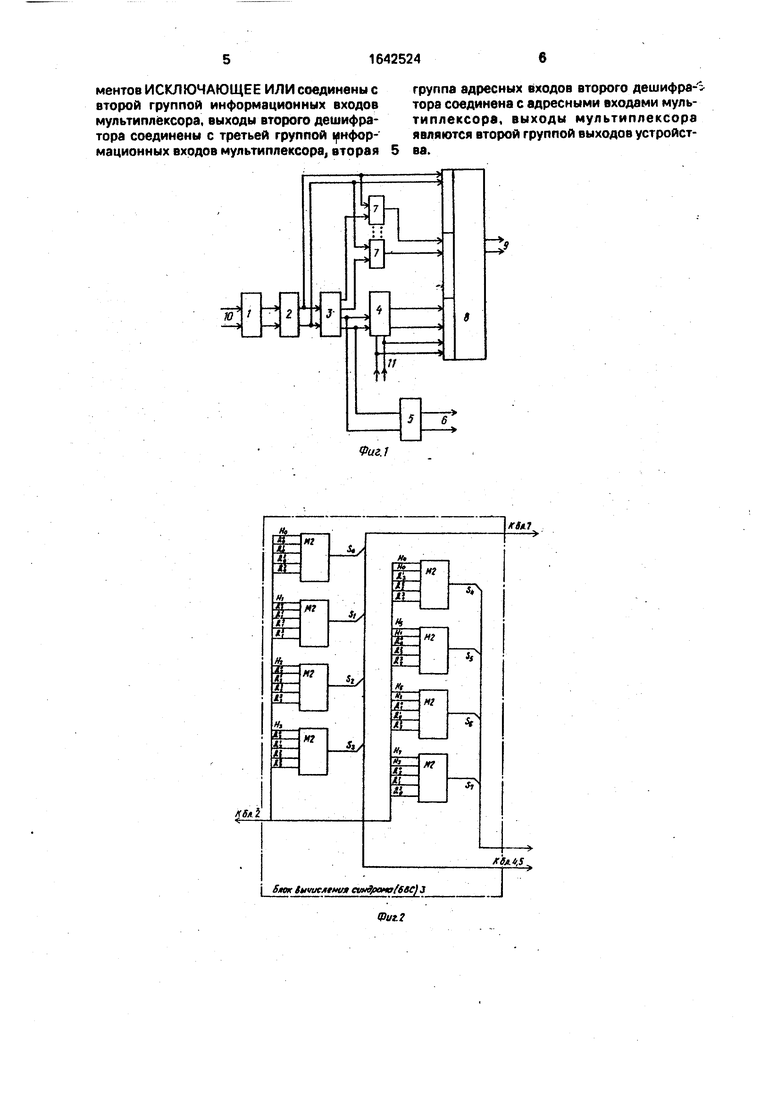

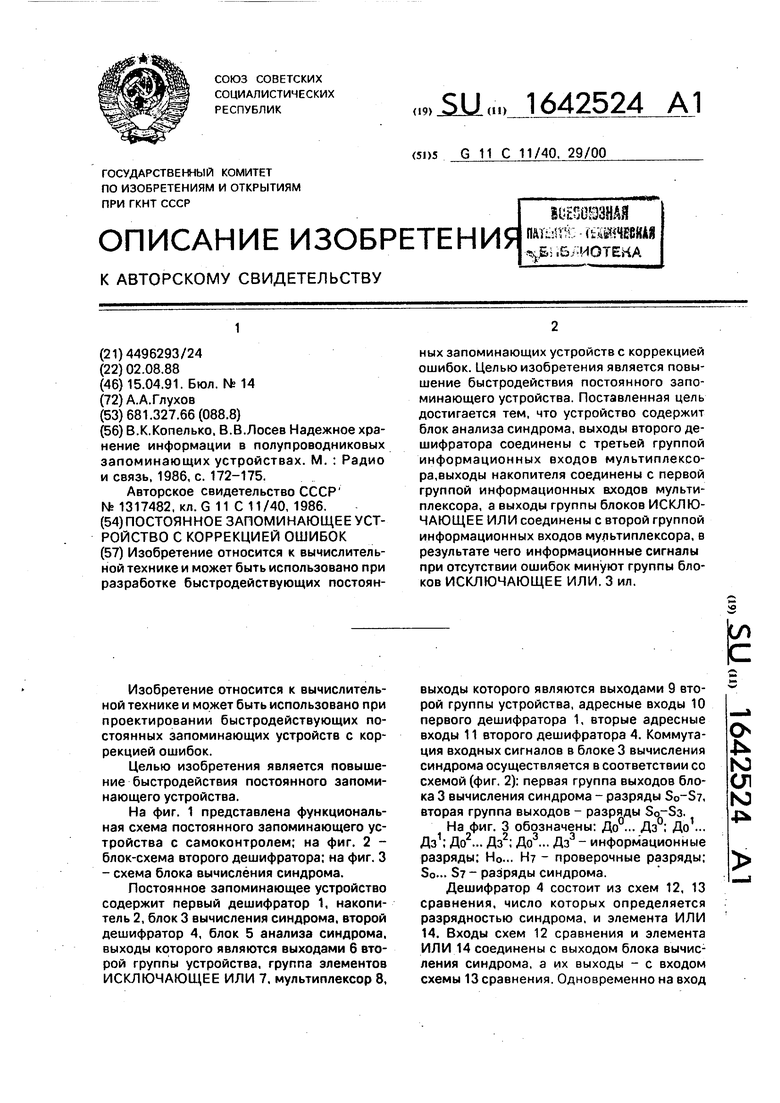

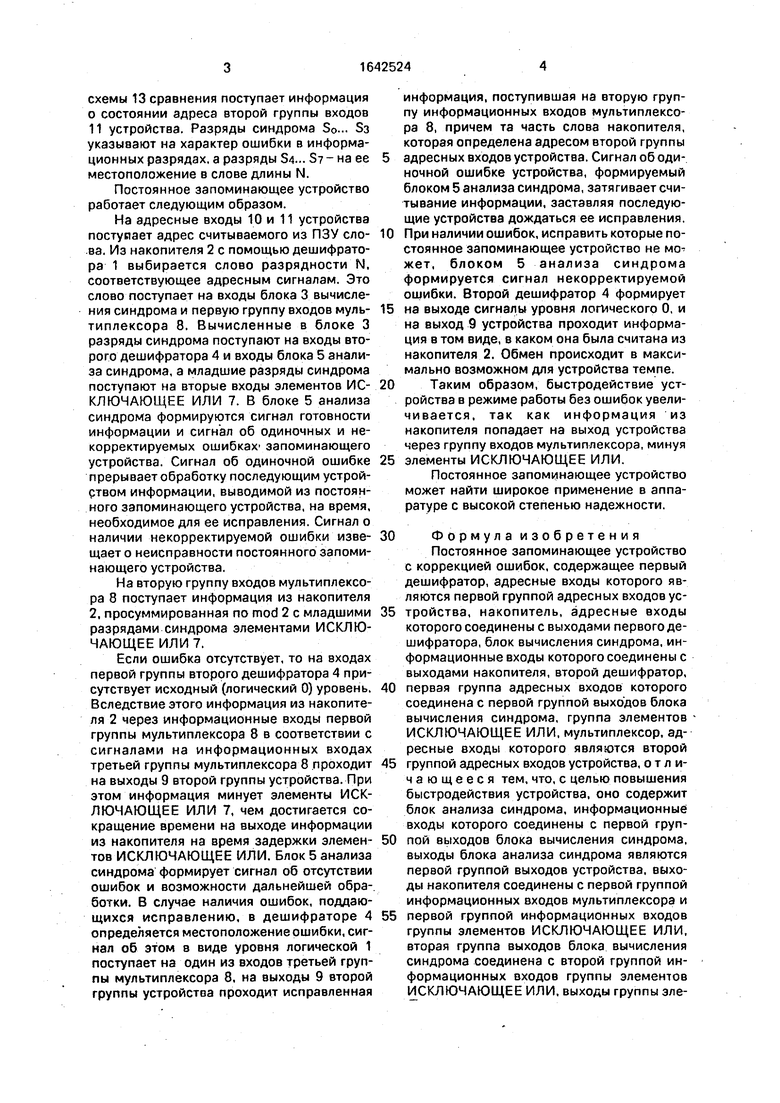

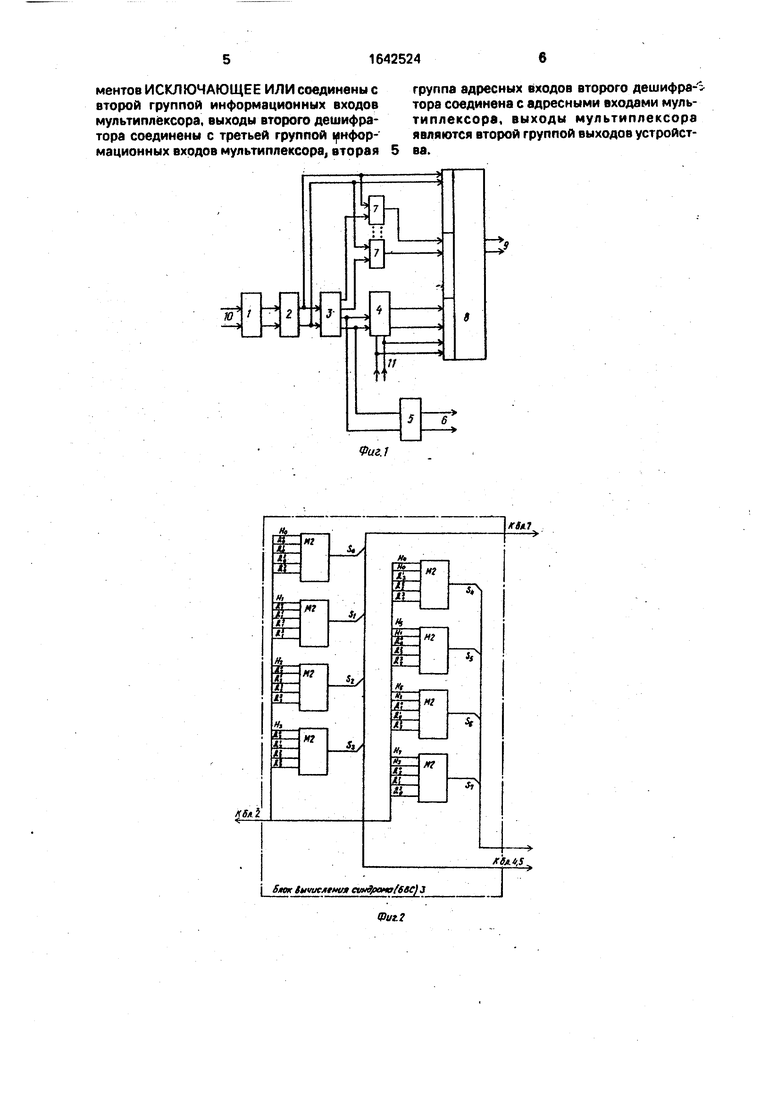

На фиг. 1 представлена функциональная схема постоянного запоминающего устройства с самоконтролем; на фиг. 2 - блок-схема второго дешифратора: на фиг. 3 - схема блока вычисления синдрома.

Постоянное запоминающее устройство содержит первый дешифратор 1, накопитель 2, блок 3 вычисления синдрома, второй дешифратор 4, блок 5 анализа синдрома, выходы которого являются выходами 6 второй группы устройства, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7. мультиплексор 8,

выходы которого являются выходами 9 второй группы устройства, адресные входы 10 первого дешифратора 1, вторые адресные входы 11 второго дешифратора 4. Коммутация входных сигналов в блоке 3 вычисления синдрома осуществляется в соответствии со схемой (фиг. 2): первая группа выходов блока 3 вычисления синдрома - разряды So-S, вторая группа выходов - разряды So-Sa.

На фиг. 3 обозначены: До0... Дз ; До1... Дз1; До2... Дз2; До3... Дз3 - информационные разряды: Н0... Н - проверочные разряды; S0... S - разряды синдрома.

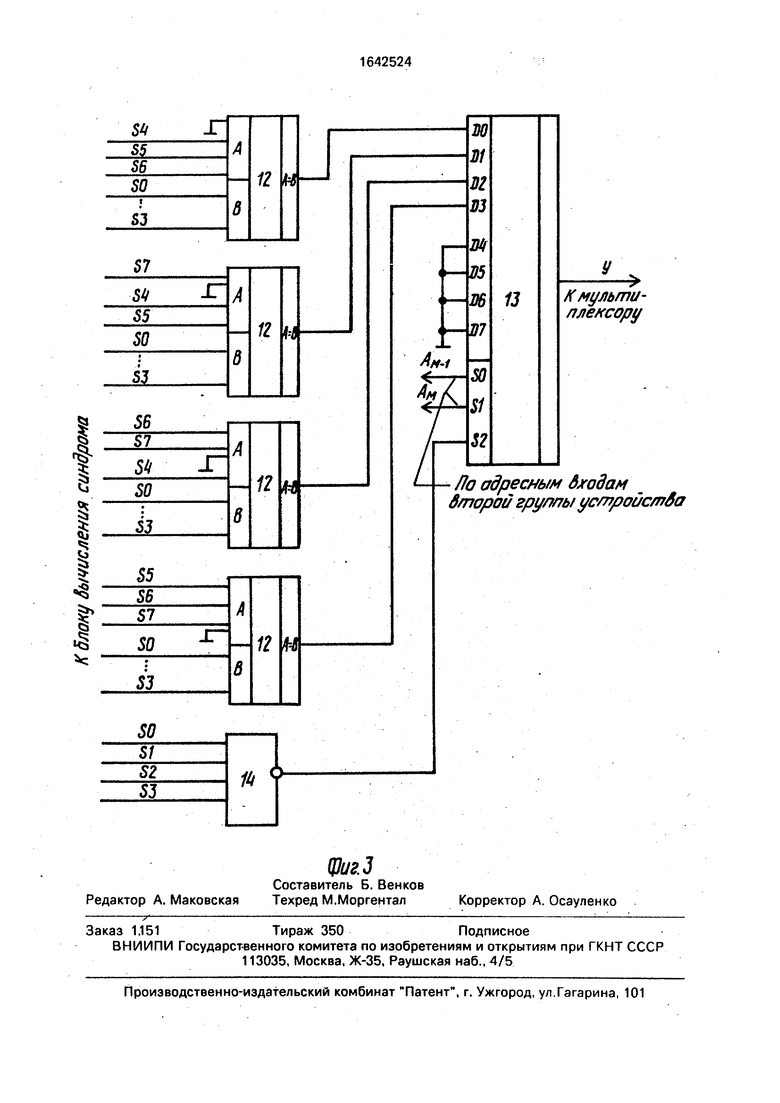

Дешифратор 4 состоит из схем 12, 13 сравнения, число которых определяется разрядностью синдрома, и элемента ИЛИ 14. Входы схем 12 сравнения и элемента ИЛИ 14 соединены с выходом блока вычисления синдрома, а их выходы - с входом схемы 13 сравнения. Одновременно на вход

О

Ьь

N) СП N3

-рь

схемы 13 сравнения поступает информация о состоянии адреса второй группы входов 11 устройства. Разряды синдрома So... 5з указывают на характер ошибки в информационных разрядах, а разряды S4... S - на ее местоположение в слове длины N.

Постоянное запоминающее устройство работает следующим образом.

На адресные входы 10 и 11 устройства поступает адрес считываемого из ПЗУ слова. Из накопителя 2 с помощью дешифратора 1 выбирается слово разрядности N, соответствующее адресным сигналам. Это слово поступает на входы блока 3 вычисления синдрома и первую группу входов мультиплексора 8. Вычисленные в блоке 3 разряды синдрома поступают на входы второго дешифратора 4 и входы блока 5 анализа синдрома, а младшие разряды синдрома поступают на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7. В блоке 5 анализа синдрома формируются сигнал готовности информации и сигнал об одиночных и некорректируемых ошибках запоминающего устройства. Сигнал об одиночной ошибке прерывает обработку последующим устройством информации, выводимой из постоянного запоминающего устройства, на время, необходимое для ее исправления. Сигнал о наличии некорректируемой ошибки извещает о неисправности постоянного запоминающего устройства.

На вторую группу входов мультиплексора 8 поступает информация из накопителя 2, просуммированная по mod 2 с младшими разрядами синдрома элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 7.

Если ошибка отсутствует, то на входах первой группы второго дешифратора 4 присутствует исходный (логический 0) уровень. Вследствие этого информация из накопителя 2 через информационные входы первой группы мультиплексора 8 в соответствии с сигналами на информационных входах третьей группы мультиплексора 8 проходит на выходы 9 второй группы устройства. При этом информация минует элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7, чем достигается сокращение времени на выходе информации из накопителя на время задержки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Блок 5 анализа синдрома формирует сигнал об отсутствии ошибок и возможности дальнейшей обработки. В случае наличия ошибок, поддающихся исправлению, в дешифраторе 4 определяется местоположение ошибки, сигнал об этом в виде уровня логической 1 поступает на один из входов третьей группы мультиплексора 8, на выходы 9 второй группы устройства проходит исправленная

информация, поступившая на вторую группу информационных входов мультиплексора 8, причем та часть слова накопителя, которая определена адресом второй группы

адресных входов устройства. Сигнал об одиночной ошибке устройства, формируемый блоком 5 анализа синдрома, затягивает считывание информации, заставляя последующие устройства дождаться ее исправления.

При наличии ошибок, исправить которые постоянное запоминающее устройство не может, блоком 5 анализа синдрома формируется сигнал некорректируемой ошибки. Второй дешифратор 4 формирует

на выходе сигналы уровня логического 0, и на выход 9 устройства проходит информация в том виде, в каком она была считана из накопителя 2. Обмен происходит в максимально возможном для устройства темпе.

Таким образом, быстродействие устройства в режиме работы без ошибок увели- чивается, так как информация из накопителя попадает на выход устройства через группу входов мультиплексора, минуя

элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

Постоянное запоминающее устройство может найти широкое применение в аппаратуре с высокой степенью надежности.

Формула изобретения

Постоянное запоминающее устройство с коррекцией ошибок, содержащее первый дешифратор, адресные входы которого являются первой группой адресных входов устройства, накопитель, адресные входы которого соединены с выходами первого дешифратора, блок вычисления синдрома, информационные входы которого соединены с выходами накопителя, второй дешифратор,

первая группа адресных входов которого соединена с первой группой выходов блока вычисления синдрома, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, мультиплексор, адресные входы которого являются второй

группой адресных входов устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок анализа синдрома, информационные входы которого соединены с первой группой выходов блока вычисления синдрома, выходы блока анализа синдрома являются первой группой выходов устройства, выходы накопителя соединены с первой группой информационных входов мультиплексора и

первой группой информационных входов группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторая группа выходов блока вычисления синдрома соединена с второй группой информационных входов группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. выходы группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены сгруппа адресных входов второго дешифра- второй группой информационных входовтора соединена с адресными входами нуль- мультиплексора, выходы второго дешифра-типлексора, выходы мультиплексора тора соединены с третьей группой инфор-являются второй группой выходов устройст- мационных входов мультиплексора вторая5 ва.

54

JTl

55

55

50

12

Ґ6

S3

57

54

Г

в

11

№

S3

SB

S7

54

SO

S3

8

12

H

13

/(мультиплексору

Ло адресным дходам второй группы уе/яройс/пба

| В.К.Копелько | |||

| В.В.Лосев Надежное хранение информации в полупроводниковых запоминающих устройствах | |||

| М | |||

| : Радио и связь, 1986, с | |||

| Приспособление для воспроизведения изображения на светочувствительной фильме при посредстве промежуточного клише в способе фотоэлектрической передачи изображений на расстояние | 1920 |

|

SU172A1 |

| Постоянное запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1317482A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-04-15—Публикация

1988-08-02—Подача