1

Изобретение относится к области запоминающих устройств и может быть ио пользовано в автоматике и вычислительг-. ной технике.

Известны устройства для корреюаии информации в блоке постоянной памяти

И и и.

в одном из известных устройств применяются методы аппаратурной и временной избыточности Щ.

Недостатком этого устройства является то, что примене1 не методов аппаратурной и временной избыточности не обеспечивает коррекцию информации по любому адресу с полной заменой содержания всего информационного слова в постоянном запоминающем устройстве в реальном масштабе Временн.

Из известных устройств наиболее близким техническим решением к изобретению является устройство, содержащее первый блок памяти, логический блок, первую и вторую группы элементов И, управляющую и информаиионнные шины,

группы адресных шин, шины ввода, причем выходы логического блока подключены к одним из входов элементов И, другие входы элементов И первой и второй групп соединены соответствоано с информационными шинами и выходами первого блока памяти, а выходы - соответственно со входами элементов ИЛИ, выходы которых подключены к вькодам устройства, первый вход первого блока

10 памяти подключен к управляющей шине

И.

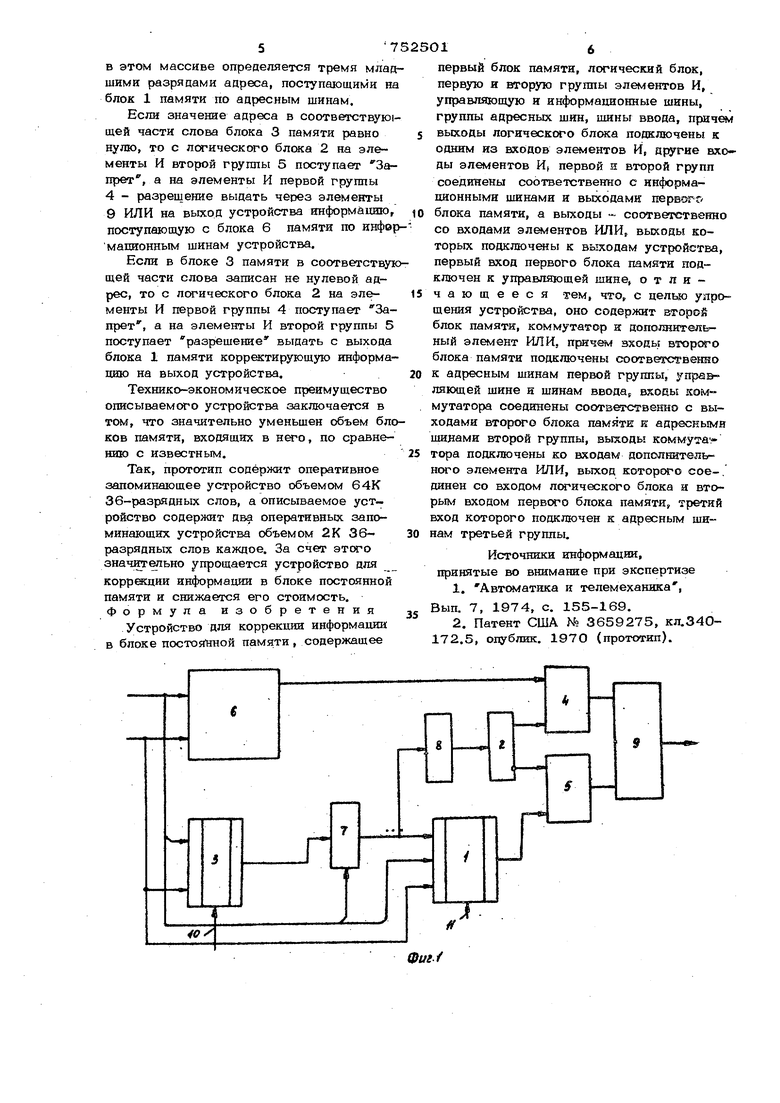

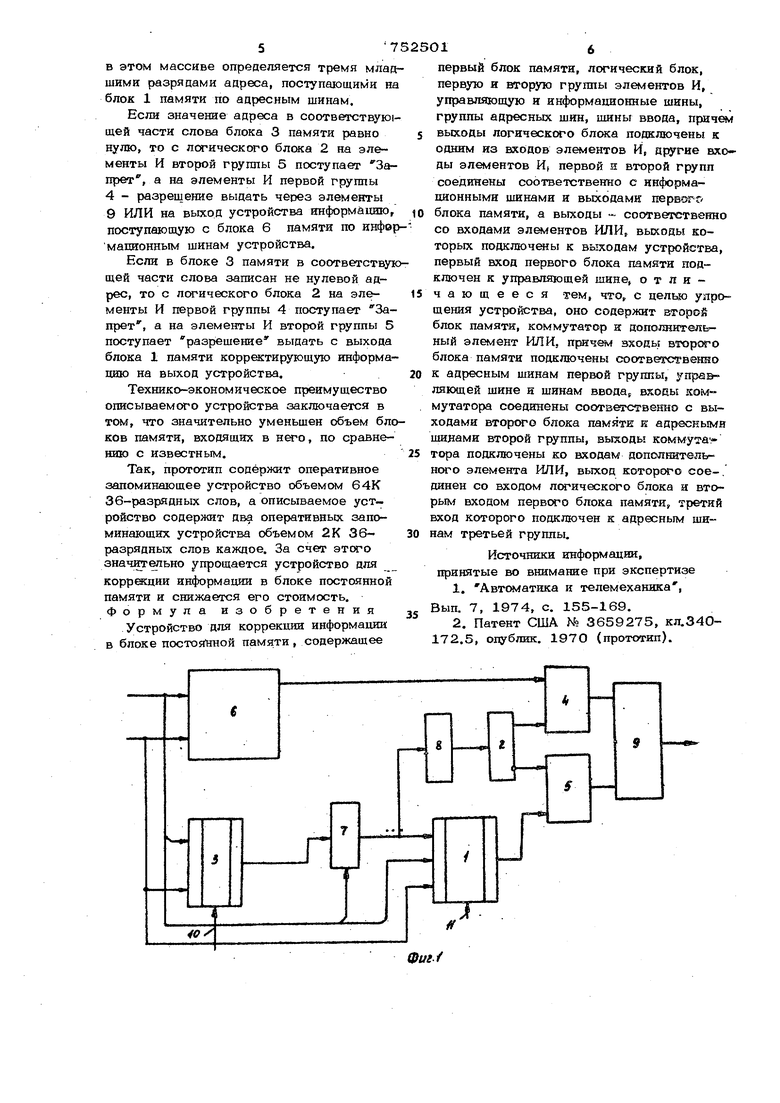

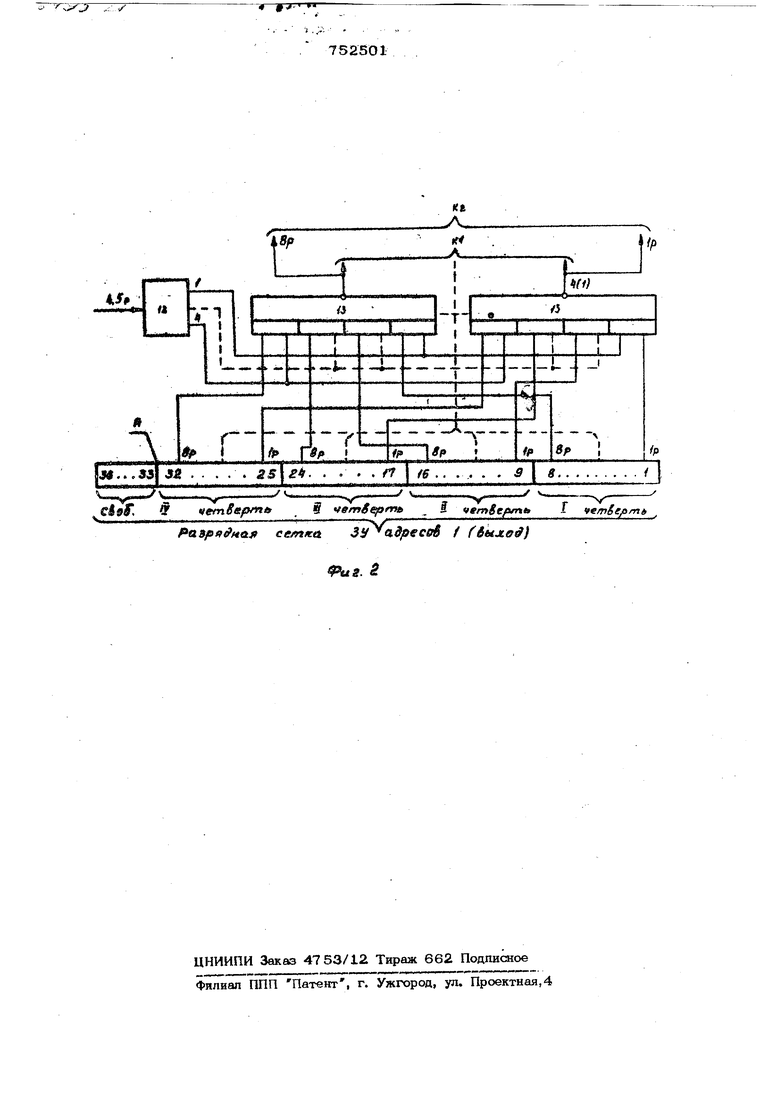

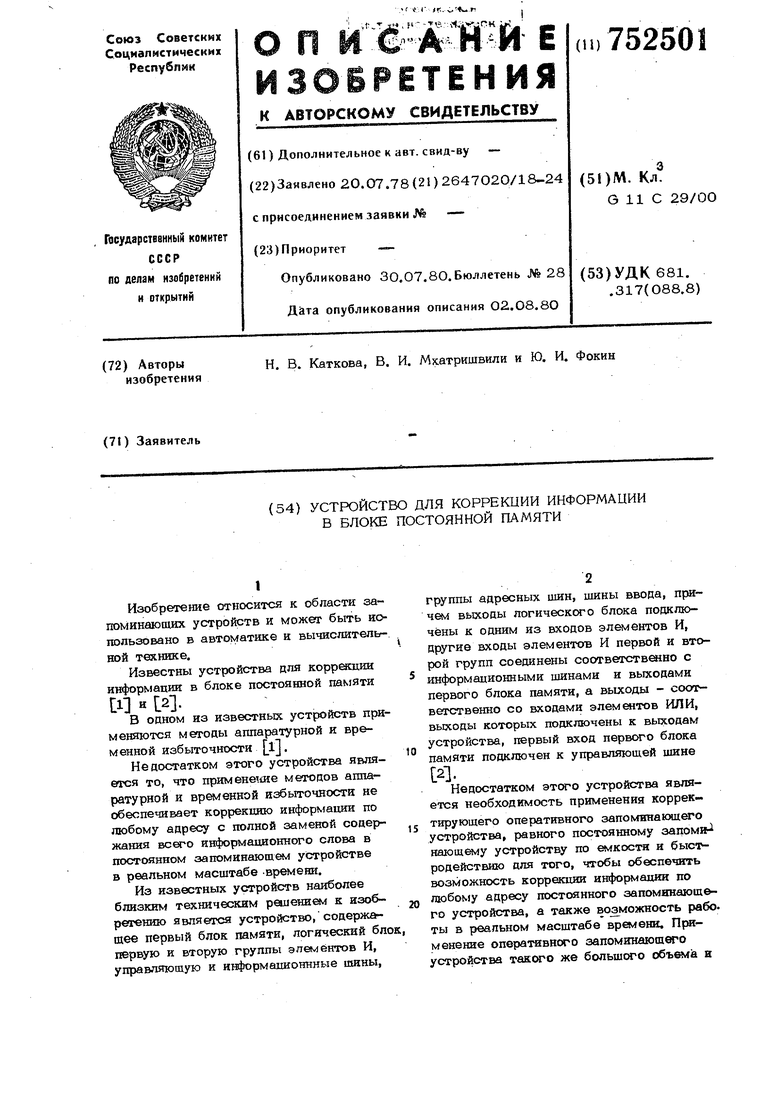

Недостатком этого устройства является необходимость применения корректирующего оперативного запоминающето

15 устройства, равного постоянному запомни нающему устройству по емкости и быстродействию для того, чтобы обеспечить возможность коррекции информации по любому адресу постоянного запоминающе20го устройства, а также возможность рабо. ты в реальном масштабе времени. Применение оперативного запоминающего устройства TaKOTo же большого объема и быстродейсугвия, как современные постоянные запоминающие -устройства, является т®сничес1Ш сложным и дорогостоящим. Цель изобретения - упрощение устройства для коррекции информашга в блоке постоя1шой памяти при обеспечешо коррегцш слов по любому адресу постоянного запоминающего устройства при работе Б реальном масштабе времени. Поставленная цель достигается тем, что устройство содержит второй блок памяти, коммутатор и дополнительный элемент ИЛИ, причем входы второго бло ка памяти подключены соответственно к адресным шинам первой группы, управляющей шине и шинам ввода, входы коммутатора соединены сооа ветственно с выходами второго блока памяти и адресными шинами второй группы, выходы коммутатора подключены ко входам дополнительного элемента ИЛИ, выход которого соединен со входом логическЪго блока и вторым входом первого блока памяти, третий вход которого подключен к адресным шинам третьей группы. На фиг. 1 изобра чена функциональная блок-схема описываемого устройства; на фйг. 2 - блок-схема коммутатора. Устройство содерлогт Сфиг„ 1) первый блок 1 памяти, логический блок 2, второй блок 3 памяти, первую 4 и вторую 5 группы элементов И. Корректируемый блок 6 постоянной памяти подключен к aapecHbSM; информагхяонным и управляющ шннам устройства, содержащего также в .оммутатор 7, дополнЕтельный элемент ИЛИ и элементы 9 ИЛИ. Входы второго блока 3 памяти подключены со1зтветственно к адресным шинам первой группы, управляющей шине и шинам 10 ввода, служащим для ввода адресов. Входы коммутатора 7 соединен соответственно с выходами второго блока 3 памятя и адресными шинами второ группы, а выходы коммутатора 7 подключены ко входам дополнительного эле мента 8 ИЛИ и вторым входам первого блока 1 памяти, первый вход которого подключен к управляющей шине, третий вход - к адресным шинам третьей групп и четвертый вход - к шинам 11 ввода, служащим для подачи информации. Выхо дополнительного элемента 8 ИЛИ соединен со ВХОДОМ логического блока 2, вы ходы которого подключены к одним из входов элементов И первой 4 и второй групп, другие входы которых соединены соответственно с информагшонными шинами и выходами первого блока 1 памяти, а выходы - соответственно со входами элементов 9 ИЛИ, выходы которых подключены к выходам устройства. Комму;гатор 7 содержит (фиг. 2) дешифратор 12 и элементы 13 И-ИЛИ-НЕ. Здесь изображен также выходной регистр 14 блока 3 памяти, Вход дешифратора 12 является входом коммутатора 7 и подключен к адресным шинам второй группы., а выходы дешифр тора соединены соответственно с одними из входов каждого элемента 13 И-ИЛИ-НЕ, к другим Входам которых подключены выходы выходного регистра 14 блока 3 памяти. Устройство работает следующим образом. Работа устройства рассматривается на примере коррекции информации блока постоянной памяти объемом 2 тридцатишестиразрядных слов при необходимости корректировать до 256 массивов, состоящих каждый из восьми слов, при этом блоки 1 и 3 памяти (фиг. 1) устройства , должны иметь объем 2 тридцатишестиразрядных слов. Во втором блоке 3 памяти записываются адреса корректируемых массивов, причем каждое слово содержит четыре восьмиразрядных адреса (каждому адресу массива соответствует определенная часть слова), В первом блоке 1 памяти записывается информация, содержащаяся в массивах, состоящих из восьми слов, причем внутри массива слова, не подлежащие коррекции, повторяются без изменения, а в словах, подлежащих коррекции, записывается соответствующая корректирующая информация. На адресные и управляющую шины уст;.ройства и одновременно на корректируемый блок 6 постоянной памяти подаются код адреса и сигнал обращения. При этом параллельно поступают на первый блок 1 памяти младшие разряды адреса (1р, 2р, Зр), на коммутатор 7 - следующие два разряда (4р, 5р) адреса и на второй блок 3 памяти - остальные старшие разряды (бр, ...... 1бр) адреса. Во втором блоке 3 памяти в соответствии со значениями старших разрядов адреса выбирается ело во, при этом коммутатор 7 в соответствии со значениями четвертого и .пятого разрядов адреса выбирает соответствующую часть этого слова, таким образом определяется адрес корректируемого массива в в блоке 1 памяти. Соответствующее слово в этом массиве определяется тремя мпа шими разрядами адреса, поступающими н блок 1 памяти по адресным шинам. Если значение адреса в соответствую щей части слова блока 3 памяти равно нулю, то с логического блока 2 на элементы И второй группы 5 поступает Запрет, а на элементы И первой группы 4 - разрешение выдать через элементы 9 ИЛИ на выход устройства информацию/ поступающую с блока 6 памяти по янфв маюионным шинам устройства. Если в блоке 3 памяти в соответствую щей части слова записан не нулевой адрес, то с логического блока 2 на элементы И первой группы 4 поступает Запрет, а на элементы И второй группы 5 поступает разрешение выдать с выхода блока 1 памяти корректирующую информацию на выход устройства. Технико-экономическое преимущество описываемого устройства заключается в том, что значительно уменьшен объем бло ков памяти, входящих в него, по сравнению с известным. Так, прототип содержит оперативное запоминающее устройство объемом 64К 36-разрядных слов, а описываемое устройство содержит два оперативных запоминающих устройства объемом 2К 36разрядных слов каждое. За счет значительно упрощается устройство для коррекции информации в блоке постоянной памяти и снижается его стоимость. Формула изобретения Устройство для коррекции информации в блоке ПОСТОЯ1ШОЙ памяти , содержащее О16 первый блок памяти, логический блок, первую и вторую группы элементов И, управляющую и информационные шины, группы адресных шин, шины ввода, приче г выходы логического блсжа подключены к одним из входов элементов И, другие входы элементов И, первой и второй групп соединены соответственно с информационными шинами и выходами первогг блока памяти, а выходы - соответственно со входами элементов ИЛИ, вькоды которых подключшы к выходам устройства, первый вход первого блока памяти подключен к управляющей шине, отличающееся тем, что, с целые упрощения устройства, оно содержит второй блок памяти, коммутатор н йопогаштельный элемент ИЛИ, причем входы второго блока памяти подключены соответственно к адресным шинам первой группы, упра&ляющей шине и шинам ввода вхоцы коммутатора соединены соответственно с выходами второго блока памяти к адресными шинами второй группы, выходы коммута.тора подключены ко входам дополнительного элемента ИЛИ, выход которого сое-. динен со входом логического блока а вторым входом первого блока памяти, третий ход которого подключен к адресным шиам третьей группы. Источники информации, принятые во внимание при экспертизе 1. Автоматика и телемеханика. ып. 7, 1974, с. 155-169. 2.Патент США № 3659275, кл.340172.5, опублик. 197О (прототип).

752501

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции информации вблОКАХ пОСТОяННОй пАМяТи | 1979 |

|

SU849308A1 |

| Запоминающее устройство с коррекцией информации | 1986 |

|

SU1392596A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Запоминающее устройство с коррекцией программы | 1981 |

|

SU963108A2 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Постоянное запоминающее устройство сКОРРЕКциЕй иНфОРМАции | 1979 |

|

SU849304A1 |

| Постоянное запоминающее устройство с самоконтролем | 1985 |

|

SU1285538A1 |

Paafuf Httjf cemic& Зуо.&ресоё / (былв)

-Яиг. 5

Авторы

Даты

1980-07-30—Публикация

1978-07-20—Подача