Не

2

sl

О

о

СП

Изобретение относится к вычислительной и измерительной технике и может быть использовано в составе управляющих и измерительных систем, обрабатывающих первичную частотную информацию.

Цель изобретения - повышение точности.

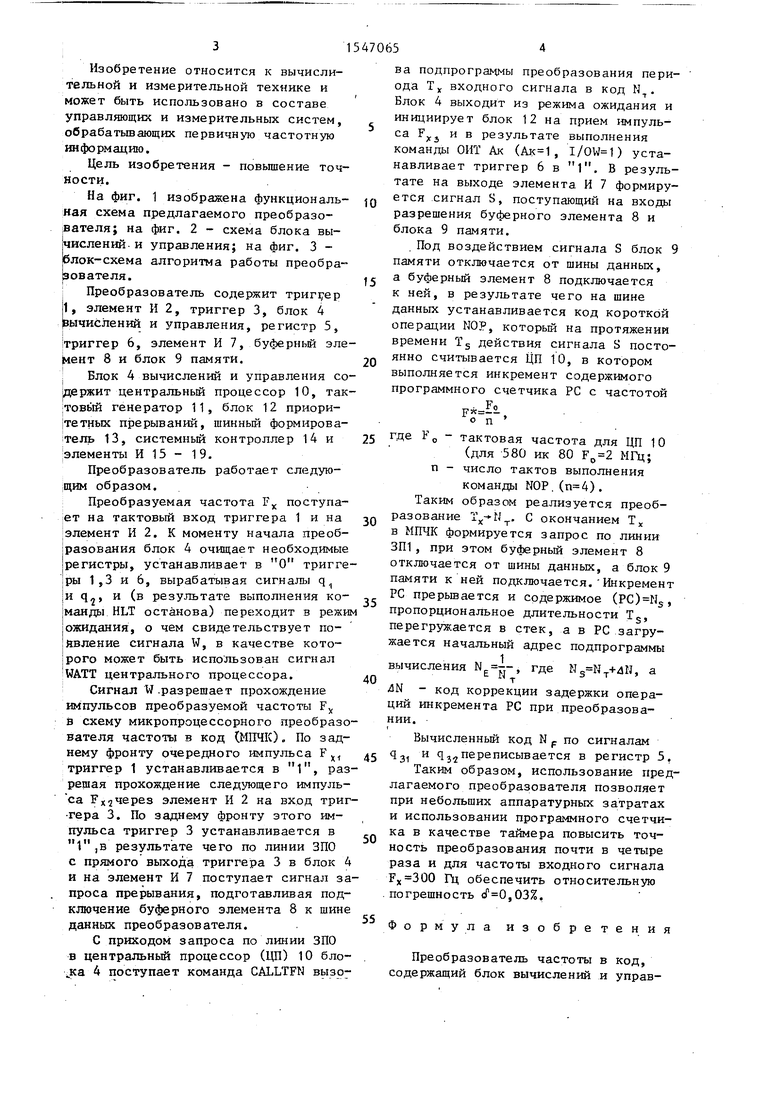

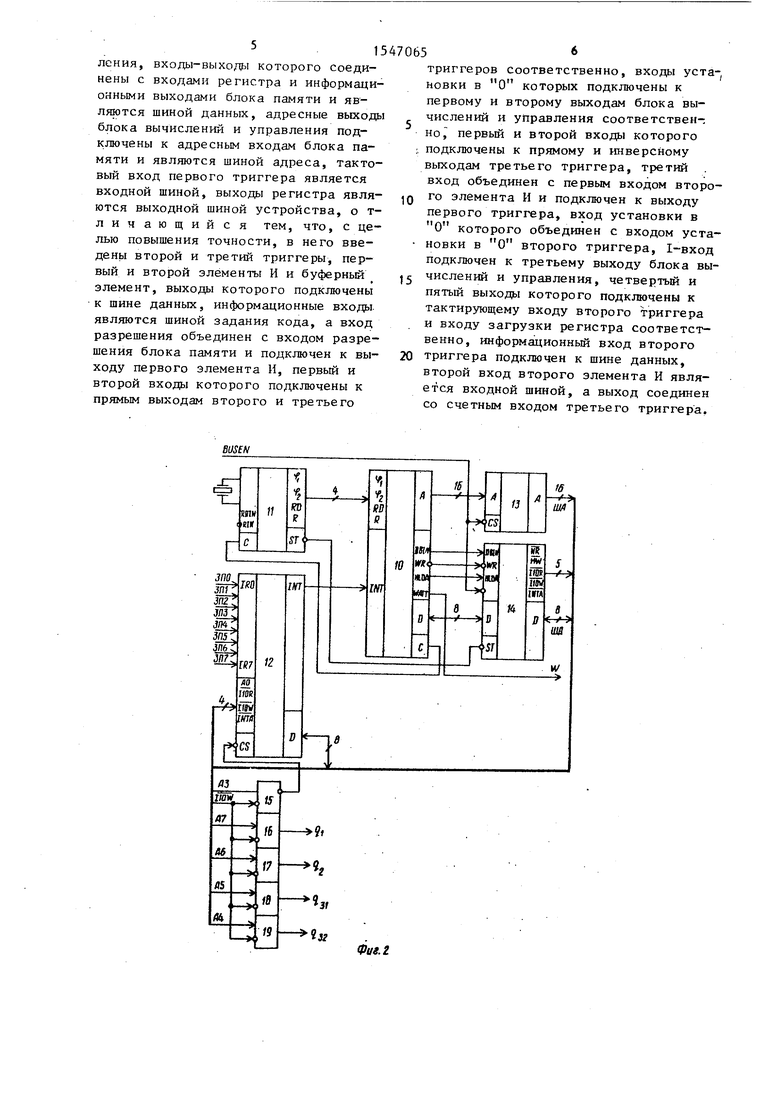

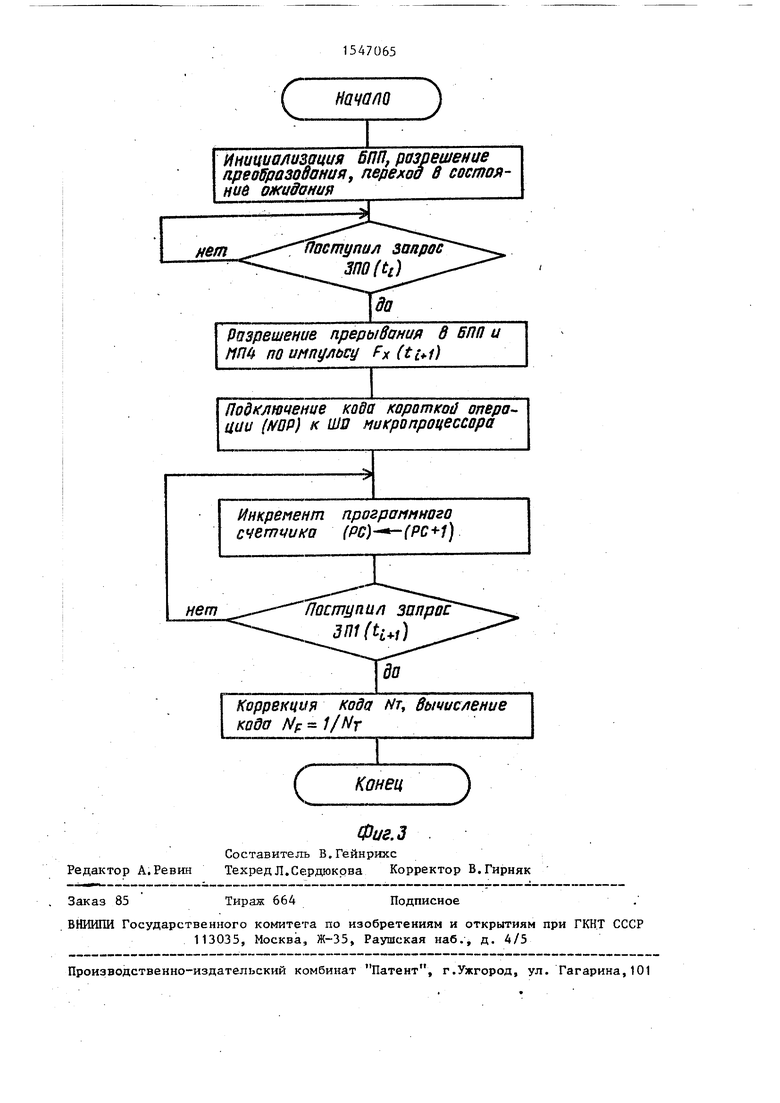

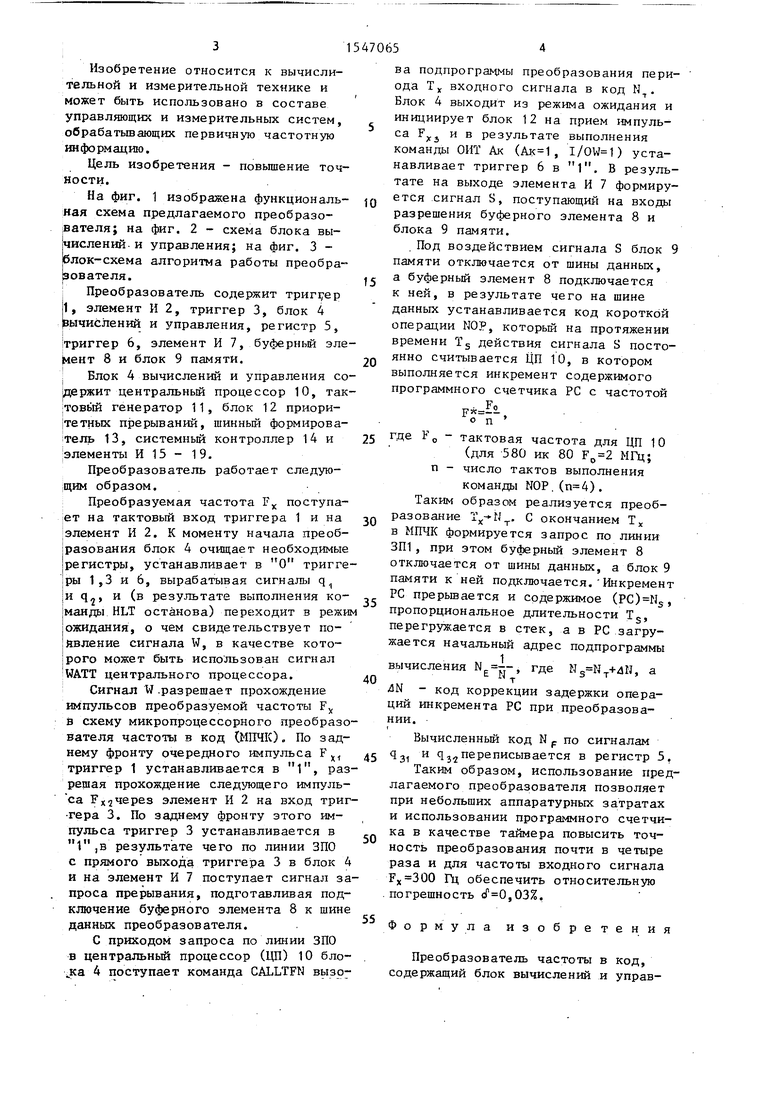

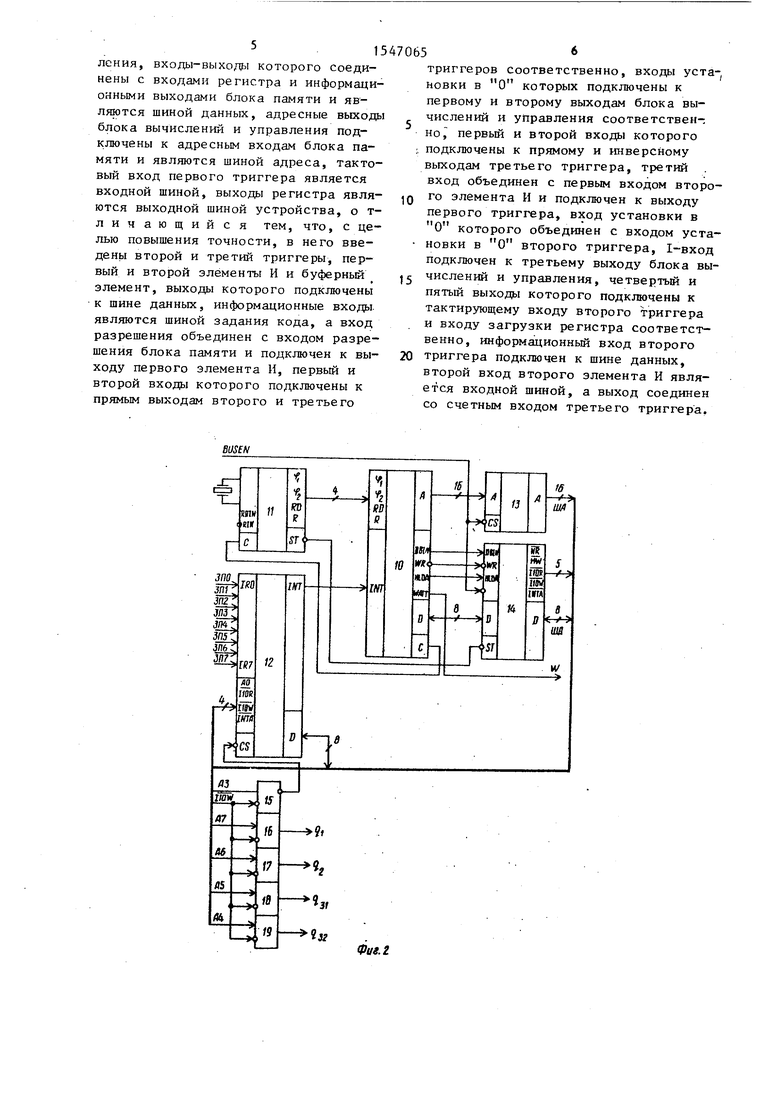

На фиг. 1 изображена функциональная схема предлагаемого преобразователя; на фиг. 2 - схема блока вычислений, и управления; на фиг. 3 - блок-схема алгоритма работы преобразователя.

Преобразователь содержит триггер J1, элемент И 2, триггер 3, блок 4 рычислений и управления, регистр 5, триггер 6, элемент И 7, буферный эле- Иент 8 и блок 9 памяти.

Блок 4 вычислений и управления содержит центральный процессор 10, тактовый генератор 11, блок 12 приоритетных прерываний, шинный формирователь 13, системный контроллер 14 и элементы И 15 - 19.

Преобразователь работает следующим образом.

Преобразуемая частота Fx поступает на тактовый вход триггера 1 и на элемент И 2. К моменту начала преобразования блок 4 очищает необходимые регистры, устанавливает в О триггеры 1 ,3 и 6, вырабатывая сигналы q и q,, и (в результате выполнения ко- манды HLT останова) переходит в режим ожидания, о чем свидетельствует появление сигнала W, в качестве которого может быть использован сигнал WATT центрального процессора.

Сигнал W.разрешает прохождение импульсов преобразуемой частоты Fx в схему микропроцессорного преобразователя частоты в код (МПЧК). По заднему фронту очередного импульса Fx, триггер 1 устанавливается в 1, разрешая прохождение следующего импуль- са Гх2через элемент И 2 на вход триггера 3. По заднему фронту этого импульса триггер 3 устанавливается в 1 ,в результате чего по линии ЗПО с прямого выхода триггера 3 в блок 4 и на элемент И 7 поступает сигнал запроса прерывания, подготавливая подключение буферного элемента 8 к шине данных преобразователя.

С приходом запроса по линии ЗПО в центральный процессор (ЦП) 10 бло- .ка 4 поступает команда CALLTFN вызо

0

5

5

0

35 до

45 0

0

55

ва подпрограммы преобразования периода Тх входного сигнала в код NT. Блок 4 выходит из режима ожидания и инициирует блок 12 на прием импульса Fv, ив результате выполнения команды ОПТ Ак (, ) устанавливает триггер 6 в 1. В результате на выходе элемента И 7 формируется сигнал S, поступающий на входы разрешения буферного элемента 8 и блока 9 памяти.

Под воздействием сигнала S блок 9 памяти отключается от шины данных, а буферный элемент 8 подключается к ней, в результате чего на шине данных устанавливается код короткой операции NOP, который на протяжении времени Ts действия сигнала S постоянно считывается ЦП 10, в котором выполняется инкремент содержимого программного счетчика PC с частотой

О П

где F0 - тактовая частота для ЦП 10

(для 580 ик 80 МГц; п - число тактов выполнения

команды ШР.(). Таким образом реализуется преобразование . С окончанием Т в МПЧК формируется запрос по линии ЗП1, при этом буферный элемент 8 отключается от шины данных, а блок 9 памяти к ней подключается. Инкремент PC прерывается и содержимое (PC)NS, пропорциональное длительности Ts, перегружается в стек, а в PC загружается начальный адрес подпрограммы

вычисления , где Ns NT+4lI, a

UN - код коррекции задержки операций инкремента PC при преобразовании.

Вычисленный код NF по сигналам q и qJ2переписывается в регистр 5.

Таким образом, использование предлагаемого преобразователя позволяет при небольших аппаратурных затратах и использовании программного счетчика в качестве таймера повысить точность преобразования почти в четыре раза и для частоты входного сигнала Гц обеспечить относительную погрешность ,03%.

Формула изобретения

Преобразователь частоты в код, содержащий блок вычислений и управлсния, входы-выходы которого соединены с входами регистра и информационными выходами блока памяти и являются шиной данных, адресные выходы блока вычислений и управления подключены к адресным входам блока памяти и являются шиной адреса, тактовый вход первого триггера является входной шиной, выходы регистра являются выходной шиной устройства, о т- личающийся тем, что, с целью повышения точности, в него введены второй и третий триггеры, первый и второй элементы И и буферный элемент, выходы которого подключены к шине данных, информационные входы являются шиной задания кода, а вход разрешения объединен с входом разрешения блока памяти и подключен к выходу первого элемента И, первый и второй входы которого подключены к прямым выходам второго и третьего

0

триггеров соответственно, входы установки в О которых подключены к первому и второму выходам блока вычислении и управления соответственно, первый и второй входы которого подключены к прямому и инверсному выходам третьего триггера, третий вход объединен с первым входом второго элемента И и подключен к выходу первого триггера, вход установки в О которого объединен с входом установки в О второго триггера, 1-вход подключен к третьему выходу блока вычислений и управления, четвертый и пятый выходы которого подключены к тактирующему входу второго триггера и входу загрузки регистра соответственно, информационный вход второго триггера подключен к шине данных, второй вход второго элемента И является входной шиной, а выход соединен со счетным входом третьего триггера.

С

начало

)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Устройство для сопряжения микро-ЭВМ с табло индикации | 1986 |

|

SU1376090A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ (ВАРИАНТЫ) И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (ВАРИАНТЫ) | 2008 |

|

RU2402025C2 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

Изобретение относится к вычислительной и измерительной технике и может быть использовано в составе управляющих и измерительных систем, обрабатывающих первичную частотную информацию. Цель изобретения - повышение точности. Указанная цель достигается за счет того, что в устройство, содержащее блок 4 вычислений и управления, триггер 1, регистр 5 и блок 9 памяти, введены триггеры 3 и 6, элементы И 2 и 7 и буферный элемент 8. Введение этих элементов и использование программного счетчика центрального процессора в качестве таймера для формирования кода периода позволило синхронизировать начало преобразования с началом периода входного сигнала, а также увеличить частоту "заполнения" измеряемого интервала, что повышает точность преобразования. 3 ил.

Инициализация йПП, разрешение преобразования, переход В состояние ожидания

Разрешение прерывания в БЛП и #Я4 по импульсу Fx (ti+i)

Подключение кода короткой операции (NOP) к ШВ микропроцессора

Инкремент программного счетчика (РС)-(РС+1)

Поступил запрос 3ll1(tM)

Коррекция кода /Yr, вычисление кода N - 1/Nr

С

Редактор А.Ревин

Фиг.З

Составитель В.Гейнрихс

Техред Л. Сердюкова Корректор В.Гирняк

Заказ 85

Тираж 664

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Конец

J

Подписное

| Ыелкунов Н.Н., Дианов А.П | |||

| Универсальный одноплатный микроконтроллер | |||

| - Микропроцессорные средства и системы, 1986, Р 5, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Лонтюхин В.Н | |||

| Функциональный преобразователь частоты в код на основе микропроцессора | |||

| - Известия вузов, Приборостроение, 1985, № 4, с | |||

| Гальванический элемент | 1922 |

|

SU540A1 |

Авторы

Даты

1990-02-28—Публикация

1988-01-18—Подача