Изобретение относится к вычислительной технике, а именно к устройствам функционального контроля логических узлов.

Устройства функционального контро- ля позволяют определить правильность функционирования логического узла . посредством определенных входных воздействий и анализа соответствующих выходных реакций. Совокупность двоичных значений входного воздействия и эталона выходной реакции, соответствующей этим значениям, называется тест-набором. Кроме тест-наборов тестовая информация включает служебные наборы, определяющие режим работы выходного формирователя устройства для каждого сигнального контакта соединителя печатной платы логического узла. Наборы, составляющие слова тестовой информации, могут иметь переменное число разрядов в зависимости от

числа сигнальных контактов в соединителе печатной платы конкретного логического узла, подлежащего контролю. Максимальное число разрядов равно максимальному числу используемых сигнальных контактов.

В процессе контроля наборы тестовой информации временно или постоянно хранятся в блоке запоминания, который размещается между блоком сопряжения устройства для функционального контроля с управляющей ЭВМ и блоком формирования входных и анализа выходных сигналов контролируемого узла.

Цель изобретения - сокращение тестовой информации, вносимой в узел памяти.

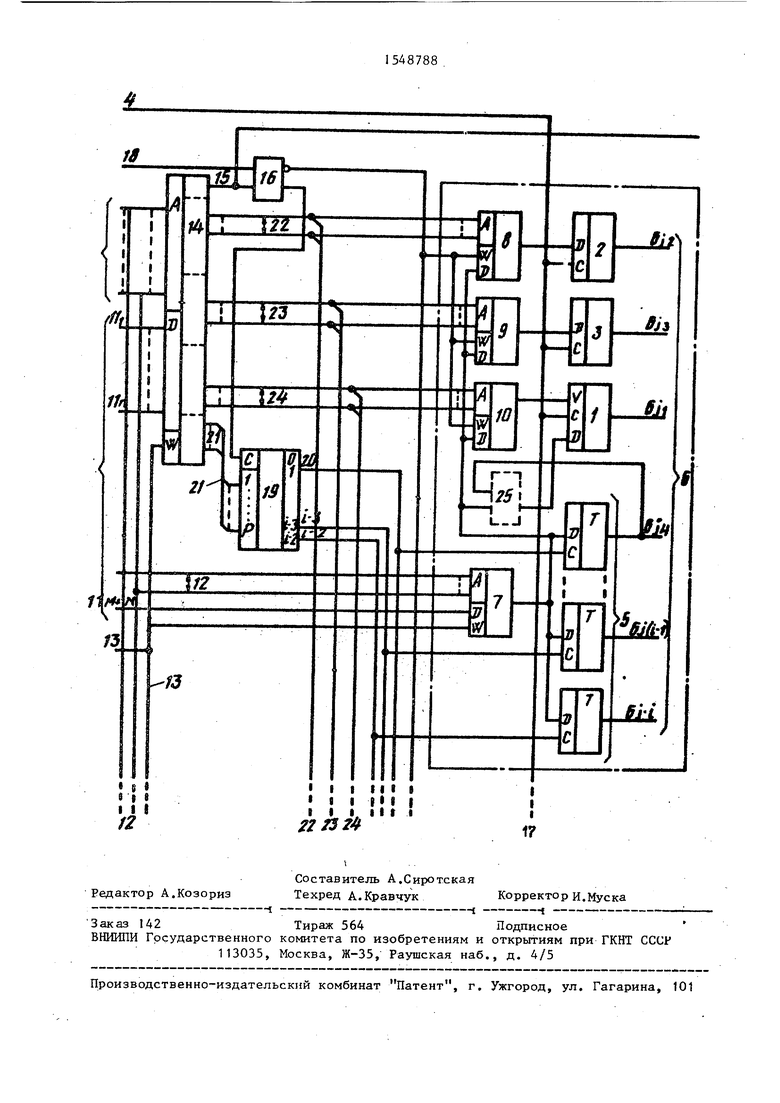

На чертеже приведена функциональная схема узла.

Узел содержит регистр 1, первую группу регистров 2 и 3, первый вход 4 задания режима работы узла, вторую

(Л

с

ел

4Ь

00

1

00 00

группу регистров 5, выходы 6 узла, третий блок 7 памяти, первый 8, второй 9 и пятый 10 блоки памяти, вторую группу информационных входов 11 узла, адресных входов 12 узла, вход 13 записи, четвертый блок 14 памяти, выход 15 признака смены тестового слова четвертого блока памяти элемент И 16, выход 17 признака тестового слова узла, второй вход 18 задания режима работы8 дешифратор 19,, первую группу информационных входов 20 узла, выходы 21 поля адреса четвертого блока памяти, группу выходов 22-24 четвертого блока памяти и группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 25.

В регистре 1 временно запоминается тест-набор. В регистре 2 временно запоминается служебный набор, задающий входные и выходные контакты соединителя проверяемого узла на данньй шаг тестирования. В регистре 2 временно запоминается служебный набор, задающий выходные контакты, подлежащие контролю в данном шаге тестирования. Регистр 3 часто называют регистром маски выходных контактов.

В группе регистров 5 помещается служебная информация, которая не изменяется в течение всей тестовой программы, и может храниться служебный набор, задающий тип логики контакта, отрицательный (ЭСП) или положительный (ТТЛ). Один регистр из этой группы может определять;, нужно ли подключать к контакту резистор нагрузки. Несколько регистров 5 из группы могут исполь зоваться для задания конкретного импульса из программно-заданной времен ной диаграммы, который подается на данный контакт,, .Один реестр может управлять подключением к заданным контактам цепей- с аналоговыми измерителями и т„п.

Количество регистров определяется характеристиками узла-тестера. Блоки 7 и 14 памяти имеют одинаковое число слов, но различную разрядность. Слово блока 14 памяти несет информацию служебного характера о набрре, находящемся в блоке 7 памяти по тому же адресу. Если с выхода 15 считывается 1 это означает, что синхронно из памяти

Наличие блока 10 памяти дает возможность использовать блок сопряжения узла с ЭВМ в случае, если часть контактов контролируемого узла не используется и т.п. Это позволяет уменьшить длину тест-программы. Для хранения служебного набора, определяющего узел логики, в узел вводится N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 25, входы которых соединены с выходами блока 7 памяти и группы регистра 5, а выход - с D-вхо- дом данных регистра 1.

Узел работает следующим образом. L

На первой фазе заносится синхронно информация в блоки 7 и 14 памяти. При этом строб-сигналы на шины 4 и 18

50

не поступают. Уровень 0 на шине 13

7 считывается служебный набор, кото- 55 Узла обеспечивает благодаря элементу рый направляется в один из блоков 8-и 16 уровень 1 на входах записи блока 8-10 памяти и уровень О на С-вхо- де дешифратора 19. Это означает, что

10 памяти или один из регистров 5 группы.

15

20

,-

-

25

87884

Блок 14 памяти может иметь разрядность, равнук 16 или 32, в то время как блок 7 памяти должен иметь разрядность от 96 до 256 и более (в соответствии с числом контактов контролируемого логического узла). Блоки 7-10 памяти имеют одинаковую разрядность, но разную емкость-по числу слов. Блок памяти 8 имеет небольшую емкость, которая зависят от максимального числа двунаправленных шин у контролируемых узлов и должна вмещать не менее (2 + +1) слов, где а - максимальное число двунаправленных шин, которое может быть у контролируемого узла.

Блок 9 памяти имеет емкость, не превышающую емкость блока 7 памяти, и, главное, что согласно данному решению содержимое блока 9 памяти может быть обновлено на любом этапе тестирования, и он может иметь существенно меньшую емкость, чем емкость блока 7 памяти. Это можно пояснить тем, что .отношение количества тест-наборов к наборам-маскам выходов в любой тест- программе больше единицы. Это соотношение зависит от методики построения (синтеза) контролирующих тестов и изменяется в широких пределах.

Блок 10 памяти, запоминает служебные наборы, которые задают номера тех входных контактов проверяемого логического узла, содержание которых не должно меняться в данном шаге контроля по сравнению с предыдущим шагом. По аналогии можно эти наборы назвать маской входных контактов.

Наличие блока 10 памяти дает возможность использовать блок сопряжения узла с ЭВМ в случае, если часть контактов контролируемого узла не используется и т.п. Это позволяет уменьшить длину тест-программы. Для хранения служебного набора, определяющего узел логики, в узел вводится N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 25, входы которых соединены с выходами блока 7 памяти и группы регистра 5, а выход - с D-вхо- дом данных регистра 1.

Узел работает следующим образом. L

На первой фазе заносится синхронно информация в блоки 7 и 14 памяти. При этом строб-сигналы на шины 4 и 18

30

35

40

45

50

не поступают. Уровень 0 на шине 13

51548788&

блоки 8-10 памяти находятся в режимесчитывается информация, отличная от

Чтение, дешифратор заперт (на выхо- нуля, а на выходах 22-24 - нулевая.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для диагностирования цифровых узлов | 1986 |

|

SU1520517A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

Устройство к вычислительной технике, в частности к устройствам функционального контроля логических узлов. Такие устройства позволяют определить правильность функционирования логического узла посредством определенных входных воздействий и анализа соответствующих выходных реакций. Цель изобретения - сокращение тестовой информации, вносимой в узел памяти. В узел запоминания тестовой информации, имеющий три блока памяти и первую группу регистров, дополнительно введены четвертый и пятый блоки памяти, вторая группа регистров, регистр, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор и элемент И. 1 ил.

дах нули).

Осуществляется запись в блоки 7 и

14памяти с входа 13. Затем адрес увеличивается на 1 и т.д. до полного или частичного заполнения блоков 7 и 14 памяти.

Вторая фаза работы - это перезапись служебных наборов из блока 7 памяти в блоки памяти и регистры 5 группы. Ячейки блоков 8-10 памяти с нулевым адресом для информации не используются. В этой фазе на входы 4 и 18 поступают строб-импульсы, а на шине 13 устанавливается уровень 1, означающий режим Чтение. Кроме того, при перезаписи служабных наборов с выхода

15блока 14 памяти считываются единицы - признак, из блока 7 памяти считывается служебный набор.

Вначале на адресных входах 12 уста20 ся математическими понятиями двоичных 1 и О для различных типов логики. Если контролируемый контакт связан с элементами положительной логики, в соответствующем разряде регистра 5

с соответствующего разряда блока 7, записывается в регистр 1 без инвертирования (для отрицательной логики в ре

навливаются нули. Через определенное

время, равное времени выборки памяти, 25 из группы должен быть записан О. на выходах блоков 7 и 14 памяти ус- В этом случае значение, считываемое танавливается информация, а на выходах одной группы 21-24 - двоичное значение адреса, равное 1, например, на выходах 22. Уровень 1 считывается гистр будет записываться инвертирован- же и с выхода 15. Затем по шине 18 ная информация).

поступает строб-импульс.Если адреса блоков 7 и 14 в каждом

Запись, по которой выходными сиг- шаге увеличиваются на единицу, то ад- налами элемента 16 стробируется дешиф- реса блоков 8-10 устанавливаются про- ратор 19, и сигнал проходят на неза- звольно по информации, считываемой

действованный нулевой выход, так как на входе дешифратора установлены все нули. При этом ни на один из регистров 5 группы не поступит импульс записи. Импульс с прямого выхода элемента И 16 записывает набор с выхода блока 7 памяти в нулевые ячейки блоков 9 и 10 памяти и в первую ячейку блоков 8 памяти. Далее адрес на адресных входах 12 возрастает на 1, а на выходах 22 считывается двойка. Происходит запись второго служебного набора по второму адресу блока 8 и опять по нулевым адресам блоков 9 и 10.

Когда вся нужная информация записывается в блок 8, начинается запись в другую память, например в блок 9 или 10, которая выполняется по тому же алгоритму, но на выходах 22 будут считываться нули, адреса - на выходах- 23 или 24 блока 14 памяти. Если записывается информация в регистры 5 группы, то на выходах 21 блока 14 памяти

с выходов 22-24 блоков 14. Уровень О на выходе 17 указывает, что информация регистров 1, 2, 3 и 5 должна использоваться для тестирования.

40 Тест-наборы и служебные наборы могут считываться и попеременно.

Из работы блока видно, что вся тест-программа может записываться в блоки 7 и 14 методом записи в магадс зинную память. Достаточно в управляющую память задать начальный адрес тестовой программы и количество слов при заданном формате наборов . Это первая причина, экономии тест-информации (не

5Q требуется хранить и передавать адреса).

Кроме того, вместо записи многоразрядных служебных наборов для блоков 8-10 задаются их адреса одним или двумя словами с разрядностью ЭВМ. Причина сокращения тестовой информации вытекает из того, что разновидностей служебных наборов гораздо меньше их количества в тест-программе. Каждый

55

0

Третья фаза работы отличается тем, что считываются тест-наборы и на выходе 15 памяти считываются нули. Дешифратор 19 не стробируется, а все блоки работают в режиме считывания. При изменении адреса на шине 12 информация появляется на выходах блоков 7-10 памяти.

Вначале рассмотрим случай, когда группы элементов 25 нет,

После появления данных на выходах

5 блоков поступает строб-импульс по шине 4 и по С-входам записываются в регистры 2 и 3 данные с выхода блоков 8 и 9. Группа элементов 25 дает возможность составителю теста пользовать0 ся математическими понятиями двоичных 1 и О для различных типов логики. Если контролируемый контакт связан с элементами положительной логики, в соответствующем разряде регистра 5

с соответствующего разряда блока 7, записывается в регистр 1 без инвертирования (для отрицательной логики в реиз группы должен быть записан О. В этом случае значение, считываемое гистр будет записываться инвертирован- ная информация).

шаге увеличиваются на единицу, то ад- реса блоков 8-10 устанавливаются про- звольно по информации, считываемой

с выходов 22-24 блоков 14. Уровень О на выходе 17 указывает, что информация регистров 1, 2, 3 и 5 должна использоваться для тестирования.

0 Тест-наборы и служебные наборы могут считываться и попеременно.

Из работы блока видно, что вся тест-программа может записываться в блоки 7 и 14 методом записи в магас зинную память. Достаточно в управляющую память задать начальный адрес тестовой программы и количество слов при заданном формате наборов . Это первая причина, экономии тест-информации (не

Q требуется хранить и передавать адреса).

Кроме того, вместо записи многоразрядных служебных наборов для блоков 8-10 задаются их адреса одним или двумя словами с разрядностью ЭВМ. Причина сокращения тестовой информации вытекает из того, что разновидностей служебных наборов гораздо меньше их количества в тест-программе. Каждый

5

Тест-набор для данного узла снабжается служебным словом, несущим информацию о служебных наборах, которые должны синхронно использоваться с данным .тест-набором. Это существенно облегчает составление, отладку . и корректировку тестов.

Дополнительные функциональные возможности появляются при введении па- мяти маски входных контактов, например узел может последовательно принимать хранимые тестовые наборы из ЭВМ, а принимать тестовые последовательности, задаваемые алгоритмическим re- йератором тестов на определенные заранее контакты контролируемого узла без изменения информации на других Контактах этого узла.

Формула изобретения

Узел запоминания тестовой информации, содержащий три блока памяти, первую группу регистров, причем выходы регистров первой группы являются пер вой группой выходов узла, синхровхо- ды регистров первой группы соединены с первым входом задания режима работы узла, группа выходов первого и второго блоков памяти соединена с пер- вой и второй группами информационных входов регистров первой группы, адресные входы и вход записи третьего блока памяти соединены с адресными входами и входом записи узла соответственно, группа информации входов третьего блока памяти соединена с первой группой информационных входов, отличающийся тем, что, с целью сокращения объема тестовой информации, вносимой в узел, в него дополнительно введены четвертый и пятый блоки памяти, вторая группа регистров регистр, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор и элемент И, причем вторая группа информационных входов узла соединена с группой информационных входов четвертого блока памяти,

0

выход признака смены тестового слова которого соединен с первым входом .. элемента И и с выходом признака смены тестового слова узла, второй вход элемента И соединен с вторым входом задания режима работы узла, прямой выход элемента И соединен с входом синхронизации дешифратора, выходы которого соединены с входами синхронизации регистров второй группы и являются выходами поля адреса узла, выходы третьего блока памяти соединены с информационными входами регистров второй группы, с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы и с информационными входами первого, второго и пятого блоков памяти, выход пятого блока памяти соединен с входом разрешения регистра, вход синхронизации и информационные входы которого соединены с первым входом задания режима работы узла и с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соответственно, выходы первой группы регистров второй группы соединены с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и являются выходами поля тест-набора узла, группа выходов поля типа логики которого соединена с второй группой выходов регистров второй группы, выходы регистра соединены с выходами поля признака эталона узла, выходы поля признаков входов (выходов) узла, первая, вторая, третья и четвертая группы выходов четвертого блока памяти соединены с информационными входами дешифратора, и с адресными входами первого, второго и пятого блоков памяти соответственно, инверсный выход элемента И соединен с входами записи первого, второго и пятого блоков памяти, вход записи узла соединен с входом записи четвертого блока памяти, группа адресных и группа информационных входов которого соединены с группами адресных и информационных выходов узла.

| УСТРОЙСТВО для ПРОВЕРКИ ФУНКЦИОНИРОВАНИЯ ЛОГИЧЕСКИХ СХЕМ | 0 |

|

SU354415A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| | Патент Великобритании № 1513731, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-03-07—Публикация

1986-01-13—Подача