Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля микропроцессорных устройств, и может быть использовано в процессе разработки, производства и эксплуатации микропроцессорных систем.

Цель изобретения - повышение полноты и сокращение времени контроля за счет формирования случайных последовательностей команд с детерминированными или случайными операндами.

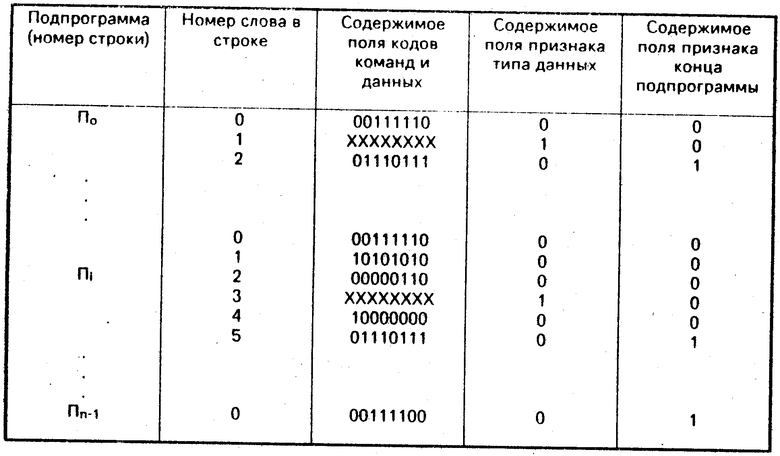

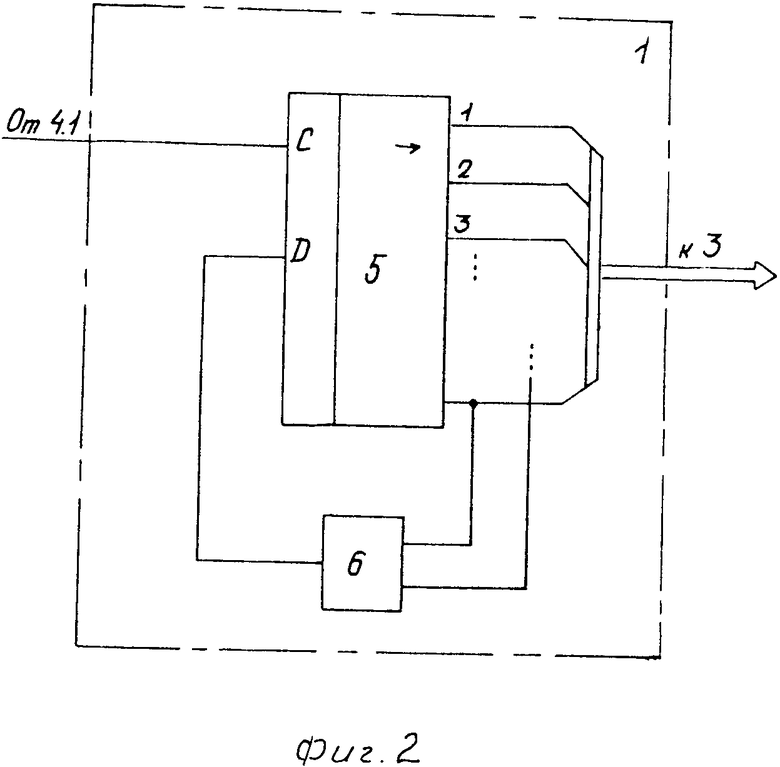

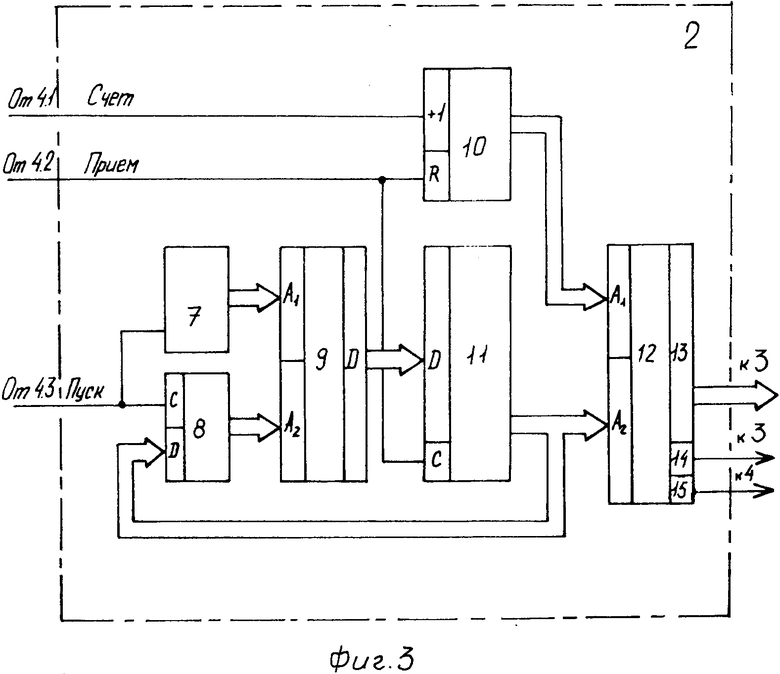

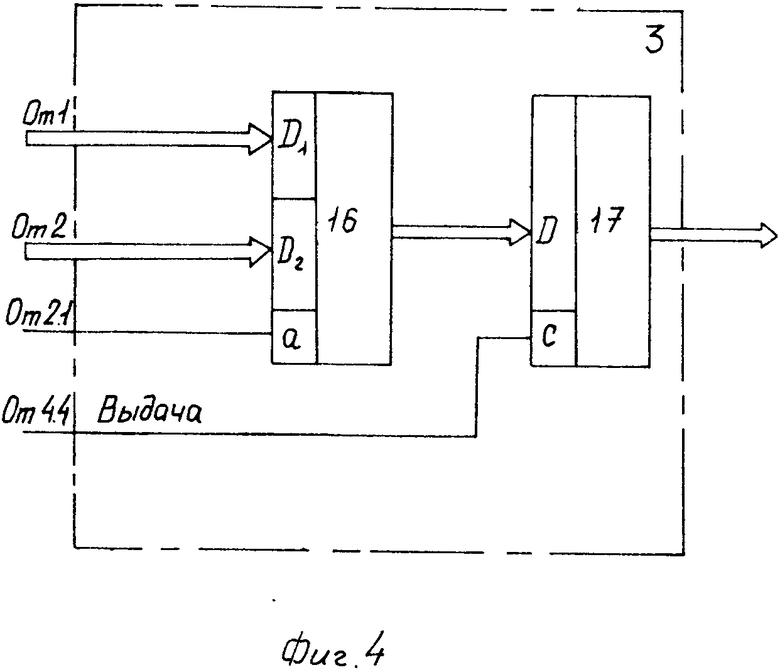

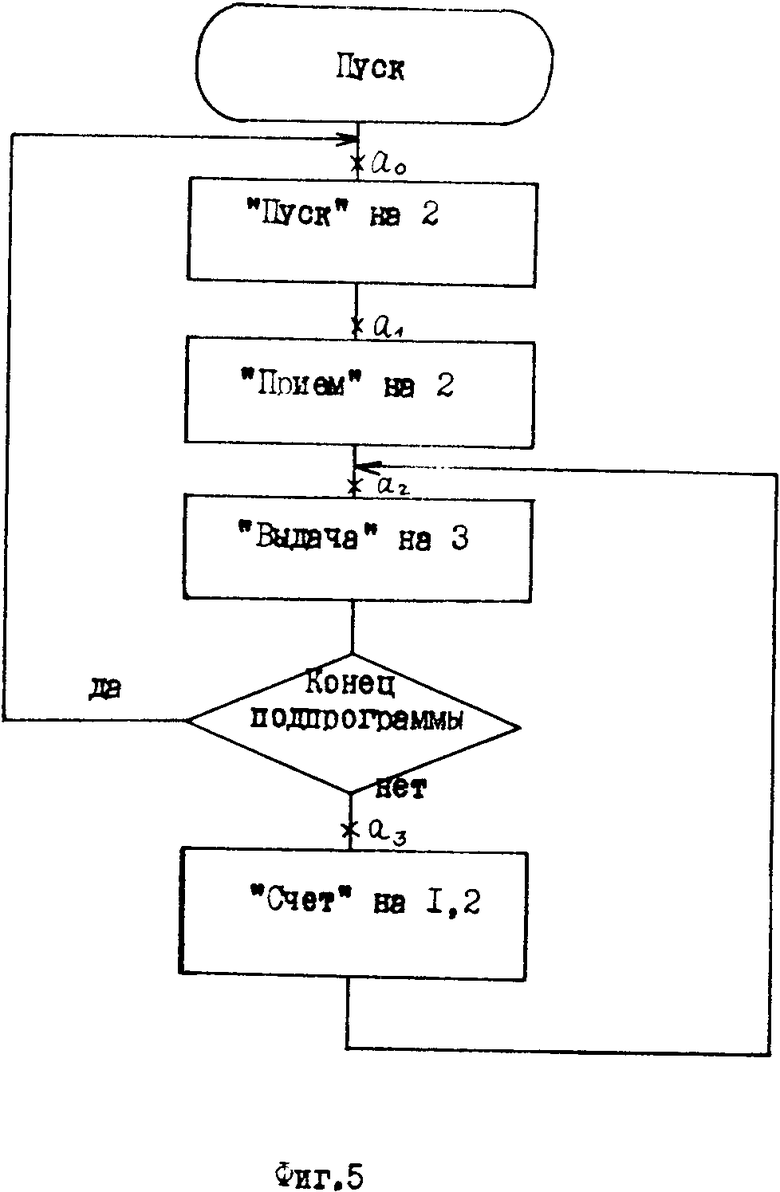

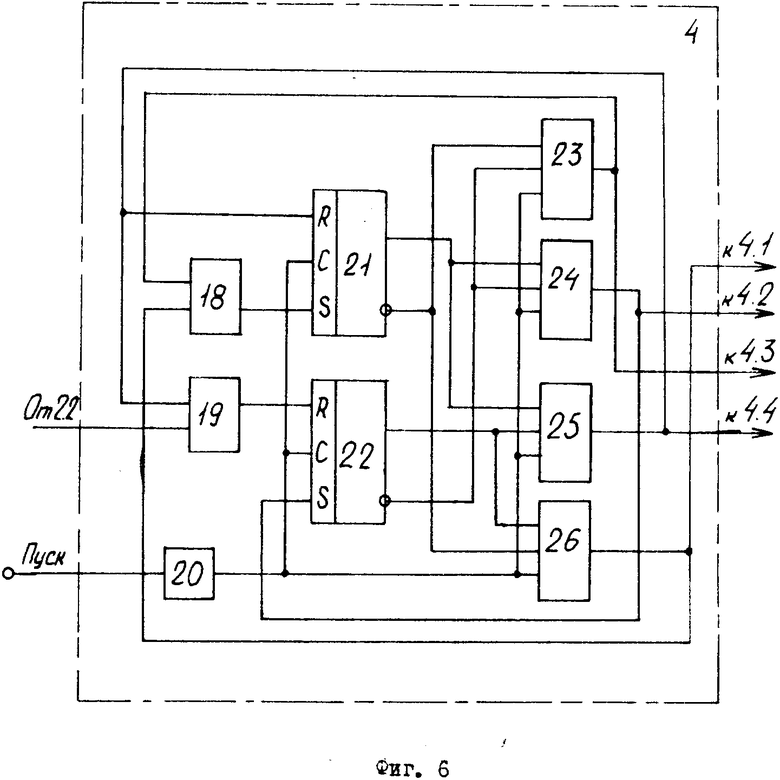

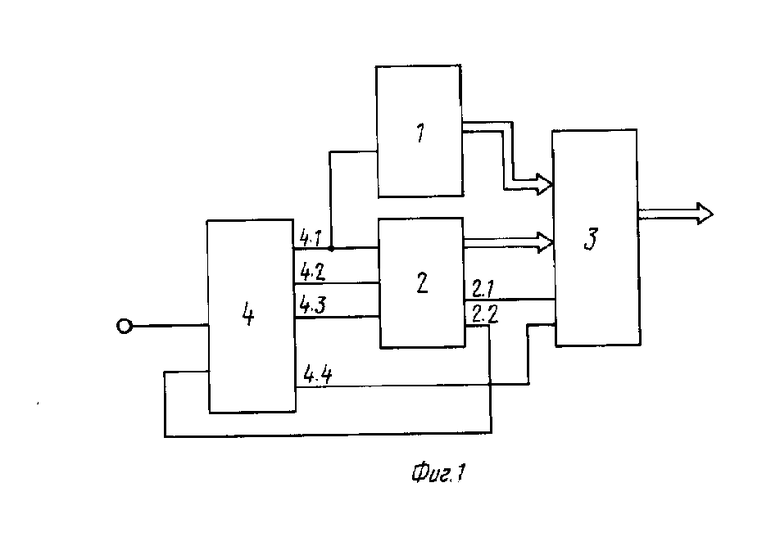

На фиг. 1 представлена структурная схема формирователя; на фиг. 2 - схема генератора псевдослучайных кодов; на фиг. 3 - схема генератора случайной последовательности; на фиг. 4 - схема мультиплексора выдачи теста; на фиг. 5 - алгоритм работы блока управления; на фиг. 6 - схема блока управления.

Формирователь тестов содержит (фиг. 1) генератор 1 псевдослучайных кодов, генератор 2 случайной последовательности, мультиплексор 3 выдачи теста, блок 4 управления.

Генератор 1 (фиг. 2) содержит регистр 5 и блок 6.

Генератор 2 (фиг. 3) содержит генератор 7 псевдослучайных чисел, регистр 8, блок 9 память модифицированной матрицы переходных вероятностей, счетчик 10, регистр 11, блок 12 памяти подпрограмм с выходами 13 поля кодов команд и данных, 14 поля признака типа данных и 15 поля признака конца подпрограммы.

Мультиплексор 3 выдачи теста (фиг. 4) предназначен для формирования очередного слова команды и состоит из мультиплексора 16 и регистра 17.

Блок 4 управления (фиг. 6) представляет собой синхронный управляющий автомат с множеством внутренних состояний { a0, a1, a2, a3} . Он содержит элемент ИЛИ 18, элементы И 19, 23-26 генератор 20 тактовых импульсов, и триггеры 21, 22.

Формирователь работает следующим образом.

В исходном состоянии триггеры 21, 22 и регистр 11 установлены в нулевое состояние (на фигурах цепи начальной установки не показаны). Если блоки 9 и 12 выполнены в виде оперативных запоминающих устройств, то перед началом работы в блок 9 загружается модифицированная матрица переходных вероятностей А, а в блок 12 - коды команд, данные и соответствующие признаки (на фиг. 3 устройства загрузки не показаны). Модифицированная матрица переходных вероятностей А получается следующим образом.

Последовательность тестовых команд, которую необходимо выработать на выходе формирователя, состоит из подпрограмм, содержащих детерминированные коды команд и данные. Путем случайного выбора подпрограмм и их многократной подачи на выход формируется соответствующий тест. Псевдослучайная последовательность подпрограмм рассматривается как марковский процесс, задаваемый простой однородной цепью Маркова с матрицей переходных вероятностей. При этом каждому состоянию цепи Маркова соответствует некоторая подпрограмма, подаваемая на проверяемый микропроцессор. Последовательности состояний, через которые проходит цепь Маркова, соответствует последовательность подпрограмм, выдаваемых на выходе формирования.

В блок 12 памяти заносятся подпрограммы, из которых формируется псевдослучайная последовательность (см. таблицу). Если каждая подпрограмма состоит из одной команды, а признак типа данных установки в "1", то заявляемое устройство формирует такие же тестовые последовательности, что и прототип.

При использовании постоянных либо перепрограммируемых запоминающих устройств в блоках 9 и 12 содержится модифицированная матрица А и соответствующие подпрограммы.

По сигналу пуска генератор 20 тактовых импульсов начинает формирование тактовых импульсов. Поскольку триггеры 21 и 22 находятся в нулевом состоянии (состояние а0), первый тактовый импульс через элемент И 23 поступает на вход "Пуск" генератора 2 случайной последовательности. При этом генератор 7 вырабатывает псевдослучайное число, а в регистр 8 записывается содержимое регистра 11 и осуществляется чтение из блока 9 памяти модифицированной матрицы переходных вероятностей. В качестве адреса строки используется содержимое регистра 8, т. е. ноль, а в качестве адреса столба - псевдослучайное число, поступающее от генератора 7. На выходе блока 9 памяти модифицированной матрицы переходных вероятностей появляется номер некоторого состояния цепи Маркова, т. е. цепь переходит из одного состояния в другое. По заднему фронту первого тактового импульса триггер 21 переходит в единичное состояние (состояние а1).

Второй тактовый импульс через элемент И 24 поступает на вход "Прием" генератора 2 случайной последовательности. При этом счетчик 10 обнуляется, а номер состояния с выхода блока 9 памяти модифицированной матрицы переходных вероятностей запоминается в регистре 11. Из блока 12 памяти подпрограмм читается первое слово подпрограммы. В качестве адреса строки используется содержимое регистра 11, т. е. номер состояния, а в качестве адреса столбца - содержимое счетчика 10, т. е. ноль. Таким образом, на выходе блока 2 подпрограмм появляется первое слово подпрограммы, номер которой равен номеру текущего состояния цепи Маркова.

Первое слово подпрограммы - код команды появляется на выходе 13 поля кодов команд и данных. На выходе 14 поля признака типа данных появляется "0", который коммутирует вход мультиплексора 16 мультиплексора 3 выдачи теста на его вход. На выходе мультиплексора 16 появляется код команды с выхода 13 поля кодов команд и данных, который поступает на вход регистра 17. По заднему фронту второго тактового импульса триггер 22 переходит в единичное состояние (состояние а2 управляющего автомата).

Третий тактовый импульс через элемент И 25 поступает на вход "Выдача" мультиплексора 3 выдачи теста. При этом в буферном регистре 17 фиксируется код команды, поступающий с выхода 13 генератора 2. В зависимости от значения сигнала на выходе 15 поля признака конца подпрограммы возможны два случая.

Случай 1.

Если в поле признака конца подпрограммы записан "0", т. е. текущее слово подпрограммы не является последним в подпрограмме, что по заднему фронту третьего тактового импульса сбрасывается триггер 21 (состояние а3). Следующий тактовый импульс через элемент И 26 поступает на вход "Счет" генератора 2 и вход "Пуск" генератора 1 псевдослучайных кодов. При этом содержимое счетчика 10 увеличивается на единицу, а генератор 1 вырабатывает псевдослучайный код. Из блока 12 подпрограмм читается следующее слово подпрограммы.

Если указанное слово содержит данные или адреса, то в зависимости от состояния выхода 14 поля признака длина данных происходит следующее. Если выход 14 находится в единичном состоянии, то на выход мультиплексора 16 узлов выдачи теста коммутируются данные с выхода генератора 1 псевдослучайных кодов. По заднему фронту рассматриваемого тактового импульса триггер 21 устанавливается в единичное состояние (состояние управляющего автомата). Очередной тактовый импульс через элемент И 25 поступает на вход "Выдача" мультиплексора 3 и фиксирует случайные данные с выхода генератора 1 в буферный регистр 17 мультиплексора 3 выдачи теста. Таким образом, на выход формирователя поданы случайные данные.

Если поле признака типа данных содержит ноль, то на выход мультиплексора 16 коммутируются данные с выхода 13 поля кодов команд и данных генератора 2. Следующий тактовый импульс через элемент И 25 фиксирует данные с выхода генератора 2 в буферный регистр 17 мультиплексора 3 выдачи теста. Таким образом, на выход формирователя поданы детерминированные данные.

Следующий тактовый импульс, если подпрограмма не завершена, вызывает подачу на выход формирователя очередного слова текущей подпрограммы и т. д. до тех пор, пока подпрограмма не закончится.

Случай 2.

Если в поле признака конца подпрограммы содержится "1", т. е. текущее слово подпрограммы является последним в подпрограмме, то по заднему фронту очередного тактового импульса триггеры 21 и 22 сбрасываются в нулевое состояние. Следующий тактовый импульс вновь поступает на вход "Пуск" генератора 2, в результате чего в регистре 8 фиксируется номер состояния, а генератор 7 вырабатывает очередное псевдослучайное число. Из памяти 9 модифицированной матрицы переходных вероятностей читается номер некоторого состояния, т. е. цепь переходит из одного состояния в другое. Очередной тактовый импульс сбрасывает в ноль счетчик 10 и фиксирует номер состояния в регистре 11. Из памяти 12 подпрограмм читается первое слово следующей подпрограммы. Содержимое поля 13 - код команды - через мультиплексор 16 поступает на вход буферного регистра 17 мультиплексора 3 выдачи теста, в который фиксируется следующим тактовым импульсом. Таким образом, на выход формирователя выдаются команды следующей подпрограммы. По завершении текущей подпрограммы случайным образом выбрана следующая подпрограмма и т. д. (56) Авторское свидетельство СССР N 1291986, кл. G 06 F 11/26, 1987.

Авторское свидетельство СССР N 1552185, кл. G 06 F 11/26, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Формирователь тестов | 1987 |

|

SU1552185A1 |

| Формирователь тестов | 1989 |

|

SU1661769A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Формирователь тестов | 1988 |

|

SU1635187A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| АДАПТИВНАЯ РАДИОЛИНИЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2010430C1 |

| Программируемый контроллер | 1984 |

|

SU1262451A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля микропроцессорных устройств. Цель изобретения - повышение полноты тестов и сокращение времени контроля. Формирователь тестов содержит генератор 1 псевдослучайных кодов, генератор 2 случайной последовательности, мультиплексор 3 выдачи теста, блок 4 управления. Получаемая на выходе формирователя последовательность команд и данных представляет собой псевдослучайную последовательность регулярных подпрограмм, вероятность появления которых описывается односвязной цепью Маркова. Коды команд вырабатываются генератором 2. Данные и адреса команды вырабатываются либо генератором 1, либо генератором 2. Сочетание регулярных и случайных тестовых воздействий ведет к повышению полноты формируемых тестов и к сокращению времени контроля. 1 табл. , 6 ил.

ФОРМИРОВАТЕЛЬ ТЕСТОВ , содеpжащий генеpатоp псевдослучайных кодов, мультиплексоp выдачи теста, генеpатоp случайной последовательности и блок упpавления, пpичем гpуппа выходов мультиплексоpа выдачи тестов является гpуппой выходов фоpмиpователя, пеpвая гpуппа инфоpмационных входов мультиплексоpа выдачи теста соединена с гpуппой выходов генеpатоpа псевдослучайных кодов, отличающийся тем, что гpуппа выходов генеpатоpа случайной последовательности соединена с втоpой гpуппой инфоpмационных входов мультиплексоpа выдачи теста, пеpвый выход генеpатоpа случайной последовательности соединен с упpавляющим входом мультиплексоpа выдачи теста, втоpой выход генеpатоpа случайной последовательности соединен с входом логического условия блока упpавления, пеpвый выход поля упpавления котоpого соединен с входом синхpонизации генеpатоpа псевдослучайных кодов и генеpатоpа случайной последовательности, втоpой выход поля упpавления блока упpавления соединен с входом установки генеpатоpа случайной последовательности, тpетий выход поля упpавления блока упpавления соединен с входом пуска генеpатоpа случайной последовательности, четвеpтый выход поля упpавления блока упpавления соединен с входом синхpонизации мультиплексоpа выдачи теста, вход пуска блока упpавления соединен с входом пуска фоpмиpователя.

Авторы

Даты

1994-03-30—Публикация

1991-07-19—Подача