.12

первыми входами четвертого и пятого элементов , вторые входы которых соединены с входом третьего разряда блока десятичной коррекции, с первым входом шестого элемента И-НЕ и вторым входом третьего элемента И-НЕ, а через второй элемент НЕ соединен с вторым входом первого элемента И-НЕ и первым входом седь- мого элемента И-НЕ, второй вход которого соединен с входом второго разряда блока десятичной коррекции, с вторыми входами второго и шестого . элементов И-НЕ и с третьим входом четвертого элемента И-НЕ,а через тре- тий элемент НЕ соединен с третьим I

1

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении устройст преобразования информации.

Известен преобразователь двоичного кода в двоично-десятичный, содежащий ярусы сумматоров по модулю 10, выходы сумматоров каждого яруса соединены с входами сумматоров соседнего старшего яру са, а входы сумматоров по модулю 10 младшего яруса соединены с шинами входного кода l1| .

Недостаток этого преобразователя состоит в большом объеме оборудования и низком быстродействии.

Наиболее близким техническим решением к предлагаемому является преобразователь двоичного кода в двоично-десятичный, содержгцдий сумматоры декад, первые входы многоразрядных сумматоров соединены с входами разрядов двоичного кода, блоки десятичной коррекции, входы которых соединены с выходами сумматоров декад, имеющих веса двоично-десятичных эквивалентов, вторые входы сумматоров декад соединены с выходами переносов многоразрадного сумматора и с выходом переноса блока десятичной коррекции соседней младшей декады zj

Недостатками указанного преобразователя являются относительно боль7

входом пятого элемента И-НЕ, выход которого через четвертый элемент НЕ соединен с выходом третьего разряда блока десятичной коррекции, вы- .ходы первого и второго разрядов которого, а также выход переноса блока десятичной коррекции соединены соответственно с выходами восьмого, девятого и десятого элементов И-НЕ, первые входы которых соединены соответственно с выходами четвертого, второго и третьего элементов И-НЕ, вторые входы восьмого, девятого и десятого элементов И-НЕ соединены соответственно с выходами первого седьмого и шестого элементов И-НЕ.

шой объем необходимой аппаратуры и относительно низкое быстродействие.

Цель изобретения - упрош;ение преобразователя.

Поставленная цель достигается тем, что преобразователь двоичного кода в двоично-десятичный, содер жащий К сумматоров декад, где К число десятичных разрядов и К блоков десятичной коррекции, входы ко- торых соединены с разрядными выходами соответствуюш 1х сумматоров декад, выходы переноса i -ro(i 1 - К-1)

сумматора декады соединены с группой входов переноса (i+l)-ro сумматора декад, первая группа информационных входов которого соединена с первой группой разрядных входов

преобразователя, первая группа выходов которого соединена с выходами блоков десятичной коррекции, вторая группа выходов преобразователя соединена с выходами младших разрядов

всех сумматоров декад, кроме первого, выход мпадшего разряда преобразователя соединен с входом младше- го разряда преобразоват,еля, выход переноса i -го блока десятичной коррекции соединен с входом переноса (i +l)-го сумматора декады, выход переноса К-го блока десятичной коррекции и группа выходов переноса

.К-го сумматора декады являются третьей группой выходов преобразо- вателя, вторые группы входов всех сумматоров декад, кроме трех первых, соединены в соответствии с весами с разрядными входами преобразователя, содержит многовходовой сумматор, выходы которого в соответствии с их весами соединены с вторыми группами входов первого, второго и третьего сумматоров декады, первая группа входов многовходового сумматора, имеющая вес 16, соединена соответственно с входами (4(6+1) +l) -х разрядов преобразователя, где п

г О 4

-, а п - число двоичных

разрядов преобразователя, вторая группа входов многовходового сумматора, имеющая вес 24, соединена сооветственно с входами (7+4С)-X разрядов преобразователя, третья группа входов многовходового сумматора, :Имею1цая вес 48, соединена с входами (8+4Е) -X разрядов преобразователя, четвертая и пятая группы входов многовходового сумматора, имеющие веса 12 и 112, соответственно сое-

дине ны с входами (6+46) -х разрядов

преобразователя. I .

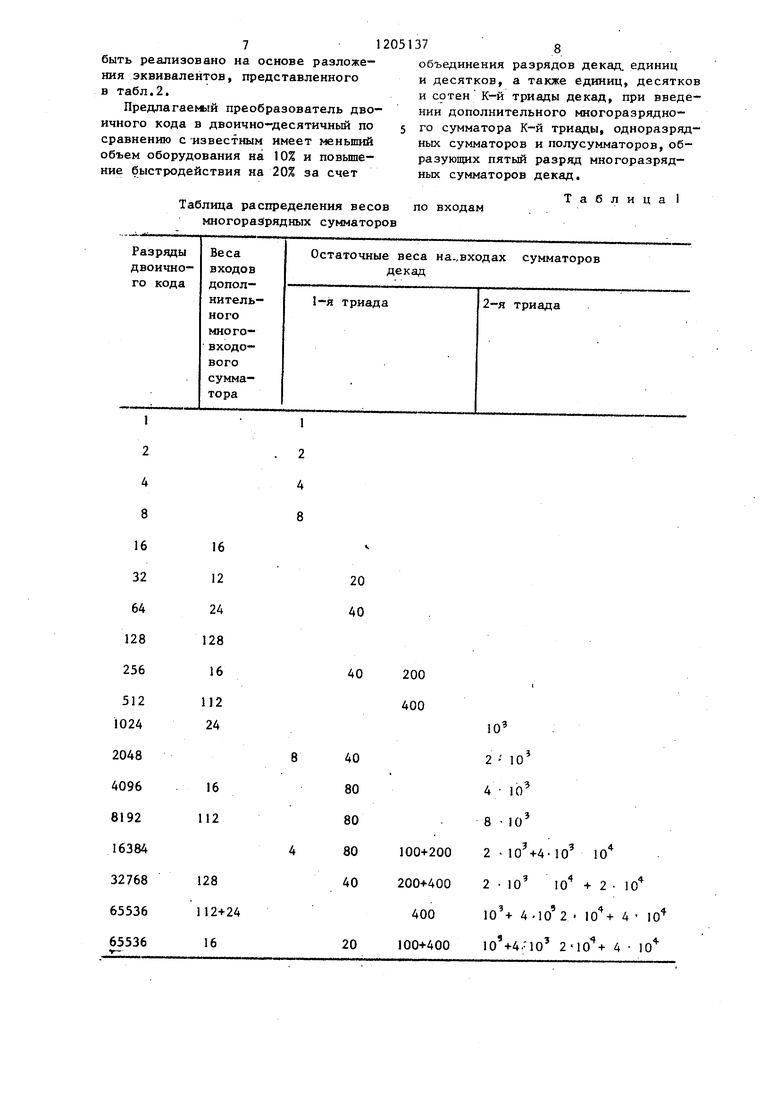

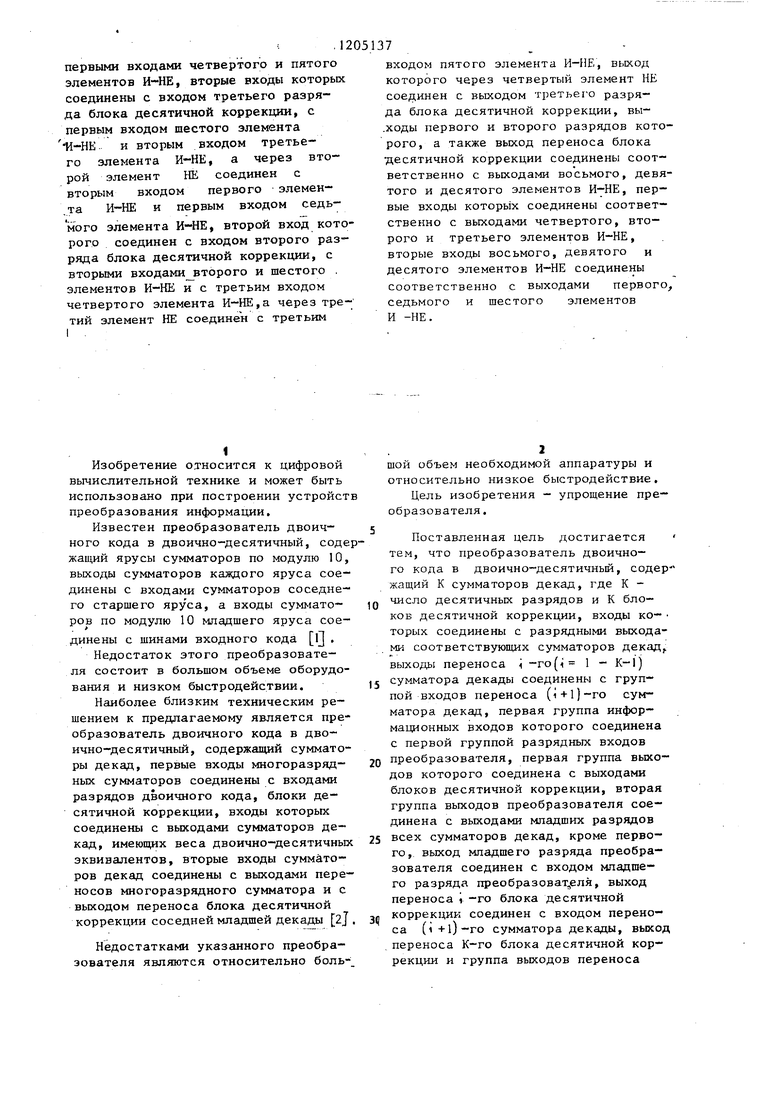

Кроме того, в преобразователе блок десятичной коррекции содержит четыре элемента НЕ и десять элементов И-НЕ, причем вход первого разряда блока десятичной коррекции соединен с первыми входами первого, второго и третьего элементов И-Н и через первый элемент НЕ соединен с первыми входами четвертого и пятого элементов И-НЕ, вторые входы ;которых соединены с входом третьего ..разряда блока десятичной коррекции, с первым входом шестого элемента И-НЕ и вторым входом третьего элемента И-НЕ, а через второй элемент НЕ соединен с вторым входом первого элемента И-НЕ и первым входом седьмого элемента И-НЕ, второй вход которого соединен с входом второго разряда блока десятичной коррекции, с вторыми входами второго и шестого элементов И-НЕ и с третьим входом четвертого элемента И-НЕ, а через третий-элемент НЕ соединен с третьим входом пятого элемента И-НЕ выход которого через четвертый элемент НЕ соединен с выходом третьего разряда блока десятичной коррекции.

2051.374

выходы первого и второго разрядов которого, а также выход переноса блока десятичной коррекции соединены соответственно с выходами восьмого, 5 девятого и десятого элементов И-НЕ, первые входы которых соединены соответственно с выходами четвертого, второго и третьего элементов И-НЕ, вторые входы восьмого, девято- 0 го и десятого элементов И-НЕ соединены соответственно с выходами первого, седьмого и шестого элементов И-НЕ.

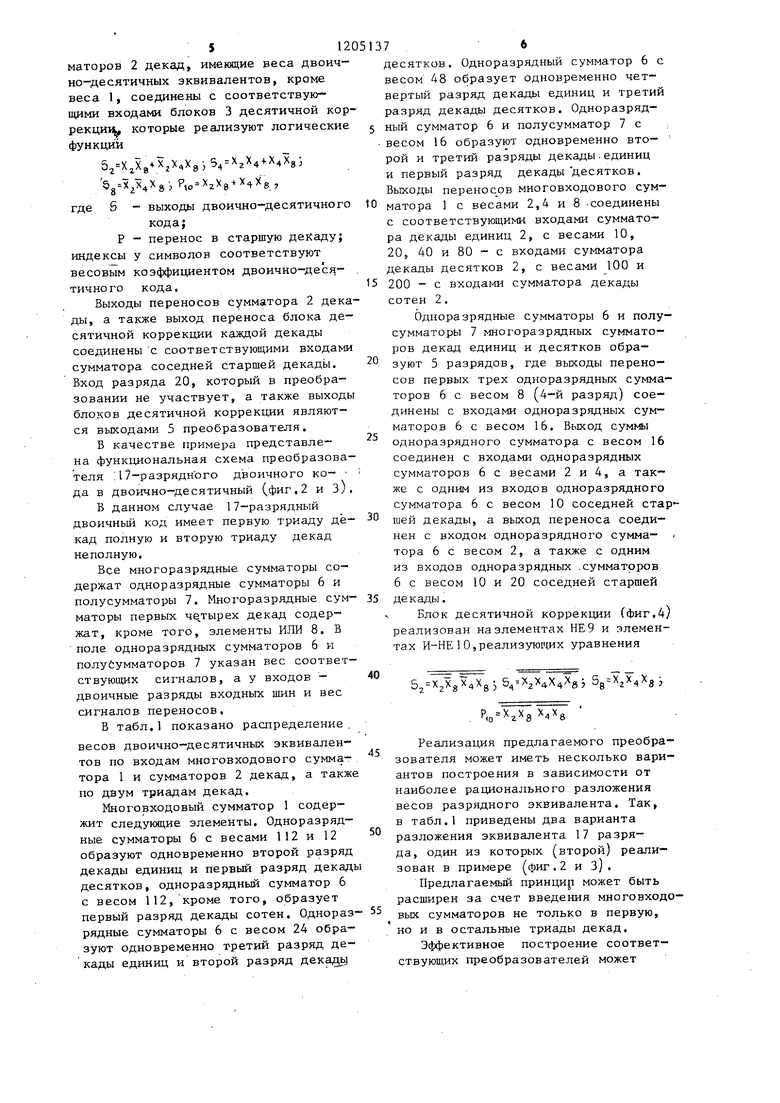

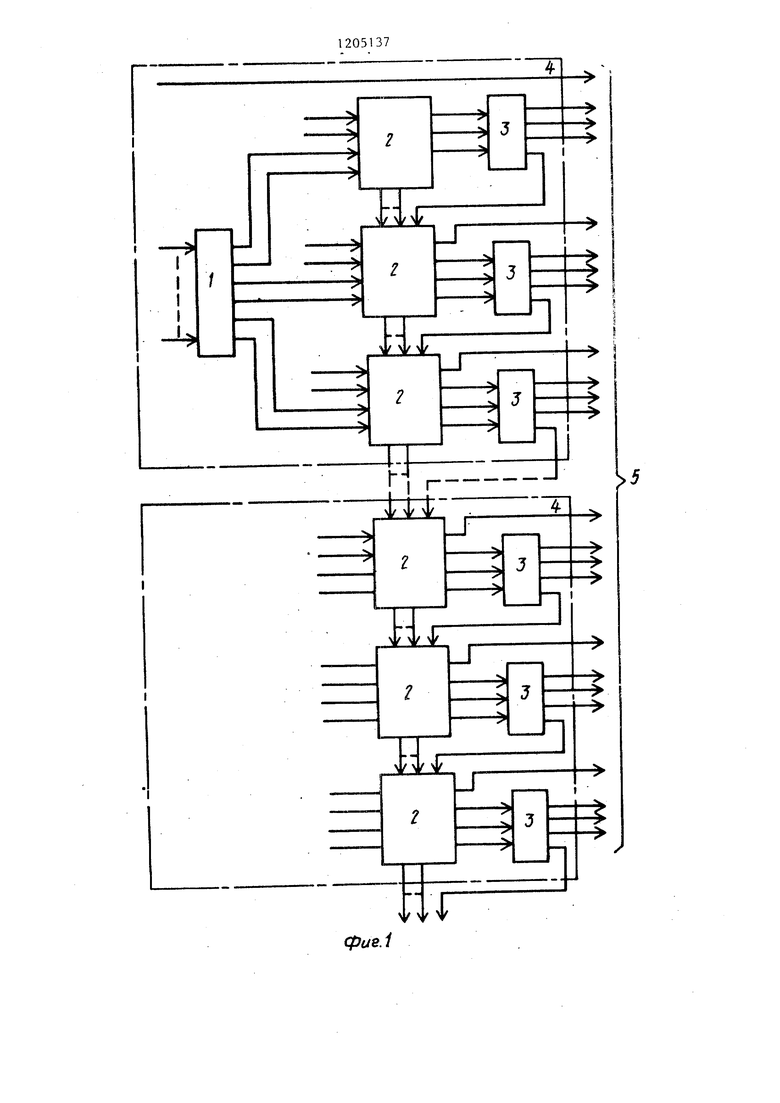

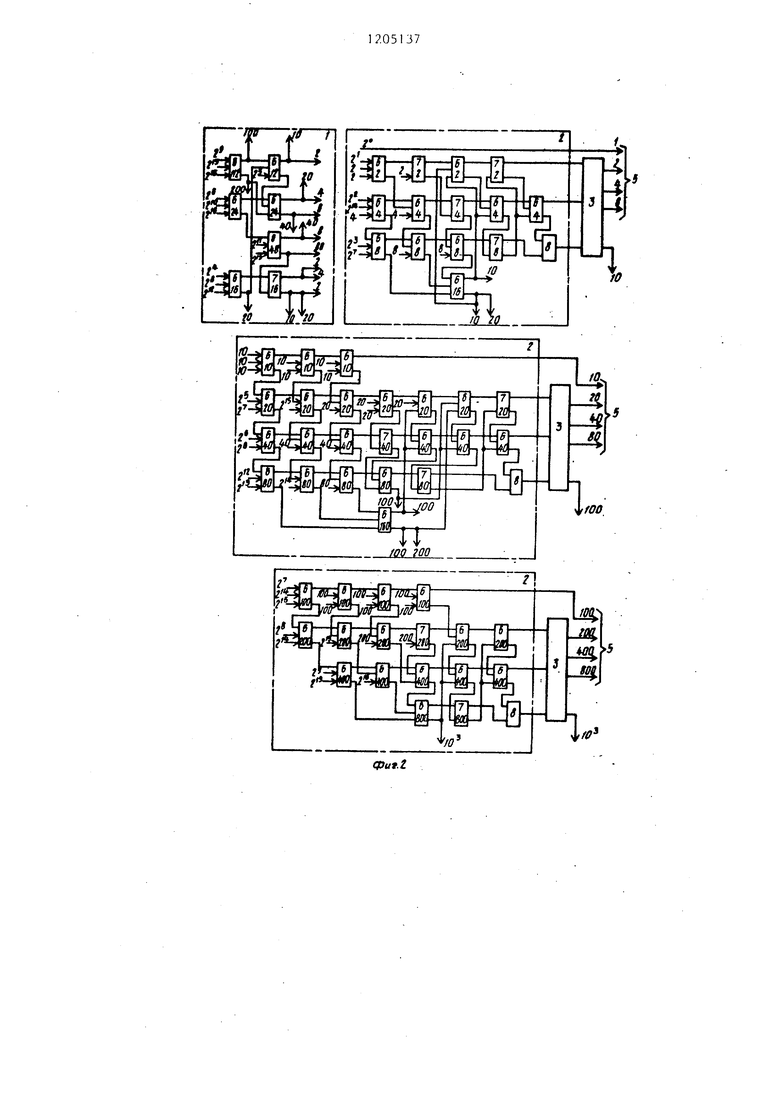

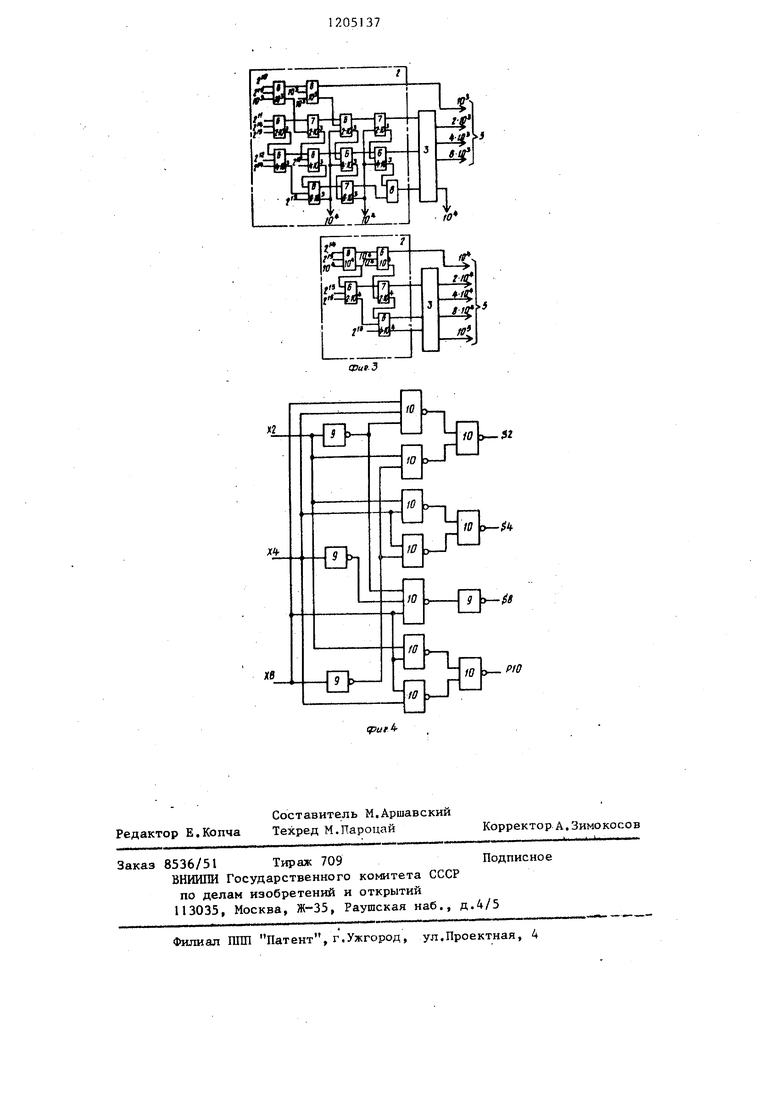

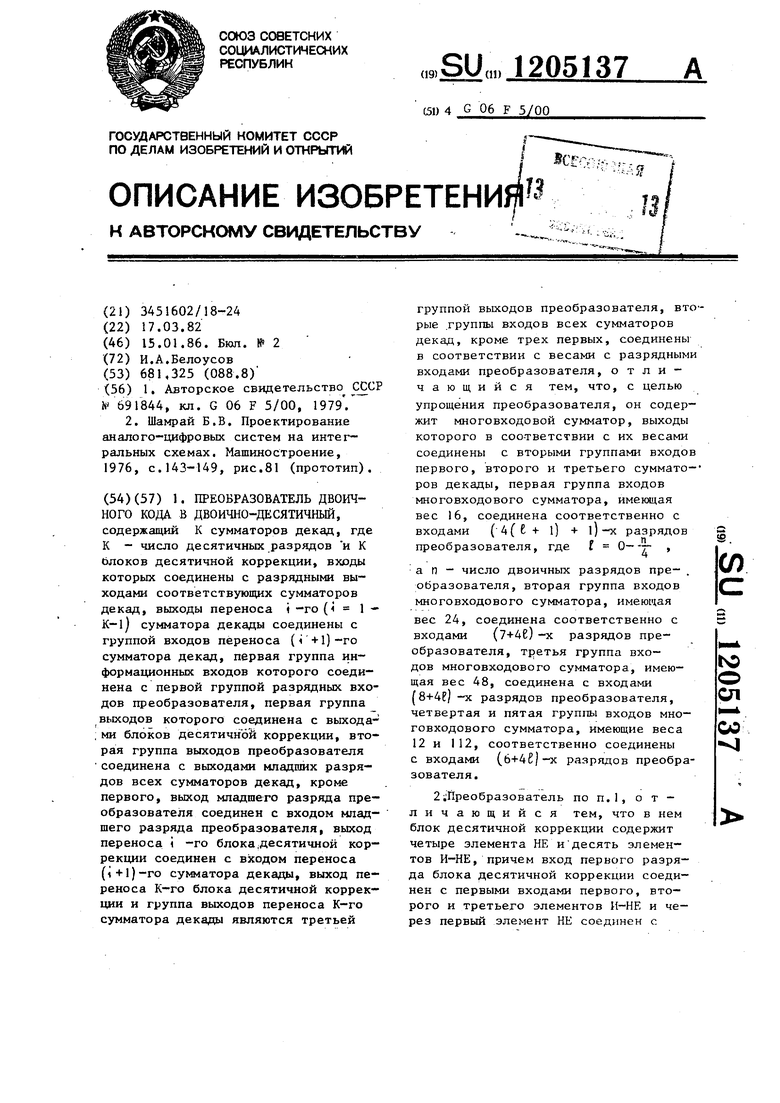

На фиг. 1 изображена структурная схема преобразователя; на фиг.2 и 3 - функциональная схема преобразователя 17-разрядного двоичного кода в двоично-десятичный; на фиг. 4 - функциональная схема блока десятичной коррекции.

Предлагаемый преобразователь построен на основании разбиения десятичных эквивалентов П -разрядного двоичного кода на триады декад

20

Декады состоят из 2 - 2

(табл.1).

разрядов, где 1 10(к-1J для декад единиц; i 4+10(К-1) для декад десятков, 1 7+10(К-1) для декад 30 сотен К-и триады декад.

Преобразователь содержит много- входовой сумматор 1, сумматоры 2 декад, блоки 3 десятичной коррекции, триады 4 декад, выходы 5, 35 Входы многовходового сумматора 1 первой триады декад соединены с входами разрядов двоичного кода из группы разрядов 2 - 2 , которые

имеют общие веса двоично-десятичных

эквивалентов одновременно в декадах

единиц и десятков при i 4+10(к-1/ а также единиц, десятков и сотен при i 7+10(К-l). Выходы многовхо- дового сумматора 1, имеющие веса

двоично-десятичньк эквивалентов декад единиц, десятков и сотен первой триады 4 декад, соединены с первыми входами сумматоров декад единиц, десятков и сотен 2, Входы разрядов

двоичного кода, не имеющие общих, двоично-десятичных эквивалентов, а также имеющие остаточные веса двоично-десятичных эквивалентов, за вычетом тех весов, которые поступают

на входы многовходового сумматора, соединены с вторыми входами сумматоров 2 декад единиц, десятков и сотен Ж-и триады 4 декад. В)1ходы сум-

маторов 2 декад, именщие веса двоично-десятичных эквивалентов, кроме веса 1, соединены с соответствующими входами блоков 3 десятичной кор рекции. которые реализуют логические функции

5.j X,,,X8i54 + 4X8i , P,o 2X8 + .

где S - выходы двоично-десятичного

кода;

Р - перенос в старшую декаду; индексы у символов соответствуют весовым коэффициентом двоично-деся- тичного кода,

Выходы переносов сумматора 2 декады, а также выход переноса блока десятичной коррекции каждой декады соединены с соответствующими входами сумматора соседней старшей декады. Вход разряда 20, который в преобразовании не участвует, а также выходы блоков десятичной коррекции являются выходами 5 преобразователя,

В качестве примера представле- на функциональная схема преобразователя 17-разрядного двоичного ко- да в двоично-десятичный (фиг,2 и З),

В данном случае 17-разрядный двоичный код имеет первую триа,цу декад полную и вторую триаду декад неполную.

Все многоразрядные сумматоры содержат одноразрядные сумматоры 6 и полусумматоры 7, Многоразрядные сум- маторы первых че тырех декад содержат, кроме того, элементы ИЛИ 8, В поле одноразрядных сумматоров 6 и полусумматоров 7 указан вес соответствующих сигналов, а у входов - двоичные разряды входных шин и вес сигналов переносов,

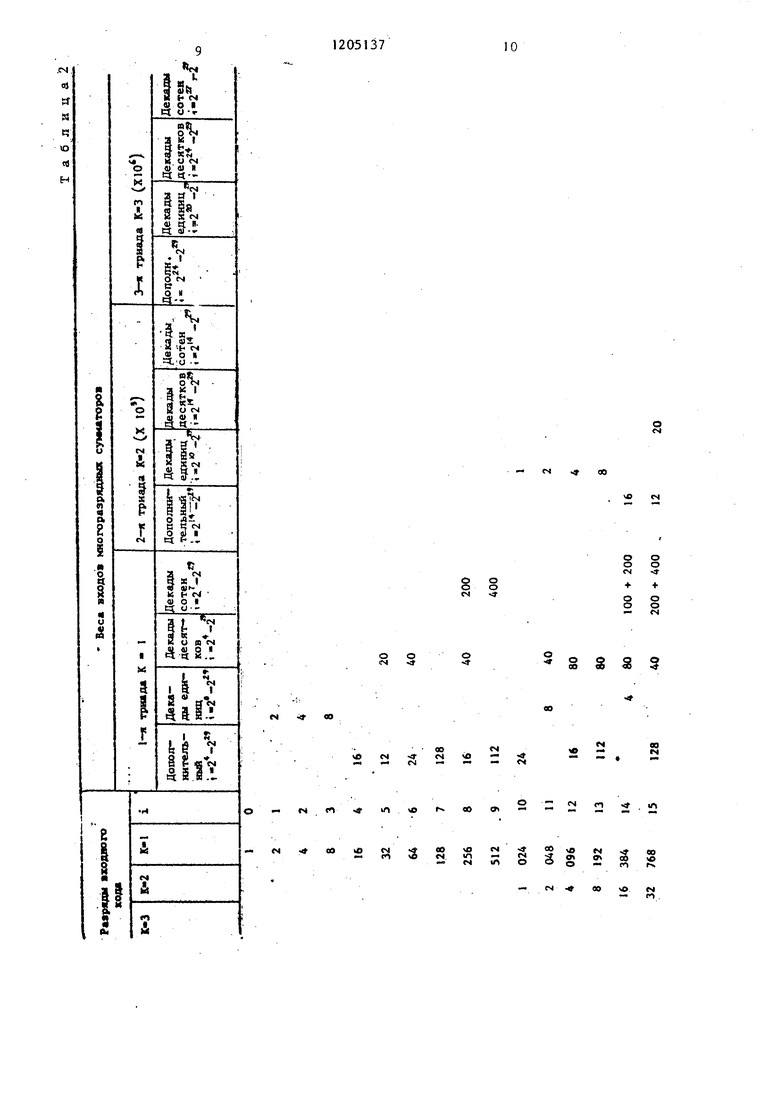

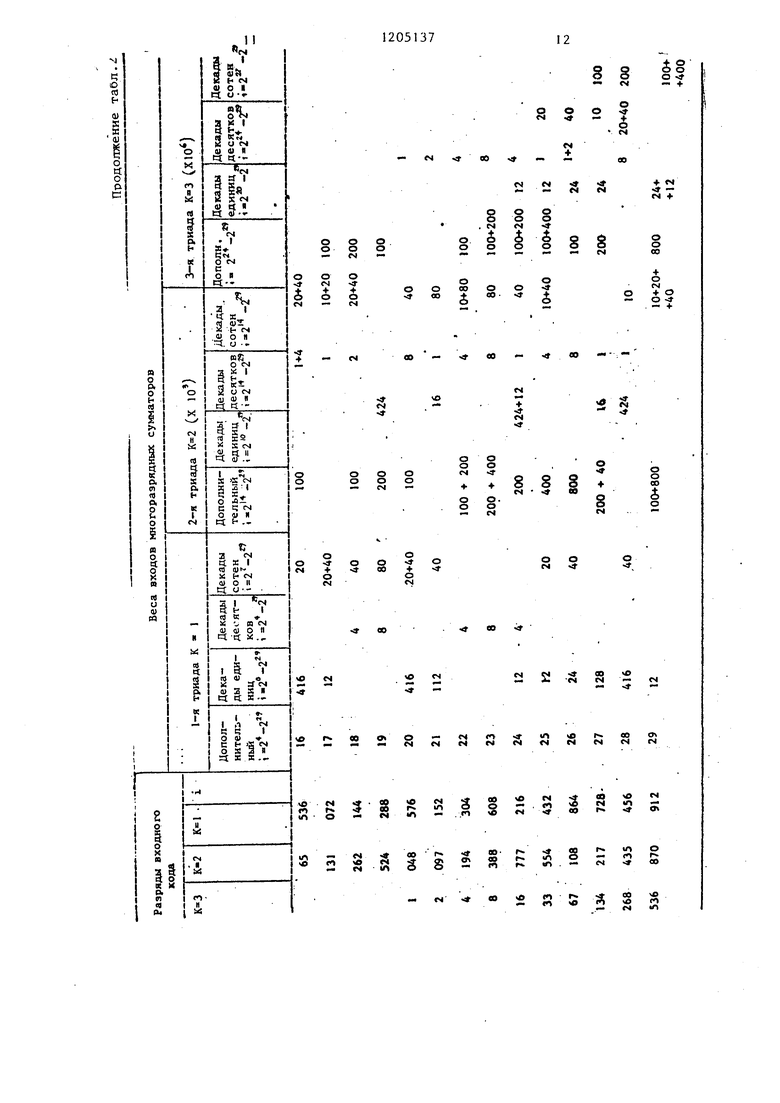

В табл,1 показано распределение.

весов двоично-десятичных эквивален-

тов по входам многовходового сумматора 1 и сумматоров 2 декад, а также по двум триадам декад,

Многовходовый сумматор 1 содержит следующие элементы. Одноразрядные сумматоры 6 с весами 112 и 12 образуют одновременно второй разряд декады единиц и первый разряд декады десятков, одноразрядный сумматор 6 с весом 112, кроме того, образует первый разряд декады сотен, Однораз- рядные сумматоры 6 с весом 24 образуют одновременно третий разряд декады единиц и второй разряд декад,ь1

.-

-

о 10

. 5

а20 ы

7ч

,

3540

30

десятков. Одноразрядный сумматор 6 с весом 48 образует одновременно четвертый разряд декады единиц и третий разряд декады десятков. Одноразрядный сумматор 6 и полусумматор 7 с ; весом 16 образуют одновременно второй и третий разряды декады.единиц и первый разряд декады десятков. Выходы переносов многовходового сумматора 1 с весами 2,4 и 8 -соединены с соответствующими входами сумматора декады единиц 2, с весами 10, 20j 40 и 80 - с входами сумматора декады десятков 2, с весами 100 и 200 - с входами сумматора декады сотен 2,

Одноразрядные сумматоры 6 и полусумматоры 7 многоразрядных сумматоров декад единиц и десятков образуют 5 разрядов, где выходы переносов первых трех одноразрядных сумматоров 6 с весом 8 (4-й разряд) соединены с входами одноразрядных сумматоров 6 с весом 16, Выход суммы одноразрядного сумматора с весом 16 соединен с входами одноразрядных сумматоров 6 с весами 2 и 4, а также с одним из входов одноразрядного сумматора 6 с весом 10 соседней старшей декады, а выход переноса соединен с входом одноразрядного сумматора 6 с весом 2, а также с одним из входов одноразрядных .сумматоров 6 с весом 10 и 20 соседней старшей декады.

Блок десятичной коррекции (фиг,4) реализован на элементах НЕ9 и элементах И-НЕ1 О,реализующих уравнения

S. .

o

X,Xg

Реализация предлагаемого преобразователя может иметь несколько вариантов построения в зависимости от наиболее рационального разложения весов разрядного экв;ивалента, Так, в табл.1 приведены два варианта разложения эквивалента 17 разряда, один из которых (второй) реализован в примере (фиг,2 и З),

Предлагаемый принцир может быть расширен за счет введения многовходо вых сумматоров не только в первую, но и в остальные триады декад,

Эффективное построение соответствующих преобразователей может

71

быть реализовано на основе разложения эквивалентов, представленного в табл.2.

Предлагаемз й преобразователь двоичного кода в двоично-десятичный по сравнению с известным имеет меньший объем оборудования на 10% и повышение быстродействия на 20% за счет

Таблица распределения весов по входам многоразрядных сумматоров

16

12

24

128

16

112 24

16

112

128

112+24 16

2 4 8

2051378

объединения разрядов декад, единиц и десятков, а также единиц, десятков и сотен К-й триады декад, при введении дополнительного многоразрядно- 5 го сумматора К-й триады, одноразрядных сумматоров и полусумматоров, образующих пятый разряд многоразрядных сумматоров декад.

Таблица 1

20 40

40

200 400

10

100+200 200+400

400 100+400

2 - 10

4 10

8 10

2 -1о +4-10 10

2 10

10 + 2 10

10Ч 4.102 10 + 4 10 10 +4, 10 2ЧО + 4 10

00

- c Jf 00

о о

IN

о -«

g S S 5

oo«Ч

2 я 2 S

(Ч lO -

s

Ю «

о - (M

w - - -

. in

ГЧ

СЛ

:s

00 vo « :

СЧ 0 -; 2J «« «Ч 1Л о

CO

3

«Ч

ON

s

(Л

«o

«o

eo

0 CM

- PI.

фае. i

ifff

Г -Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный код | 1982 |

|

SU1097995A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1221758A1 |

| Преобразователь двоичного кода в двоично-десятично- шестидесятиричный код | 1982 |

|

SU1051529A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Преобразователь двоичного кода угла в двоично-десятичный код градусов и минут | 1983 |

|

SU1116425A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Преобразователь двоичного кода в двоично-десятичный | 1985 |

|

SU1304175A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1043627A1 |

Составитель М.Аршавский Редактор Е.Копча Техред М.Пароцай Корректор А.Зимокосов

Заказ 8536/51 Тиране 709Подписное

ВНИИПИ Государствеиного комитета СССР по делам изобретений и открытий 113035, Москва, Ж--35, Раушская наб., д.4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

ТЪп

«

ГЦ

UP

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691844A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шамрай Б.В | |||

| Проектирование аналого-цифровых систем на интегральных схемах | |||

| Машиностроение, 1976, с.143-149, рис.81 (прототип). | |||

Авторы

Даты

1986-01-15—Публикация

1982-03-17—Подача