СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь кодов | 1986 |

|

SU1578813A1 |

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ РАДИОЛОКАЦИОННОГО ИЗОБРАЖЕНИЯ МЕСТНОСТИ | 1988 |

|

SU1841035A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах передачи информации для преобразования равновесной формы кода с иррационными отрицательными основаниями в двоич- ньш код. Цель изобретения - упрощение устройства. Устройство содержит блок 2 формирования импульсов,, накапливающий сумматор 4, счетчик 5 адреса, преобразователь 1 последовательного кода в параллельный, блок 3 хранения двоичных эквивалентов. Предлагаемое устройство позволяет снизить аппаратурные затраты за счет применения одноступенчатой схемы накапливающего сумматора и уменьшения емкости ПЗУ. 2 3.п. ф-лы, 1 табл., 3 ил.

г/./

Изобретение относится к вычислительной технике и может быть ис- .пользовано в системах передачи информации для преобразования равновесной формы кода с иррациональными от- рицательными основаниями в двоичный код.

Целью изобретения является упрощение преобразователя,

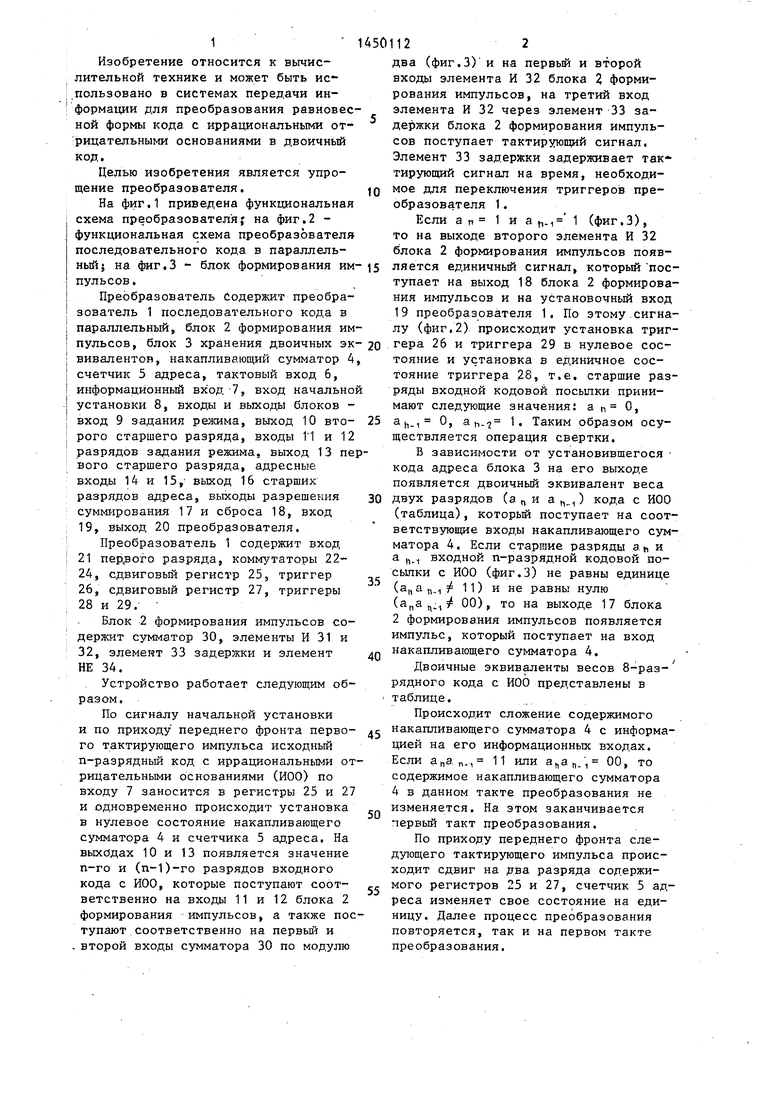

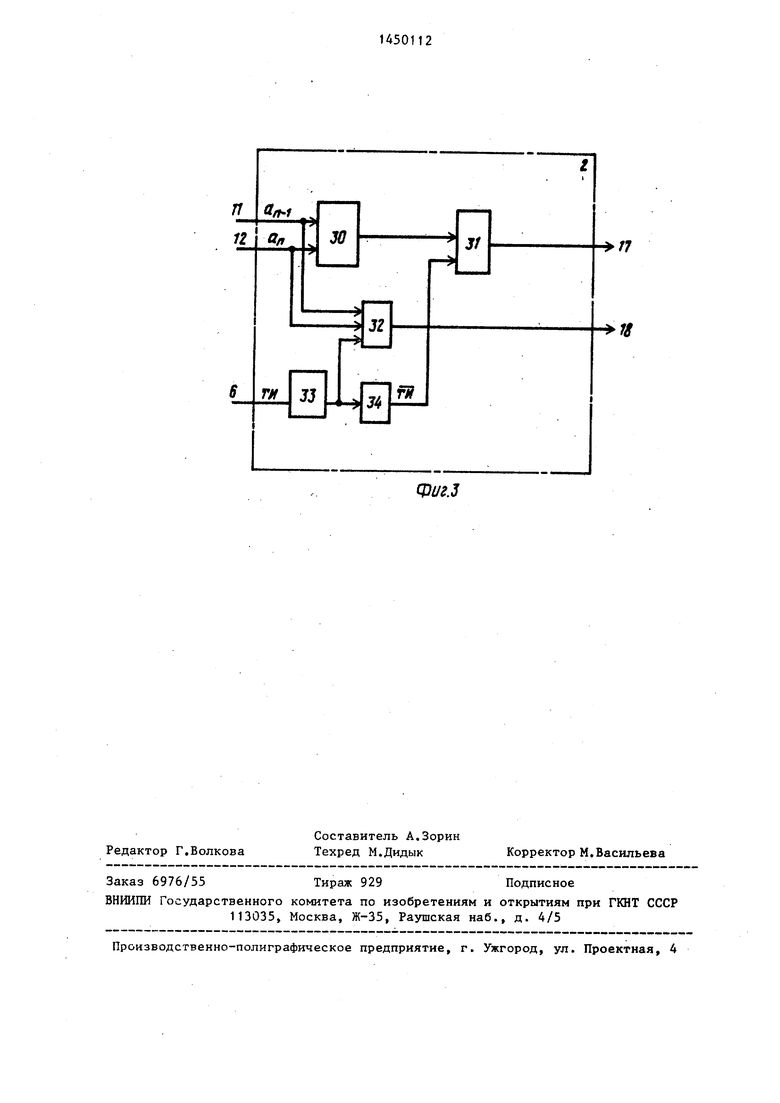

На фиг.1 приведена функциональная схема преобразователя; на фиг.2 функциональная схема преобразователя последовательного кода в параллельный; на фиг.З - блок формирования им пульсов.

Преобразователь Содержит преобразователь 1 последовательного кода в параллельный, блок 2 формирования импульсов, блок 3 хранения двоичных эк Бивалентов, накапливающий сумматор 4 счетчик 5 адреса, тактовый вход б, информационный вход-7, вход начально установки 8, входы и выходы блоков - вход 9 задания релсима, выход 10 вто- рого старшего разряда, входы 11 и 12 разрядов задания режима, выход 13 певого старшего разряда, адресные входы 14 и 15, выход 16 старших разрядов адреса, выходы разрешения суммирования 17 и сброса 18, вход 19, выход 20 преобразователя.

Преобразователь 1 содержит вход 21 первого разряда, коммутаторы 22- 24, сдвиговый регистр 25, триггер 26, сдвиговый регистр 27, триггеры 28 и 29.

Блок 2 формирования импульсов содержит сумматор 30, элементы И 31 и 32, элемент 33 задержки и элемент НЕ 34.

Устройство работает следующим образом.

По сигналу начальной установки и по приходу переднего фронта перво- го тактирующего импульса исходный п-разрядный код с иррациональными отрицательными основаниями (ИОО) по входу 7 заносится в регистры 25 и 27 и одновременно происходит установка в нулевое состояние накапливающего сумматора 4 и счетчика 5 ад,реса. На выходах 10 и 13 появляется значение п-го и (п-1)-го разрядов входного кода с ИОО, которые поступают соот- ветственно на входы 11 и 12 блока 2 формирования импульсов, а также поступают .соответственно на первый и . второй входы сумматора 30 по модулю

Q

5

0 5 О

0

j

5

0

два (фиг.З) и на первьй и второй входы элемента И 32 блока 2 формирования импульсов, на третий вход элемента И 32 через элемент 33 задержки блока 2 формирования импульсов поступает тактирующий сигнал. Элемент 33 задержки задерживает так тирующий сигнал на время, необходимое для переключения триггеров преобразователя 1.

Если ап 1 и af,. (фиг.З), то на выходе второго элемента И 32 блока 2 формирования импульсов появляется единичный сигнал, который поступает на выход 18 блока 2 формирования импульсов и на установочный вход 19 преобразователя 1. По этому.сигналу (фиг.2) происходит установка триггера 26 и триггера 29 в нулевое состояние и установка в единичное состояние триггера 28, т.е. старшие разряды входной кодовой посылки принимают следующие значения: а п О, а,., О, ац-7 1« Таким образом осуществляется операция свертки.

В зависимости от установившегося - кода адреса блока 3 на его выходе появляется двоичньш эквивалент веса двух разрядов (а и а...,) кода с ИОО (таблица), который поступает на соответствующие входы накапливающего сумматора 4. Если старшие разряды а, и а ., входной п-разрядной кодовой по- сьшки с ИОО (фиг.З) не равны единице (а,, а „. 7 11) и не равны нулю ( . 5 00) то на выходе 17 блока 2 формирования импульсов появляется импульс, который поступает на вход накапливающего сумматора 4.

Двоичные эквиваленты весов 8-разрядного кода с ИОО представлены в таблице.

Происходит сложение содержимого накапливающего сумматора 4 с информацией на его информационных входах. Если ., 11 или ., 00, то содержимое накапливающего сумматора 4 в данном такте преобразования не изменяется. На этом заканчивается первый такт преобразования.

По приходу переднего фронта следующего тактирующего импульса происходит сдвиг на два разряда содержимого регистров 25 и 27, счетчик 5 адреса изменяет свое состояние на единицу. Далее процесс преобразования повторяется, так и на первом такте преобразования.

314501

Для преобразования п-разрядной входной кодовой посьшки необходимо п/2 тактов преобразования, так как преобразование входной п-разрядной g кодовой посьшки с ИОО осуществляется по два разряда на каждом такте преобразования.

При записи входной п-разрядной кодовой посьшки с ИОО преобразова- 10 тель 1 (фиг.2) независимо от значения первого разряда, который является кладшим разрядом а входной п- разрядной кодовой посылки с ИОО, на первый информационный вход сдвиго- 15 вого регистра 25 поступает уровень логического О, поскольку вес младшего разряда п-разрядной кодовой посьшки с ИОО равен О. Это приводит к тому, что на последнем такте пре- 20 образования не возникает комбинация , которая требует выполнения операции свертки.

По окончании преобразования результат преобразования находится в накапливающем сумматоре 4.

Формула изобретения

нен с входом начальной установки пробразователя, тактовый вход которого соединен со счетным входом счетчика адреса, тактовым входом блока формирования импульсов и входом синхронизации преобразователя последовательного кода в параллельный, выход старшего разряда которого соединен с входом младдаего разряда адреса блока хранения двоичных эквивалентов.

5 14501

формирования импульсов содержит сумматор по модулю два, два элемента И, элемент НЕ и элемент задержки, причем входы первого и второго разрядов задания режима блока формирования им- пульсов соединены с соответствующими входами сумматора по модулю два к первого элемента И, третий вход которого соединен с выходом элемента ю задержки и входом элемента НЕ, выхол

126

которого соединен с первым входом второго элемента И, второй.вход и выход которого соединены соответственно с выходом сумматора по модулю два и выходом разрешения суммирования блока формирования импульсов, выход сброса и тактовый вход которого . соединены соответственно с выходом первого элемента И и входом элемента задержки.

Фиг.З

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-01-07—Публикация

1987-05-24—Подача