315

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для вычисления логариф- мов чисел.

Цель изобретения - упрощение устройства и повышение быстродействия.

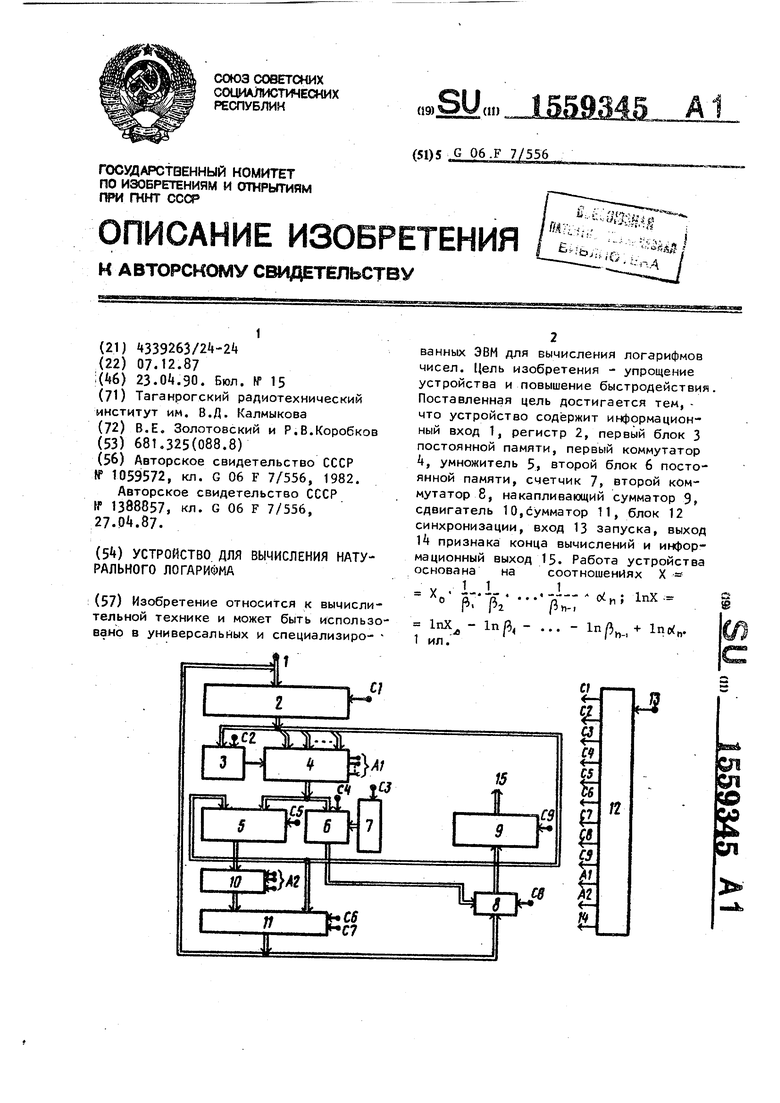

На чертеже представлена структурная схема устройства для вычисления натурального логарифма.

Устройство содержит информационный вход 1, регистр 2, первый блок 3 постоянной памяти, первый коммутатор 4, умножитель 5, второй блок 6 постоянной памяти, счетчик 7, второй коммутатор 8, накапливающий сумматор 9, сдвигатель 10, сумматор 11, блок 12 синхронизации, вход 13 запуска, выход Н приз нака конца вычислений, информационный выход 15.

Устройство работает следующим об- ,разом.

Аргумент X поступает на информационный вход 1 устройства. На вход 13 запуска поступает сигнал запуска.Блок 12 синхронизации вырабатывает сигнал на первом выходе, который посту- .пает на вход записи регистра 2. Одновременно на выходе 1 признака конца вычислений вырабатывается сигнал, отключающий информационный вход 1 устройства .

Во втором такте формируются сигналы С1 - С7, С9 и А1. По сигналам А1 первый коммутатор 4 настраивается на соединение первого входа на выход. Пб сигналу С5 в умножителе вычисляется

мяти Величина --- хо

значение , Х/Х0, где Х0 - значение первой группы разрядов числа X. Разрядность числа Х0 определяется разрядностью первого блока 3 постоянной папоступает на

вход второго блока 6 постоянной памя- ти, где формируется полноразрядная величина 1пХв, которая по сигналу ГЛ считывается. Сигналы Сб и С7 настраивают сумматор 11 таким образом, что он только пропускает значение произведения с выхода умножителя 5, которое поступает на вход регистра 2 и записывается в него по заднему фронту сигнала С1 .

По заднему фронту сигнала СЗ в счетчике 7 устанавливается код 01. Счетчик 7 logj C.ti+1)-разрядный и его выходы подключаются к старшим адресным входам. Они определяют страницу

памяти, с которой в-данном такте работает устройство. Распределение следующее: 00--Х0, 01- (-In/3,), 10- (-1пр), 11-(-ln|}3) и т.д.-На этом второй такт работы завершается.

В третьем такте вновь формируются сигналы С1 - С7, С9 и А1. Код А1 на входе первого коммутатора Ц формируется так, что образуется соединение второго входа на выход коммутатора. -При этом на второй вход коммутатора 4 подключаются n-разрядов регистра 2, начиная с младшего разряда предыдущей группы.

Текущая группа из п разрядов поступает на вход умножителя 5 и второго блока 6 постоянной памяти. Во второй области памяти записана таблица значений

In p( -1п(2т-5,), где оГ, 2.00.. .0 ххх. ..х

п - 1 разрядов; п разрядов. Умножитель 5 Формирует значение

с/,(2-5:1)(1- Ј ()

5 ,

35

40

50

5

где рЈ, ,0.00.. ... .x,

n - 1 разрядов; п разрядов. На вход умножителя 5 и блока 6 постоянной памяти поступают только значащие разряды величины oi, , В блоке 6 постоянной памяти соответствующий сдвиг и единица в целой части учитываются при прошивке. При умножении соответствующий сдвиг необходимо осущест-, вить физически. Эту операцию выполняет сдвигатель 10, на управляющие входы которого поступает код А2, настраивающий его на сдвиг числа на п-1 разрядов в сторону младших разрядов с одно временным инвертированием. На второй вход сумматора 11 поступает величина о(,, поэтому на его выходе формируется требуемая величина оЈг о,-, сх ,. Полученное значение по заднему фронту заносится в регистр 2. Считанное из блока 6 постоянной памяти по сигналу С значение In ft, поступает через второй коммутатор 8 на вход накапливающего сумматора 9 где складывается с предыдущим значением по сигналу С9. Счетчик 7 сигналом СЗ наращивается на единицу

В следующих тактах все повторяется за исключением кодов А1 и А2, которые меняются так, что первый коммутатор k подключает новые группы разрядов, а сдвигатель 10 увеличивает число разрядов, на которое сдвигается результат умножения, кратно п-1.

В последнем такте первый коммутатор настраивается так, что выбирает следующую группу разрядов. Счетчик 7 находится в положении единицы, т.е. (11...1). Подключается поле памяти, где записана величина

1 у -2х

где X - п разрядов последней выбираемой группы. При этом в предпоследнем и последнем тактах сигнал С1 не оканчивается и результат с выхода сумма- торг 11 в регистр не записывается. Сигнал Ck тоже не подается, а выход блока 6 памяти отключен. Подаются сигналы С8 и С9. На вход накапливающего сумматора 9 поступает результат с выхода сумматора 11 через второй коммутатор 8 без целой единицы, которая обнуляется Эта величина прибавляется к предыдущему результату, хранимому в накапливающем сумматоре 9.

В завершающей стадии сигналы С1, С8 и С9 снимаются и в регистре 2 фиксируется результат, присутствующий на выходе сумматора И, а в накапливающем сумматоре 9 фиксируется текущий результат. Затем подаются сигналы СА и С9. По сигналу из последней области памяти считывается величина - 1/2 й5, которая и прибавляется к текущему результату. Таким образом, в сумматоре формируется величина

H lnX0-ln ft, -Inflj-...,,.

j lO2 + (Х,ц - 2 ft

которая и является приближенным логарифмом искомой величины, т.е. 1пХ.

Формула изобретения

Устройство для вычисления натурального логарифма, содержащее регистр, первый и второй коммутаторы, умножитель, первый блок постоянной памяти, накапливающий сумматор и блок синхронизации, отличающееся тем что, с целью упрощения устройства и повышения быстродействия, оно содержит сумматор, счетчик,второй блок постоянной памяти, сдвигатель и второй коммутатор, причем первый выход

блока синхронизации соединен с входом разрешения записи регистра, К-я (К 2,3,...,Р, где р - количество групп , выходов регистра; рб Ј 2,3 , , n/2i, п - число разрядов аргумента) группа выходов регистра соединена соответственно с К-й группой информационных входов первого коммутатора, причем

0 младший разряд 1-й (,3,...,)

группы выходов регистра является старшим разрядом j-й (,Р) группы выходов регистра, первая группа выходов регистра соединена с адрес5 ныяи входами первого блока постоянной памяти, выходы которого соединены с первой группой информационных входов первого коммутатора, выходы которого соединены с первыми информационными

0 входами умножителя и младшими адресными входами второго блока постоянной памяти, старшие адресные входы которого соединены с выходами счетчика, выходы второго блока постоянной

5 памяти соединены с первыми информационными входами второго коммутатора, выходы которого соединены с информационными входами накапливающего сумматора, вторые информационные входы вто0 рого коммутатора соединены с информационными входами устройства, с входами регистра и с выходами сумматора, входы первого слагаемого которого соединены через сдвигатель с выходами умножителя, входы второго слагаемого сумматора соединены с вторыми информационными входами умножителя и с выходами регистра, вход разрешения считывания первого блока постоянной памяти соединен с вторым выходом блока синхронизации, вход которого является входом запуска устройства, третий выход блока синхронизации соединен со счетным входом счетчика, четвертый

5 выход - с входом разрешения считывания второго блока постоянной памяти, пятый выход - с входом разрешения умножения умножителя, шестой выход - с входом разрешения пропуска первого

0 слагаемого сумматора, седьмой выход - с входом разрешения суммирования сумматора, восьмой выход - с управляющим входом второго коммутатора, девятый выход - с управляющим входом накапливающего сумматора, выход которого является выходом результата устройства, десятый выход блока синхронизации соединен с управляющим входом первого коммутатора одиннадцатый выход - с уп5

0

715593 58

равляющим входом сдвигателя, двенад-знака конца вычислений устройст

цатый выход является выходом при- ва.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции арктангенса | 1989 |

|

SU1661760A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Многоканальный цифровой фильтр | 1990 |

|

SU1751781A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для вычисления логарифмов чисел. Цель изобретения - упрощение устройства и повышение быстродействия. Поставленная цель достигается тем, что устройство содержит информационный вход 1, регистр 2, первый блок постоянной памяти 3, первый коммутатор 4, умножитель 5, второй блок постоянной памяти 6, счетчик 7, второй коммутатор 8, накапливающий сумматор 9, сдвигатель 10, сумматор 11, блок синхронизации 12, вход запуска 13, выход 14 признака конца вычислений, и информационный выход 15. Работа устройства основана на соотношениях: X=X0.1/β1.1/β2.....1/βN-1.ΑN

LNX=LNX0-LNβ1-...-LNβN-1+LNΑN. 1 ил.

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для логарифмирования | 1986 |

|

SU1388857A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-04-23—Публикация

1987-12-07—Подача