10

Изобретение относится к вычисли- тельной технике и может быть исполь- зовано для аппаратного вычисления логарифма числа.

Целью изобретения является повышение точности вычисления.

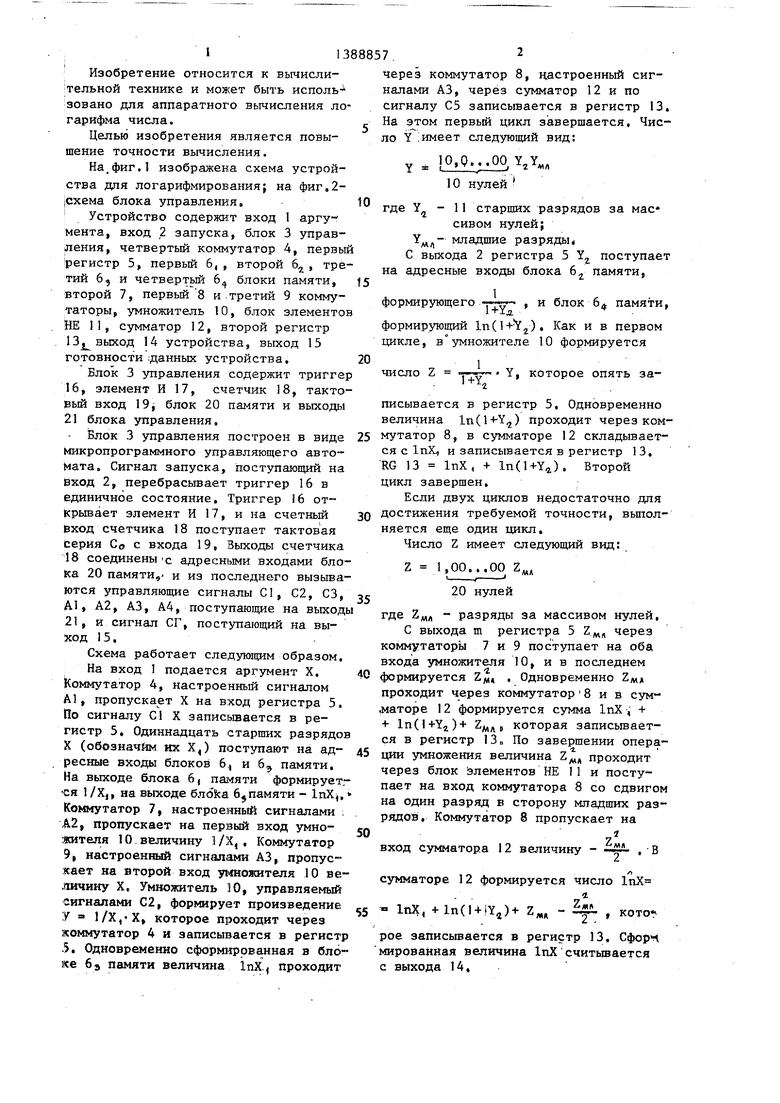

На.фиг.} изображена схема устройства для логарифмирования; на фиг,2- jcxeMa блока управления Устройство содержн:т вход 1 аргумента, вход 2 запуска, блок 3 управления, четвертый коммутатор 4, первый регистр 5, первый 6,, второй 6, третий 6, и четвертый 6 блоки памяти, fs второй 7, первый 8 и .третий 9 коммутаторы, умножитель 10, блок элементов НЕ I, сумматор 12, второй регистр 13j| выход 14 устройства, выход 15 готовности данных устройства, 20

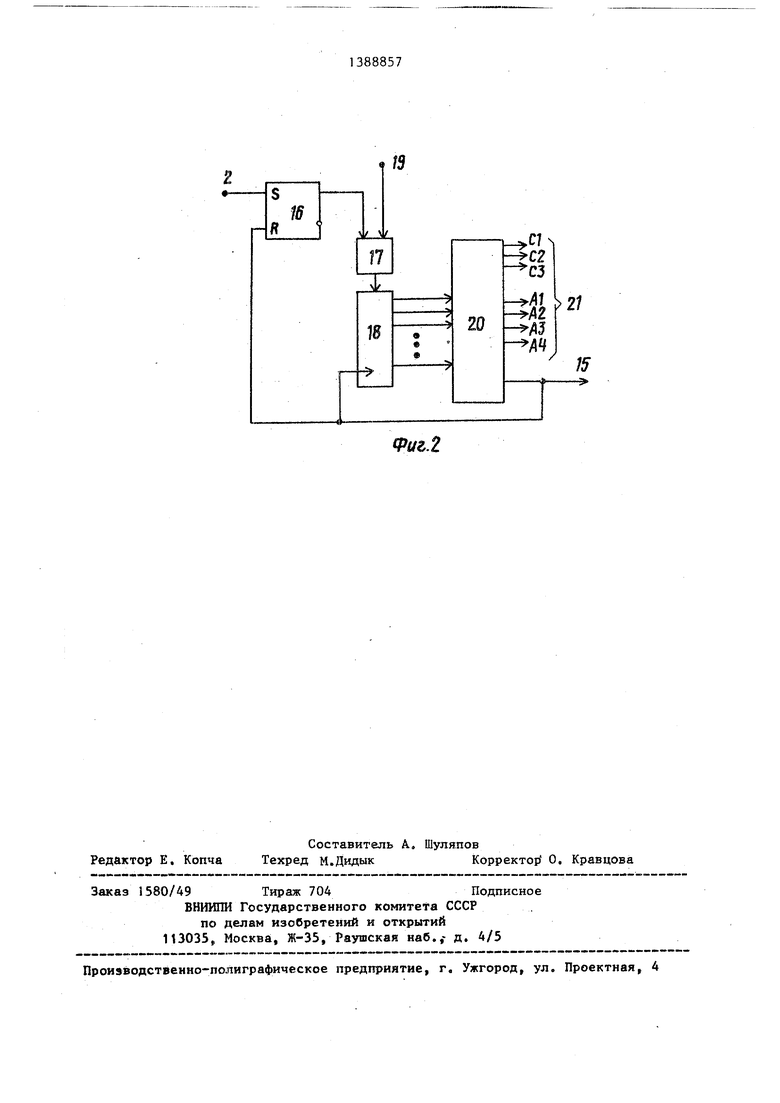

Блок 3 управления содержит триггер 16, элемент И 17, счетчик 18, тактовый вход 19j блок 20 памяти и выходы 21 блока управления.

Блок 3 управления построен в виде Микропрограммного управляющего авто- Мата, Сигнал запуска, поступающий на Вход 2, перебрасьгоает триггер 16 в единичное состояние. Триггер 16 открывает элемент И 17, и на счетный Вход счетчика 18 поступает тактовая Серия Со с входа 19, Выходы счетчика 18 соединены С адресными входами блока 20 памяти,- и из последнего вызываются управляющие сигналы С1, С2, СЗ, А1, А2, A3, А4, поступающие на выходы 21, и сигнал СГ, поступающий на выход 15,

Схема работает следуюищм образом.

На вход 1 подается аргумент X, Коммутатор 4, настроенный сигналом А1, пропускает X на вход регистра 5. По сигналу С1 X записьшается в регистр 5, Одиннадцать старших разрядов X (обозначим их X,) поступают на ад

1388857,2

через коммутатор 8, настроенный сигналами A3, через сумматор 12 и по сигналу С5 записывается в регистр 13, На этом первьм цикл завершается. Число Y :имеет следующий вид:

ДО.О.у.ОО ,

10 нулей

где Y - 11 старших разрядов за мае

сивом нулей; младшие разряды С выхода 2 регистра 5 Y поступает на адресные входы блока 6 памяти,

формирующего TTv

1+Хд.

и блок 6

памяти,

формирующий ln(). Как и в первом цикле, в°умножителе 10 формируется

число Z

1

1Ж И I

1+Y.

Y, которое опять записывается в регистр 5, Одновременно величина ln() проходит через ком- 25 мутатор 8, в сумматоре 12 складывается с InXi и записывается в регистр 13. RG 13 1пХ, + ln(l+Y), Второй цикл завершен,

Если двух циклов недостаточно дпя достижения требуемой точности, выполняется еще один цикл.

Число Z имеет следующий вид:

30

35

1,00,,,00 Z, 20 нулей

где , разряды за массивом нулей, С выхода m регистра 5 Z, через коммутаторы 7 и 9 поступает на оба входа умножителя 10, и в последнем формируется Zfm , Одновременно ZMX проходит через коммутатор 8 и в сумматоре 12 формируется сумма 1пХ , + + ln(l+Yj)+ которая записьшаётресные входы блоков 6,| и 6, памяти, На выходе блока 6, па;мяти формирует,- йя /X,, на выходе бл6 fca б памяти - InXj, Ко№1утатор 7, настроенный сигналами . А2, пропускает на первый вход умно- :Кителя 10.величину I/X,, Коммутатор 9, настроенный сигнгшами A3, пропускает на второй вход зп шожителя 10 ве- .пичину X, Умножитель 10, управляемый сигналами С2, формирует произведение У 1/Х,«Х которое проходит через жоммутатор 4 и записывается в регистр 5, Одновременно сформированная в блоке 6э памяти величина 1пХ проходит

ся в регистр 13 По завершении опера- 45 ции умножения величина Z проходит через блок Элементов НЕ 11 и поступает на вход коммутатора 8 со сдвигом на один разряд в сторону младших разрядов. Коммутатор 8 пропускает на

1

50

вход сумматора 12 величину ZM

В

сумматоре 12 формируется число lTiX

z:.

55 « InX, + ln(l-i-iY,j)+ Z - , KOTO T

рое записьгоается в регистр 13, Сфор мированная величина 1пХ считывается с выхода 14,

ДО.О.у.ОО ,

10 нулей

где Y - 11 старших разрядов за мае

сивом нулей; младшие разряды С выхода 2 регистра 5 Y поступает на адресные входы блока 6 памяти,

формирующего TTv

1+Хд.

и блок 6

памяти,

формирующий ln(). Как и в первом цикле, в°умножителе 10 формируется

Z

1

1Ж И I

1+Y.

Y, которое опять записывается в регистр 5, Одновременно величина ln() проходит через ком- мутатор 8, в сумматоре 12 складывается с InXi и записывается в регистр 13. RG 13 1пХ, + ln(l+Y), Второй цикл завершен,

Если двух циклов недостаточно дпя достижения требуемой точности, выполняется еще один цикл.

Число Z имеет следующий вид:

1,00,,,00 Z, 20 нулей

где , разряды за массивом нулей, С выхода m регистра 5 Z, через коммутаторы 7 и 9 поступает на оба входа умножителя 10, и в последнем формируется Zfm , Одновременно ZMX проходит через коммутатор 8 и в сумматоре 12 формируется сумма 1пХ , + + ln(l+Yj)+ которая записьшаётся в регистр 13 По завершении опера- ции умножения величина Z проходит через блок Элементов НЕ 11 и поступает на вход коммутатора 8 со сдвигом на один разряд в сторону младших разрядов. Коммутатор 8 пропускает на

1

вход сумматора 12 величину ZM

В

сумматоре 12 формируется число lTiX

z:.

55 « InX, + ln(l-i-iY,j)+ Z - , KOTO T

рое записьгоается в регистр 13, Сфор мированная величина 1пХ считывается с выхода 14,

Формула изобретения

1. Устройство для логарифмирования, содержащее сумматор, первый и второй регистры, первьш и второй коммутаторы, первый и второй блоки памяти, блок управления, причем выходы старших разрядов первого регистра соединены с адресными входами перво- го блока памяти, выход первого коммутатора соединен с входом первого операнда сумматора, выход которого соединен с информационным входом второго регистра, выход которого соединен с выходом функции устройства, первый, второй, третий и четвертый выходы блока управления соединены соответственно с входами записи первого и второго регистров, управляющими вхо-. дами первого и второго коммутаторов, отличающееся тем, что, с целью повышения точности вычисления, в него введены третий и четвертый

блоки памяти, третий и четвертый ком-25 входами умножителя, третьего и четмутаторы, з ножитель и блок элементов НЕ, причем выход первого блока памяти соединен с первым информационным входЬм второго коммутатора, выходы старших разрядов первого регистра соединены с адресными входами третьего блока памяти, выход которого соединен с первым информационным входом первого коммутатора, выходы средних разрядов первого регистра соединены с адресными входами второго и четвер того блоков памяти, выходы которых соответственно соединены с вторыми информационными ёходами второго и . первого коммутаторов, третьи информационные входы которых соединены с выходами младших разрядов первого регистра, выходы которого соединены с первым информационным входом третье30

-35

40

вертого коммутаторов, с выходом готовности данных устройства,

2. Устройство по п,1, о т л и ч а ющ е е с я тем, что блок управления содержит блок памяти, счетчик, триггер и элемент И, первый вход которого соединен с тактовым входом устрой ства, вход запуска которого соединен с установочным входом триггера, прямой выход которого соединен с вторым входов элемента И, выход которого со единен со счетным входом счетчика, выходы которого соединены с адресными входами блока памяти, с первого по восьмой выходы которого соединены соответственно с первого по восьмой выходами блока управления, восьмой выход блока памяти соединен с входами сброса счетчика и триггера.

го коммутатора, вторые информационные входы которого соединены с выходами младших разрядов первого регистра, информационный вход которого соединен с выходом четвертого коммутатора, первый информационный вход которого соединен с входом аргумента устройства, выход второго и третьего коммутаторов соединены с входами первого и второго сомножителей умножителя, выход которого соединен с входом блока элементов НЕ и вторым информационным входом четвертого коммутатора, выход второго регистра соединен с входом операнда сумматора, вы- ходы блока элементов НЕ- соединены со сдвинутыми на один разряд вправо четвертыми информационными входами первого коммутатора, вход запуска уст- ройства соединен с управляющим входом блока управления, пятый, шестой, седьмой и восьмой выходы которого соединены соответственно с управляющими

30

35

40

вертого коммутаторов, с выходом готовности данных устройства,

2. Устройство по п,1, о т л и ч а- ющ е е с я тем, что блок управления содержит блок памяти, счетчик, триггер и элемент И, первый вход которого соединен с тактовым входом устройства, вход запуска которого соединен с установочным входом триггера, прямой выход которого соединен с вторым входов элемента И, выход которого соединен со счетным входом счетчика, выходы которого соединены с адресными входами блока памяти, с первого по восьмой выходы которого соединены соответственно с первого по восьмой выходами блока управления, восьмой выход блока памяти соединен с входами сброса счетчика и триггера.

.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство обнаружения и определения координат объекта на изображении | 1990 |

|

SU1737755A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

Изобретение относится к области вьиислительной техники и может быть использовано при построении быстродействующих цифровых вычислительных машин. Целью изобретения является по- вьшение точности вычисления. Устройство содержит вход аргумента 1, вход запуска 2, блок управления 3, четвертый коммутатор 4, первый регистр 5, .первый, второй, третий и четверТЕ й блоки памяти 6|, 6, 6, и 6,, второй, первый и третий коммутаторы 7, 8 и 9, умножитель 10, блок элементов НЕ 1, сумматор 12, второй регистр 13, выход устройства 14, выход готовности данных устройства 15. 1 з.п. ф-лы, 2 ил.

| Устройство для вычисления логарифма числа | 1979 |

|

SU860067A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-15—Публикация

1986-11-17—Подача