Изобретение относится к области вычислительной техники и может быть использовано при построении буферных запоминающих устройств в системах , сбора, передачи и обработки данных, в частности в устройствах сбора информации QT цифровых датчиков в системах телеметрии.

Цель изобретения - расширение функциональных возможностей запоминающего устройства за счет анализа входных дачных и исключения записи в накопитель, малоизменяющихся данных.

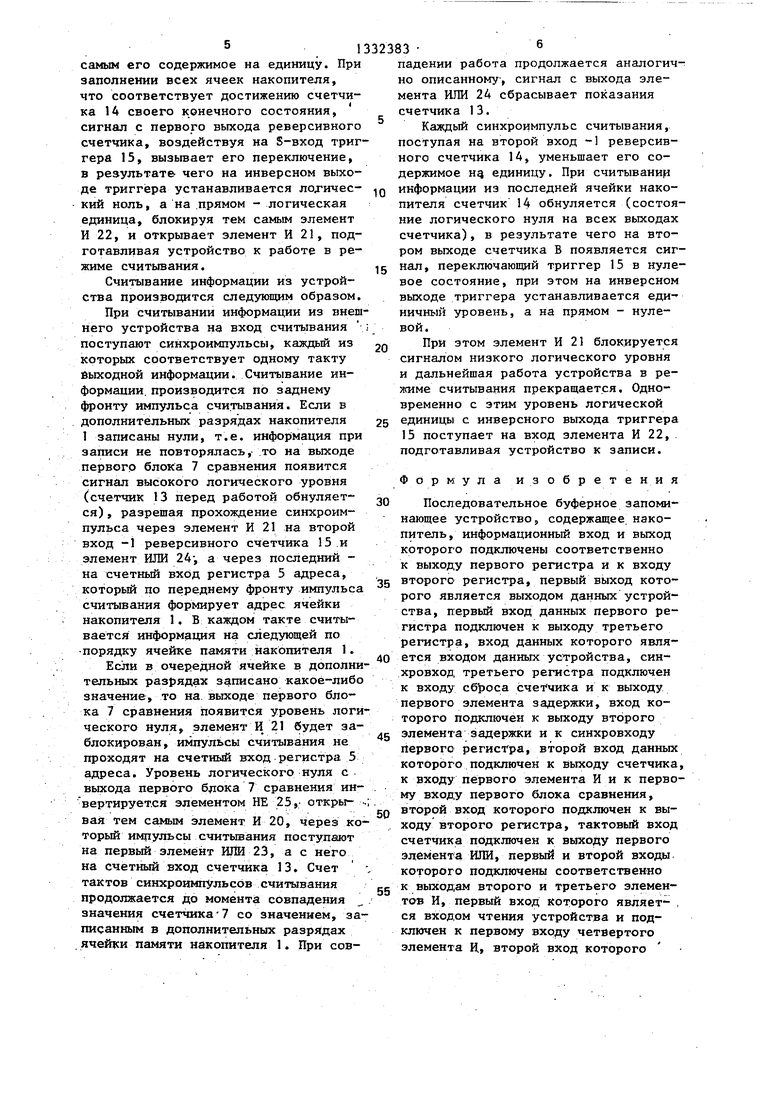

На чертеже представлена структурная схема последовательного буферного запоминающего устройства.

Последовательное буферное запоминающее устройство содержит накопитель 1, первый 2, второй 3 и третий 4 регистры, четвертый регистр 5 адреса, дешифратор 6, первый 7, второй 8 и третий 9 блоки сравнения, первый 10 и второй 11 мультиплексоры, сумматор 12, счетчик 13, реверсивный счетчик 14, триггер 15, первый 16 и второй 17 элементы задержки, элементы И 18 - 22 с первого по пятый, первый 23 и второй 24 элементы ИЛИ и первый 25 и второй 26 элементы НЕ„

Устройство работает следующим образом.

Перед работой регистры, счетчики и триггер 15 приводятся в исходное состояние. При этом элемент И 21 заблокирован сигналом низкого логического уровня с прямого выхода триггера 15„ в то же время сигнал высокого логического уровня на первом входе элемента И 22 разрешает прохождение синхроимпульса записи. Входная информация параллельным кодом поступает одновременно на входы данных регистра 4 и на первые входы (А) блока 9 сравнения, который выполняет сравнение его с кодом, записанным в регистре 4 в предыдущем цикле записи и поступающим с его выхода на вторые входы (В) блока 9 .сравнения. Если значение кода на первых входах (А) больше либо равно значению кода на вторых входах (В), то на втором выходе (А Т) В) блока 9 сравнения появляется сигнал, который поступае.т на вторые входы управления мультиплексоров 10 и 11 и переключает их в такое состояние, что на выход первого мультиплексора 10 поступают данные с его первого входа данных, а на вькод второго мультиплексо

ра 11 - данные с его второго входа данных.

Таким образом, на первые входы (А) сумматора 12 поступают через

мультиплексор 10 входные данные в прямом коде, на его вторые входы (В) через инверсный выход мультиплексора

11- данные из регистра 4 в инверс-i- ном коде, а на третий вход (вход заема сумматора) - логическая единица. Сумматор 12 производит вычитание из числа, поступившего на вход А, числа, поступившего на вход В по методу второго дополнения, который реализуется следующим образом. Сумматор 12 выполняет сложение числа на первом (А) входе, представленного в прямом коде, числа на втором (В) входе, представленном в обратном коде, и прибавляет к полученной сумме единицу младшего разряда, поступающую на третий (Ро) выход заема. В результате на выходе сумматора 12 формируется число, равное разности между значением входной информации и числом, записанным в регистре 4 в предыдущем цикле записи.. 1

Если число на входе А блока 9 сравнения меньше числа, поступающего на вход В, то на его выходе А ; В появляется сигнал, поступающий на первые входы управления ryльтиплeкco- ров 10 и 11 и переключающий их таким образом, что на входы А сумматора

12поступает число из регистра 4,

а на входы В - число с входа, данных устройства. Далее на выходе сумматора появится разность чисел аналогично описанному, однако это будет разность между числом, записанным в регистре 4 в предыдущем цикле записи, и числом, находяш 1Мся на входе устройства. Таким образом, на выходах сумматора 12 формируется число, представляющее собой модуль разности указанных чисел, которое поступает на вторые входы А второго блока 8 сравнения. На третьи входы В этого блока поступает число с входа кода приращения устройства. Блок 8 сравнения сравнивает числа на входах А и В и в случае, если А В, на выходе (А : В) блока появляется сигнал и разрешает прохождение инхроимпуль- са записи через элемент И 22, второй элемент ИЛИ 24 на синхровход регистра 5 адреса, который формирует но

- .3

вый адрес для записи слова входной информации.

Кроме того, синхроимпульс записи с выхода второго элемента ИЛИ 24 через элемент 17 задержки поступает на синхровход регистра 2, при этом информация с вьгхода регистра 4 переписывается в основные, а состояние счетчика 13 - в дополнительные разряды ячейки накопителя 1. Через первьй и второй элементы 16 и 17 задержки синхроимпульс записи поступает на вход Сброс счетчика 13, обнуляя его, и на синхровход регистра 4, при этом информация, присутствующая на входе устройства, запишется в регистр .

Дальнейшая запись поступающей информации происходит аналогично.

Если, начиная с какого-либо момента времени, входная информация остается неизменной либо ее изменение по абсолютной величине не превьшает значения числа заданного на входах кода приращения информации, то, появившись на входе устройства впервые, с приходом очередного синхроимпульса записи она записывается в регистр 4, после чего блок 8 сравнения, сравнивая значения информации на входах А и В, установит факт А В и на входе блока (А В) появится сигнал низкого логического уровня и, блокируя элемент И 22, запретит прохождение последующих синхроимпульсов записи на синхровход , регистра 5 адреса и другие узлы устройства.

Уровень логического нуля, посту- пая на вход элемента НЕ 26f инвертируется и разрешает прохождение синхроимпульсов записи через элемент И 19, первый элемент ИЛИ 23 на счетный вход двоичного счетчика 13, который считает количество тактов повторяющейся информации.

Как только входная информация изменится настолько, что абсолютная величина разности входной информации и числа в регистре 4 превысит значение кода приращения, сигнал с вьгхода блока 8 сравнения уровнем логической единиць разрешит прохождение синхроимпульса записи через первый элемент 22 на узлы устройства и запретит его прохождение на синхровхоД . счетчика 13 через второй элемент И 19, так как на его вход поступит уровень логического нуля с выхода эле20

32383 .

мента НЕ 26. С вьпсода элемента И 22 синхроимпульс записи через второй элемент ИЛИ 24 поступает на счетный вход регистра 5 адреса, где формируется новый адрес для записи числа в накопитель. Синхроимпульс записи через элемент 17 задержки поступает на -синхровход регистра 2 и информа- д ция из регистра 4 перепишется в основные, а состояние счетчика 13 - в дополнительные разряды ячейки памяти накопителя 1 . С вьгхода элемента 17 задержки синхроимпульсы записи посту- g пают на вход элемента 16,задержки, ас его выхода на вход Сброс счетчи- ка 13, обнуляя его, и на синхровход регистра 4, записывая в него новую информацию.

Если абсолютная величина разности входной информации и информации в регистре 4 числа равна нулю либо не превьщ1ает значения числа, заданного на входах кода приращения устройства, 25 а число циклов записи такое, что счетчик 13 под воздействием многократных тактовых импульсов достигает своего конечного состояния - на выходах всех его разрядов устанавлнвают- ,, ся логические единицы, то элемент И 18 открывается и на его выходе появляется уровень логической единицы, который, поступая на вход А .В второго блока 8 сравнения, вызывает появление на его выходе сигнала логи- ческой единицы. Этот сигнал блокирует элемент И 19 и открывает элемент И 22, в результате чего последующий синхроимпульс записи через элементы И 22 и ИЛИ 24 поступает на счетный вход регистра 5 адреса, который формирует новый адрес для записи слова входной, информации.

Далее устройство выполняет запись информации с выходов регистра 4 в основные, а состояния счетчика 13 - в дополнительные разряды ячейки накопителя 1 аналогично описанному, после чего в регистр 4 перепишется информация, присутствующая в данный момент на входах устройства, а счетчик 13 обнулится.

Дальнейшая запись информации, поступающей на вход устройства, происходит аналогично.

Казедь1й синхроимпульс записи, по- (ступаюпцй на регистр 5 адреса, поступает также на первый вход +1 реверт сивного счетчика 14, увеличивая тем

0

5

0

5

ь1

самым его содержимое на единицу. При заполнении всех ячеек накопителя, что соответствует достижению счетчика 14 своего конечного состояния, сигнал с первого выхода реверсивного счетчика, воздействуя на S-вход триг гера 15, вызьгоает его переключение, в результате чего на инверсном выходе триггера устанавливается лод ичес- кий ноль, а на прямом - логическая единица, блокируя тем самым элемент И 22, и открывает элемент И 21, подготавливая устройство к работе в режиме считывания.

Считывание информации из устройства производится следующим образом.

При считывании информации из внеш него устройства на вход считывания поступают синхроимпульсы, каждый из которых соответствует одному такту Выходной информации. Считывание информации, производится по заднему фронту импульса считывания. Если в дополнительных разрядах накопителя 1 записаны нули, т.е. информация при записи не повторялась, то на выходе первого блока 7 сравнения появится сигнал высокого логического уровня (счетчик 13 перед работой обнуляется) , разрешая прохождение синхроимпульса через элемент И 21 на второй вход -1 реверсивного счетчика 15 и элемент ИЛИ 24; а через последний - на счетный вход регистра 5 адреса, который по переднему фронту импульса считьюания формирует адрес ячейки накопителя 1. В каждом такте считывается информация на следующей по -порядку ячейке памяти накопителя 1.

Если в очередной ячейке в дополни тельных разрядах записано какое-либо значение, то на выходе первого блока 7 сравнения появится уровень логи ческого нуля, элемент И 21 будет заблокирован, импульсы считывания не проходят на счетный вход регистра 5 адреса. Уровень логического нуля с выхода первого блока 7 сравнения ин- вертирует.ся элементом НЕ 25,- откры- вая тем самым элемент И 20, через который импульсы считьшания поступают на первый элемент ИЛИ 23, а с него на счетный вход счетчика 13. Счет тактов синхроимпульсов считывания продолжается до момента совпадения значения счетчика-7 со значением, записанным в дополнительных разрядах ячейки памяти накопителя 1. При сов32383

падении работа продолжается аналогично описанному, сигнал с выхода элемента ИЛИ 24 сбрасывает показания счетчика 13.

Каждьй синхроимпульс считывания, поступая на второй вход -1 реверсивного счетчика 14, уменьшает его содержимое н единицу. При считывании

Q информации из последней ячейки нако- пителя счетчик 14 обнуляется (состояние логического нуля на всех выходах счетчика), в результате чего на втором выходе счетчика В появляется сиг15 нал, переключающий триггер 15 в нулевое состояние, при этом на инверсном выходе триггера устанавливается единичный уровень, а на прямом - нулевой.

2Q При этом элемент И 21 блокируется сигналом низкого логического уровня и дальнейшая работа устройства в ре- ясиме считывания прекращается. Одновременно с этим уровень логической

25 единицы с инверсного выхода триггера 15 поступает на вход элемента И 22, . подготавливая устройство к записи.

Формула изобретения

30 Последовательное буферное запоминающее устройство, содержащее накопитель, информационный вход и выход которого подключены соответственно к выходу первого регистра и к входу

35 второго регистра, первый выход которого является выходом данных устройства, первьй вход данных первого регистра подключен к выходу третьего регистра, вход данных которого явля40 ется входом данных устройства, син- хровход третьего регистра подключен к вход сброса счетчика и к выходу первого элемента задержки, вход которого подключен к выходу второго

45 злемента задержки и к синхровходу Первого регистра, второй вход данных которого подключен к выходу счетчика, к входу первого элемента Ник первому входу первого блока сравнения,

5Q второй вход которого подключен к выходу второго регистра, тактовый вход счетчика подключен к выходу первого элемента ИЛИ, первый и второй входы которого подключены соответственно

55 к выходам второго и третьего элемен- тав И, первый вход которого являет- , ся BxofliOM чтения устройства и подключен к первому входу четвертого элемента И, второй вход которого

7,

подключен к выходу первого бЛока сравнения и к входу первого элемента НЕ , выход которого подключен к второму входу третьего элемента И, третий вход четвертого элемента И подключен к прямому выходу триггера, инверсный выход которого подключен к первому входу пятого элемента И, второй вход которого подключен к вы- хору второго блока сравнения и к входу второго элемента НЕ, выход которого подключен к первому входу второго элемента И, второй вход которого является входом записи устройства и подключен к третьему входу пятого элемента И, выход которого подключен к входу сложения реверсивного счетчика и к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И и к входу вычитания реверсивного счетчика, выход второго элемента ИЛИ подключен к входу второго элемента задержки и входу регистра адреса, выход которого подключен к входу дешифратора, выход которого подключен к адресным входам накопителя, первый и второй выходы реверсивного счетчика подключены соответственно к входам установки и сброса триггера, выСоставитель С. Щустенко, Редактор Л. Гратилло Техред Л.Сердюкова Корректор С, Шекмар

Заказ 3839/48

Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

323838

ход первого элемента И подключен к первому входу второго блока сравнения, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет анализа входных данных и исключения записи в накопитель малоизменяющихся данных, оно содержит третий блок

10 сравнения, первый и второй мультиплексоры и сумматор, выход которого подключен к второму входу второго блока сравнения, третий вход крторо- го является входом кода приращения

5 устройства, первый и второй входы даннйх сумматора подключены к вьрсодам соответственно первого и инверсным выходам второго мультиплексоров, первые и вторые управляющие входы кото20 рых подключены соответственно к первому и второму выходам третьего блока сравнения, первый вход которого подключен к первым входам данных первого и второго мультиплексоров и к

25 входу данных третьего регистра, выходы которого подключены к второму входу третьего блеска сравнения, к вторым входам данных первого и второго мультиплексоров, вход переноса

0 сумматора подключен к входу логической единицы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1397968A1 |

| Запоминающее устройство | 1984 |

|

SU1257700A2 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

Изобретение отиосится к вычислительной технике и может быть использовано при построении буферных запо iykmySlLm k . -г- 9 . - « . И - м Чт: 4 „ минающих устройств в системах сбора передачи и обработки данных, в частности в устройствах сбора информации от цифровых датчиков в системах телеметрии. Цель изобретения - расширение функциональных возможностей запоминающего устройства за счет анализа входных данных и исключения записи в накопитель малоизменяющихся данных. Устройство содержит накопитель 1, регистры 2 - 5 адреса, дешифратор 6, блоки сравиения 7-9, мультиплексо- ры 10, 11, сумматор 12, счетчик 13, реверсивиый счетчик 14, триггер 15, элементы задержки 16, 17, элементы И 18 - 22, элементы ИЛИ 23, 24 и элементы НЕ 25j 26. 1 нп. i (Л

| Запоминающее устройство | 1984 |

|

SU1177856A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Запоминающее устройство | 1984 |

|

SU1257700A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-08-23—Публикация

1986-03-10—Подача