10.

п

102

Wi

i

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Фурье при многоканальной обработке информации | 1983 |

|

SU1124324A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Процессорный модуль | 1989 |

|

SU1674111A1 |

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для быстрого преобразования фурье | 1981 |

|

SU1018123A1 |

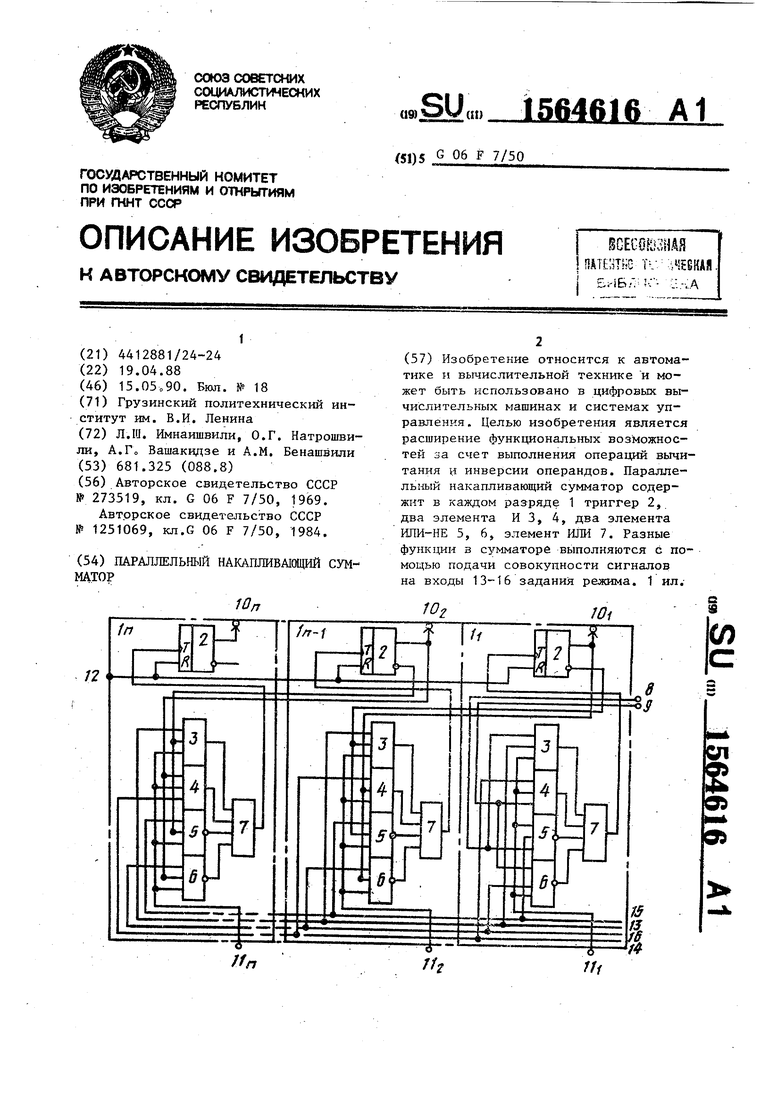

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных машинах и системах управления. Целью изобретения является расширение функциональных возможностей за счет выполнения операций вычитания и инверсии операндов. Параллельный накапливающий сумматор содержит в каждом разряде 1 триггер 2, два элемента И 3,4, два элемента ИЛИ-НЕ 5,6, элемент ИЛИ 7. Разные функции в сумматоре выполняются с помощью подачи совокупности сигналов на входы 13-16 задания режима. 1 ил.

Лп

ел

г

а 5

/ft

111

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных машинах и системах управ- ле|ния.

Цель изобретения - расширение функциональных возможностей за счет выполнения операций вычитания и инверсии операндов,,

j На чертеже представлена схема параллельного накапливающего сумматора

Параллельный накапливающий сумматор содержит в каждом разряде 1k

(k

эл

1-п) триггер 2, первый и второй

ементы И 3 и 4 соответственно, первый и второй элементы ИЛИ-НЕ 5 и 6 соответственно, элемент ИЛИ 7, входы

и 9 соответственно единичного и ну левого потенциалов сумматора, выходы

)-10п разрядов сумматора, информационные входы у, разрядов сумматора, вход 12 сброса сумматора и с первого по четвертый входы 13-16 задания режима сумматора соответственно.

Сумматор работает следующим образом.

Параллельный накапливающий сумматор позволяет реализовать функции суммирования и вычитания двоичных операндов, функцию статического ре

гистра с синхронизированным приемом двоичного кода функцию синхронизированного инверсного приема двоичного кода и функцию инвертирования содержимого сумматора. На входы 13, 14 и 15, 16 подаются прямое и инверсное значения сигналов задания вида операции соответственно.

Для сложения двоичных операндов предварительно сумматор обнуляется по дачей высокого уровня сигнала на 12 сумматора

Следовательно, все триггеры 2 су шатора переходят в нулевое состояние. Разрешающий сигнал подается на взводы 13 и 16. В результате первый элемент И 3 и первый элемент ИЛИ-НЕ 5 оказываются подготовленными для приема информации. При этом на ВЫХОДА первого элемента ИЛИ-НЕ 5 первого разряда присутствует низкий потенци- ajt, поскольку на его третий вход постоянно подается высокий потенциал с входа 8. Разряды кода первого one- ранда подеются на информационные входы сумматора. Предположим,

5

0

5

5

0

5

0

5

что первьй операнд подготовлен кодом 1001 (п 4). В первом разряде единица проходит через первый элемент И 3 и элемент ИЛИ 7 и на счетном входе триггера 2 устанавливает высокий потенциал. Такой же процесс происходит в четвертом разряде сумматора. В сумматоре применены Т-триг- геры со статико-динамическим управле- нием, изменяющие свое состояние на задних фронтах входных сигналов, поэтому состояния триггеров 2 в первом и четвертом разрядах не меняются. После этого первьй операнд 1001 снимается с входов 114-111 и, следовательно, на них устанавливаются низкие потенциалы. В результате на счетных входах триггеров 2 первого и четвертого разрядов появляются низкие потенциалы, следовательно, они переходят в единичное состояние. Низкий потенциал с инверсного выхода триггера 2 первого разряда подается на третий вход первого элемента ИЛИ-НЕ 5 второго разряда и на счетном входе триггера 2 второго разряда устанавливает высокий потенциал. Высокий потенциал устанавливается также на счетном входе триггера 2 пятого разряда. После этого сумматор готов для приема второго операнда.

Второй операнд подается также на информационные входы . Предположим, что второй операнд представлен кодом 0111. При этом на счетных входах триггеров 2 первого и третьего разрядов появляются высокие потенциалы, поскольку входные логические единицы проходят через первые элементы И 3 соответствующих разрядов. Во втором разряде единица с информационного входа 11г подается на первый вход первого элемента ИЛИ-НЕ 5 и на его выходе устанавливает низкий потенциал. Следовательно, триггер 2 второго разряда переходит в единичное состояние. Низкий потенциал с инверсного выхода триггера 2 второго разряда закрывает первый элемент И 3 третьего разряда и переводит соответствующий триггер 2 в единичное состояние. Таким образом, в триггерах 2 записывается код 1111. После этого с информационных входов 114-114 снимается второй операнд. На счетных входах триггеров 2 второго, третьего и четвертого разрядов устанавливаются высокие потенциалы, а на счетном входе триггера 2 первого разряда - низкий потенциал. В результате триггер 2 первого разряда переходит в нулевое состояние, высокий потенциал с инверсного выхода которого устанавливает на выходе первого элемента ИЛИ-НЕ 5 и на счетном входе триггера 2 второго разряда низкий потенциал. Триггер 2 второго разряда переходит в нулевое состояние, в свою очередь, переводят триггер 2 третьего разряда в нулевое состояние и т.д. В результате во всех четырех разрядах сумматора записывается код 0000 (при этом пятый разряд сумматора переходит в единичное состояние). Для вычитания двоичных операндов разрейающий сигнал подается на входы 14 и 15. В результате вторые элемент И 4 и ИЛИ-НЕ 6 оказываются подготов- тенными для приема информации. При этом на выходе второго элемента И 4 первого разряда присутствует низкий потенциал, поскольку на его третий вход постоянно подается низкий потенциал с входа 9. Предположим, что в разрядах сумматора предварительно введено уменьшаемое, представляющее собой код 10000. Разряды вычитаемого операнда подаются на информационные входы 11п-114 сумматора. Предположим, что вычитаемое представлено кодом 0111. В первом разряде единица на первом входе второго элемента ИЛИ- НЕ 6 устанавливает на его выходе низкий потенциал, который через элемент ИЛИ 7 на счетном входе триггера 2 этого разряда образует задний фронт управляющего сигнала, который переводит его в единичное состояние. Такой же процесс происходит во втором и третьем разрядах сумматора. Высокий потенциал с прямого выхода триггера 2 первого разряда открывает второй элемент И 4 второго разряда и устанавливает на входе соответствующего триггера 2 высокий потенциал. Такой же процесс происходит в третьем разряде сумматора. Высокий потенциал с прямого выхода триггера 2 третьего разряда устанавливает на выходе второго элемента ИЛИ-КЕ 6 чет-; вертого разряда нулевой потенциал, который через элемент ИЛИ 7 подается на счетный вход триггера 2. В триггере 2 четвертого разряда устанавливается единичное состояние.

10

0

5

После этого операнд 0111 снимается с информационных входов . На счетных входах триггеров 2 второго и третьего разрядов устанавливаются низкие потенциалы. В результате триггеры 2 второго и третьего разряда переходят в нулевое состояниес

Функция статического регистра с v синхронизированным приемом двоичного кода осуществляется следующим образом.

Предварительно сумматор обнуляется подачей сигнала на вход 12 . Опе- 5 ранд подается на информационные входы 11п-11,,. Синхросигнал подается через вход 13 сумматора.

Функция статического регистра синхронизированного инверсного приема двоичного кода осуществляется следующим образом.

Предварительно сумматор обнуляется подачей сигнала на вход 12. ПошГе . этого на входы 13 и 14 одновременно подается синхросигнал. На выходах вторых элементов ИЛИ-НЕ 6 разрядов сумматора устанавливаются высокие потенциалы, которые через элементы ИЛИ 7 подаются на счетные входы соответствующих триггеров 2 разрядов сумматора. После этого синхросигнал снимается с входов 13 и 14 сумматора. На выходах вторых элементов ИЛИ-НЕ 6 разрядов сумматора устанавливаются низкие потенциалы, которые через элементы ИЛИ 7 на счетных входах триггеров 2 разрядов сумматора образуют задние фронты управляющих сигналов, которые переводят их в единич- Q ное состояние.. Принимаемый операнд подается на информационные входы 11п-11, а синхросигнал приема - на вход 14, В триггерах 2 устанавливается инверсия двоичного операнда.

Функция инвертирования содержимого сумматора осуществляется следующим образом.

Синхросигнал подается на входы 13 и 14. На выходах первых элементов ИЛИ-НЕ 5 или вторых элементов ИЛИ-НЕ 6, что зависит от содержимого предыдущего разряда, устанавливаются высокие потенциалы, которые через элементы ИЛИ 7 подаются на счетные . входы триггеров 2 разрядов сумматора. После этого синхросигнал снимается с входов 13 к 14„ На счетных входах триггеров 2 разрядов сумматора образуются задние фронты управ0

5

5

0

5

ляющих сигналов. В триггерах 2 разрядов сумматоров устанавливается ин- Йерсия кода содержимого, формула изобретения

Параллельный накапливающий сумма- фор, содержащий в k-M разряде (k f...n, n - разрядность числа) триг- tfep, первый и второй элементы И, nep элемент ИЛИ-НЕ и элемент ИЛИ, 1|фичем вход сброса сумматора соедине с; входами установки в О триггеров разрядов сумматора, прямые выходы ко торых являются выходами сОответст- кующих разрядов сумматора, выходы первого и второго элементов И k-ro разряда сумматора соединены с соответствующими входами элемента ИЛИ k-ro разряда сумматора, информацион- пый вход k-ro разряда сумматора сое- линен с первыми входами первого и второго элементов И k-ro разряда сумматора, инверсный выход триггера k-ro разряда сумматора соединен с иторым входом первого элемента И (k+1)-ro разряда сумматора, о т л и : а ю щ и и с я тем, что, с целью расширения функциональных возможностей за счет выполнения операций вы- питания и инверсии операндов, он со- 4ержит в k-м разряде второй элемент

ИЛИ-НЕ, причем выходы первого и второго элементов ИЛИ-НЕ k-ro разряда сумматора соединены соответственно с третьим и четвертым входами элемента ИЛИ k-ro разряда сумматора, выход которого соединен со счетным входом триггера k-ro разряда сумматора, информационный вход k-ro разряда сумматора соединен с первыми входами первого и второго элементов ИЛИ-НЕ k-ro разряда сумматора, с первого по четвертый входы задания режима сумматора соединены с третьими входами v первых элементов И и с вторыми входами вторых элементов И, первых элементов ИЛИ-НЕ и вторых элементов ИЛИ-НЕ разрядов сумматора соответст- -венно, второй вход первого элемента И k-ro разряда сумматора соединен с ( третьим входом первого элемента ИЛИ- НЕ k-ro разряда сумматора, прямой выход триггера k-ro разряда сумматора соединен с третьими входами вторых элементов И и ИЛИ-НЕ (k+1)-ro разряда сумматора, входы единичного и нулевого потенциалов сумматора соединены соответственно с вторым входом первого элемента И и с объединенными третьими входами вторых элементов И и ИЛИ-НЕ первого разряда сумматора.

| НАКАПЛИВАЮЩИЙ СУММАТОР | 0 |

|

SU273519A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Накапливающий сумматор | 1984 |

|

SU1251069A1 |

Авторы

Даты

1990-05-15—Публикация

1988-04-19—Подача