Изобретение относится к автоматике и вычислительной технике, может быть использовано для контроля логических блоков и схем и является дополнительным к авт.св. N 1332322,

Цель изобретения - повышение достоверности контроля.

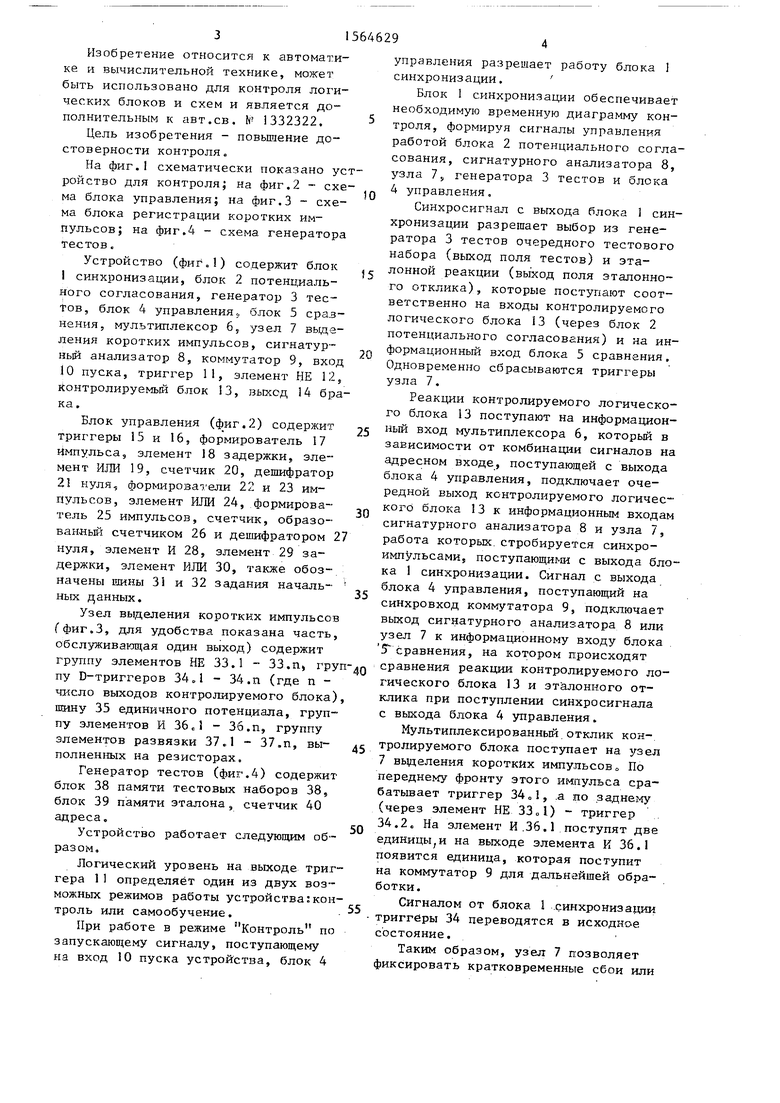

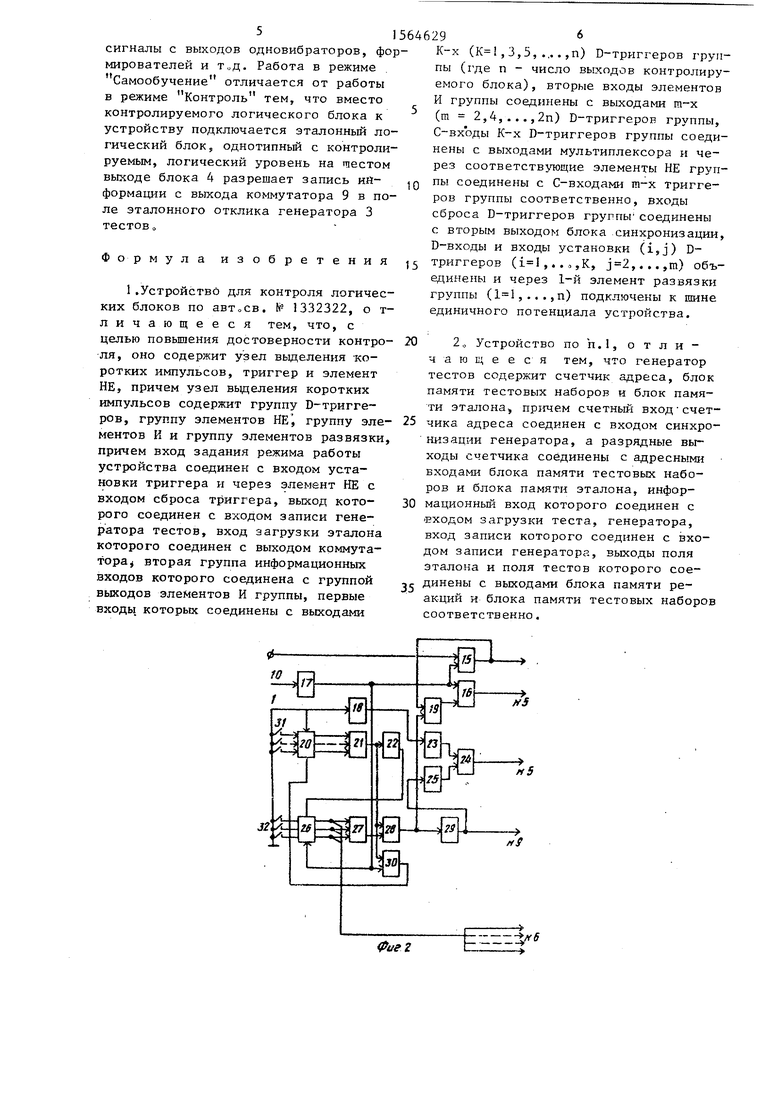

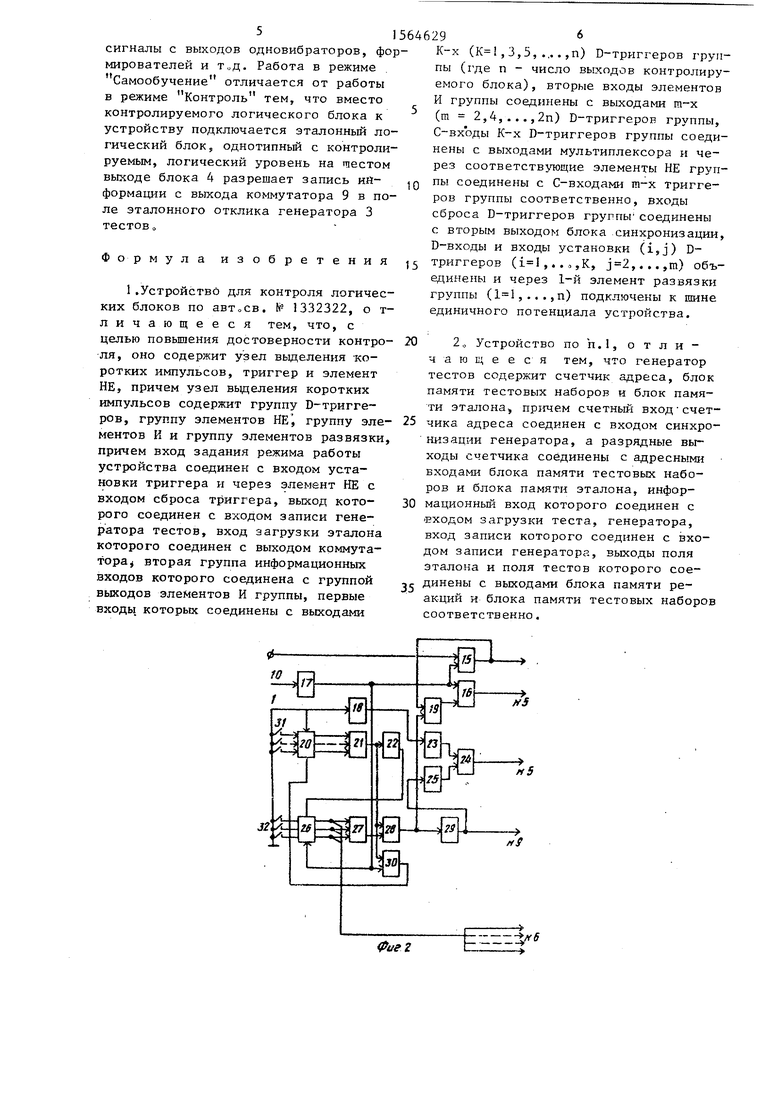

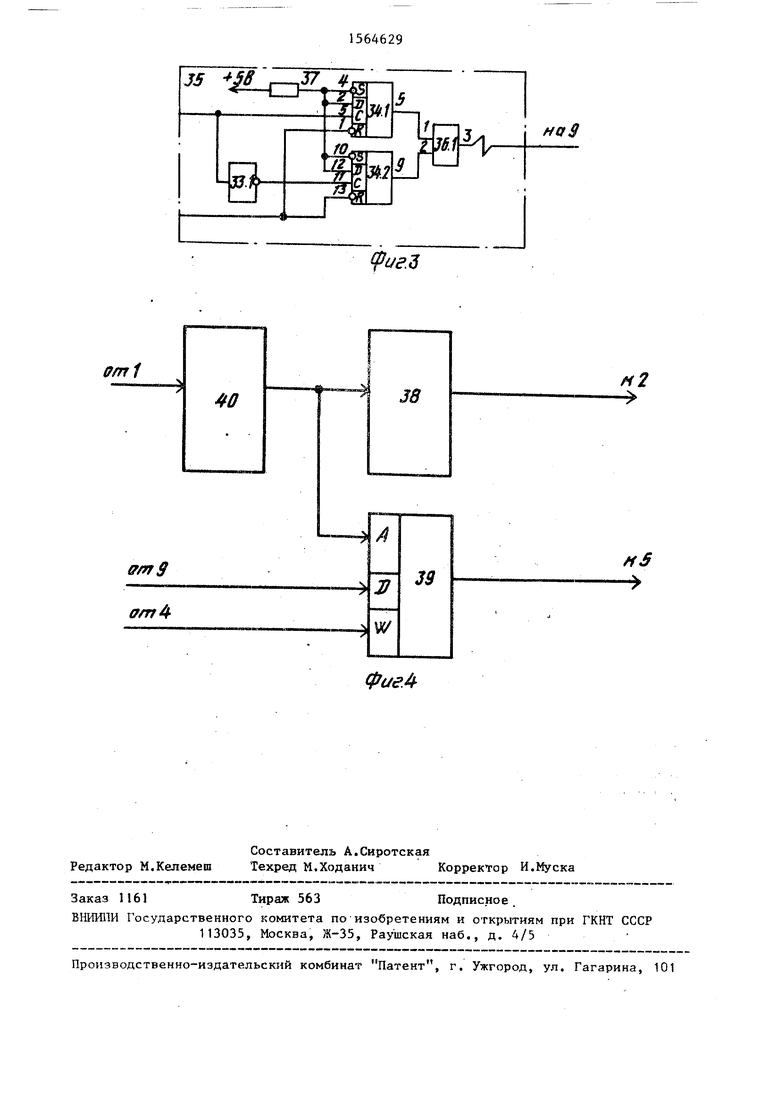

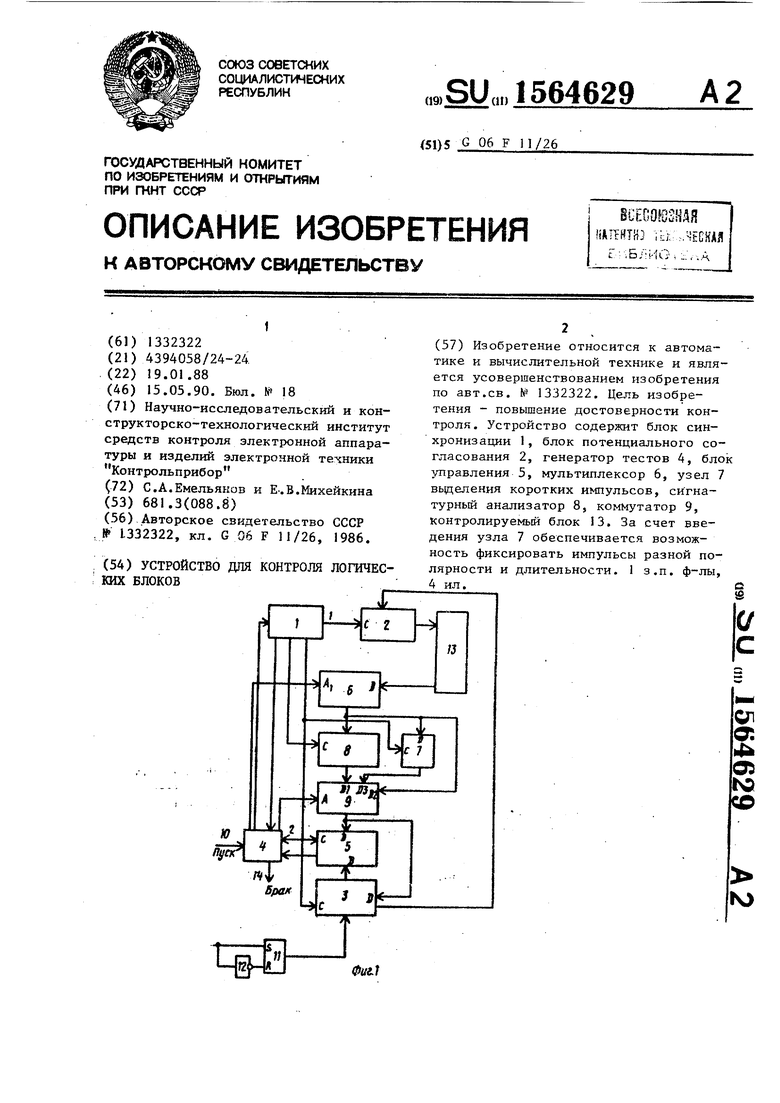

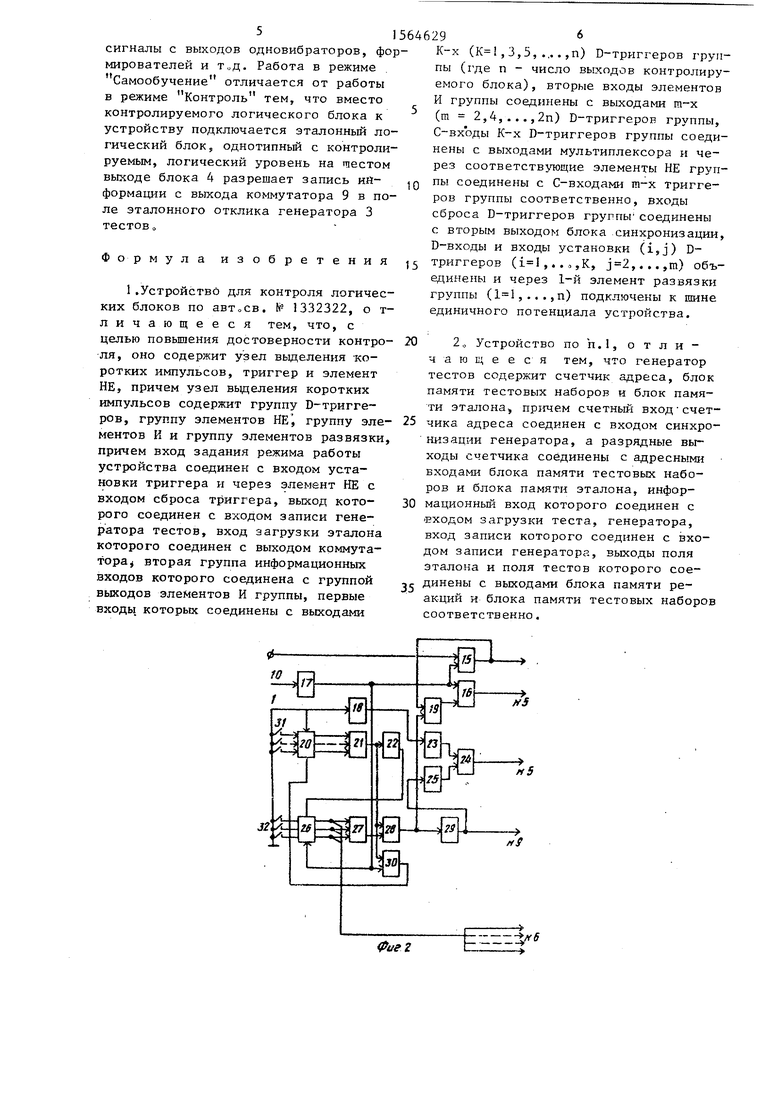

На фиг.1 схематически показано устройство для контроля; на фиг.2 - схема блока управления; на фиг.З - схема блока регистрации коротких импульсов; на фиг.4 - схема генератора тестов.

Устройство (фиг„1) соцержит блок I синхронизации, блок 2 потенциального согласования, генератор 3 тес- fOB, блок 4 управления,, блок 5 сравнения, мультиплексор 65 узел 7 выдэ- ления коротких импульсов, сигнатур ный анализатор 8, коммутатор 9, вход 10 пуска, триггер 11, элемент НЕ 12, контролируемый блок 13, выход 14 брака.

Блок управления (фиг.2) содержит триггеры 15 и 16, формирователь 17 Импульса, элемент 18 задержки, элемент ИЛИ 19, счетчик 20, дешифратор 21 нуля, формирователи 22 и 23 им- Пульсов, элемент ИЛИ 24, формирователь 25 импульсов, счетчик, образованный счетчиком 26 и дешифратором 2 нуля, элемент И 28, элемент 29 задержки, элемент ИЛИ 30, также обозначены шины 31 и 32 задания началь- ных данных.

Узел выделения коротких импульсов Гфиг.З, для удобства показана часть, обслуживающая один выход) содержит группу элементов НЕ 33.1 - 33.п, гру пу D-триггеров 34.1 - 34.п (где п - число выходов контролируемого блока) шину 35 единичного потенциала, группу элементов И 36.1 - 36.п, группу элементов развязки 37.1 - 37.п, выполненных на резисторах.

Генератор тестов (фиг.4) содержит блок 38 памяти тестовых наборов 38, блок 39 памяти эталона, счетчик 40 адреса.

Устройство работает следующим образом,

Логический уровень на выходе триггера 11 определяет один из двух возможных режимов работы устройства г контроль или самообучение.

При работе в режиме Контроль по запускающему сигналу, поступающему на вход 10 пуска устройства, блок 4

5

0

5

д

0

5

45

50

55

управления разрешает работу блока 1 синхронизации.

Блок 1 синхронизации обеспечивает необходимую временную диаграмму контроля, формируя сигналы управления работой блока 2 потенциального согласования, сигнатурного анализатора 8, узла 7„ генератора 3 тестов и блока 4 управления.

Синхросигнал с выхода блока 1 синхронизации разрешает выбор из генератора 3 тестов очередного тестового набора (выход поля тестов) и эталонной реакции (выход поля эталонного отклика), которые поступают соответственно на входы контролируемого логического блока 13 (через блок 2 потенциального согласования) и на информационный вход блока 5 сравнения. Одновременно сбрасываются триггеры узла 7.

Реакции контролируемого логического блока 13 поступают на информационный вход мультиплексора 6, который в зависимости от комбинации сигналов на адресном входе, поступающей с выхода блока 4 управления, подключает очередной выход контролируемого логического блока 13 к информационным входам сигнатурного анализатора 8 и узла 7, работа которых стробируется синхроимпульсами, поступающими с выхода блока 1 синхронизации. Сигнал с выхода блока 4 управления, поступающий на синхровход коммутатора 9, подключает выход сигнатурного анализатора 8 или узел 7 к информационному входу блока 5 сравнения, на котором происходят сравнения реакции контролируемого логического блока 13 и эталонного отклика при поступлении синхросигнала с выхода блока 4 управления.

Мультиплексированный отклик контролируемого блока поступает на узел 7 выделения коротких импульсов„ По переднему фронту этого импульса срабатывает триггер 34 „ 1, а по заднему (через элемент НЕ 33 „ I) - триггер 34.2« На элемент И 36.1 поступят две единицы,и на выходе элемента К 36.1 появится единица, которая поступит на коммутатор 9 для дальнейшей обработки.

Сигналом от блока 1 синхронизации триггеры 34 переводятся в исходное состояние.

Таким образом, узел 7 позволяет фиксировать кратковременные сбои или

Фиг 2

фе/аЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1332322A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1354195A1 |

Изобретение относится к автоматике и вычислительной технике и является усовершенствованием изобретения по а.с.N1332322. Цель изобретения - повышение достоверности контроля. Устройство содержит блок синхронизации 1, блок потенциального согласования 2, генератор тестов 4, блок управления 5, мультиплексор 6, узел 7 выделения коротких импульсов, сигнатурный анализатор 8, коммутатор 9, контролируемый блок 13. За счет введения узла 7 обеспечивается возможность фиксировать импульсы разной полярности и длительности. 1 з.п.ф-лы, 4 ил.

фиеА

| Устройство для контроля логических блоков | 1986 |

|

SU1332322A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-15—Публикация

1988-01-19—Подача