е

ой

ре

ной

ре

ной

ре

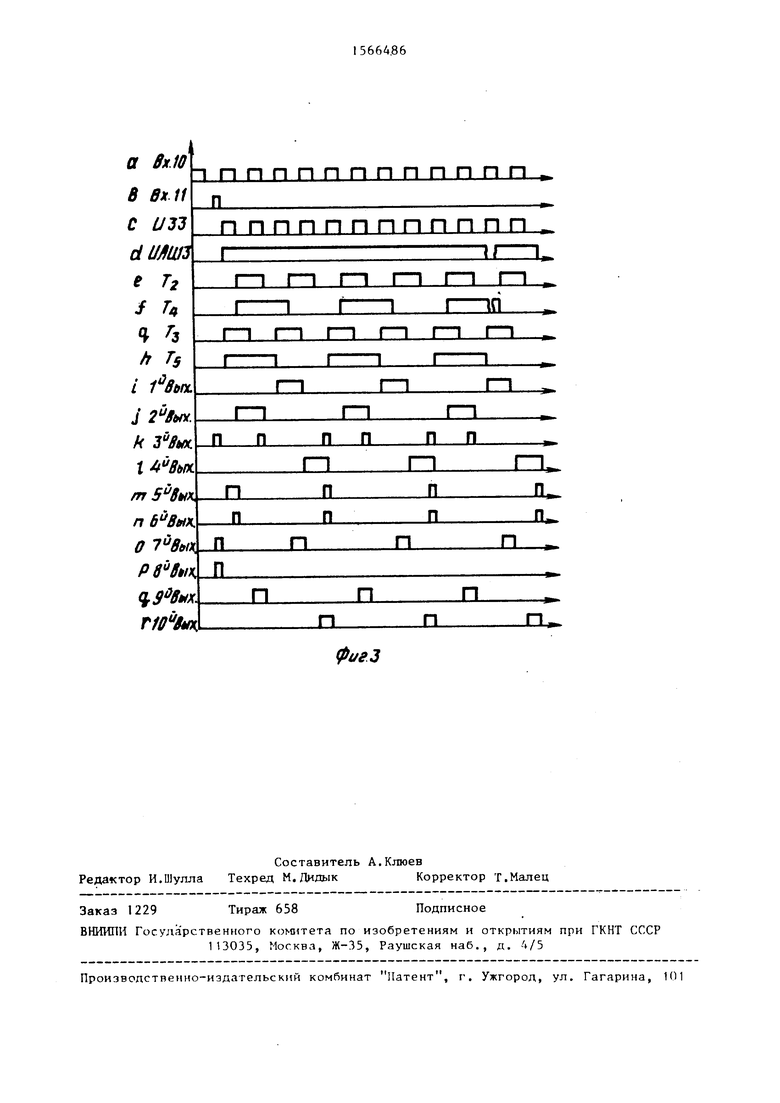

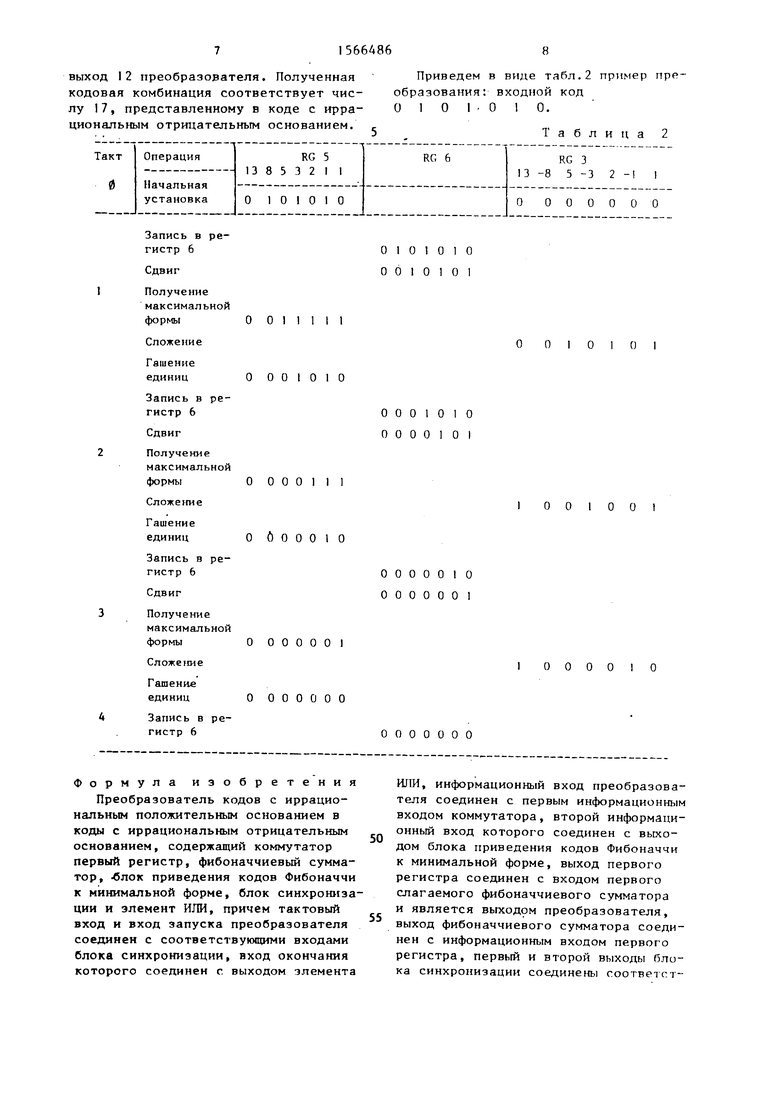

0011

О 001010

О 000111

О 600010

О 000001

О 000000

0101010 0010101

О 01010

0001010 0000101

001001

0000010 000000 1

000010

0000000

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов с иррациональным основанием | 1991 |

|

SU1837279A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Преобразователь числа в модулярный код | 1987 |

|

SU1444961A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Сумматор кодов с иррациональным основанием | 1982 |

|

SU1083182A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1983 |

|

SU1170449A1 |

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для умножения | 1987 |

|

SU1444751A1 |

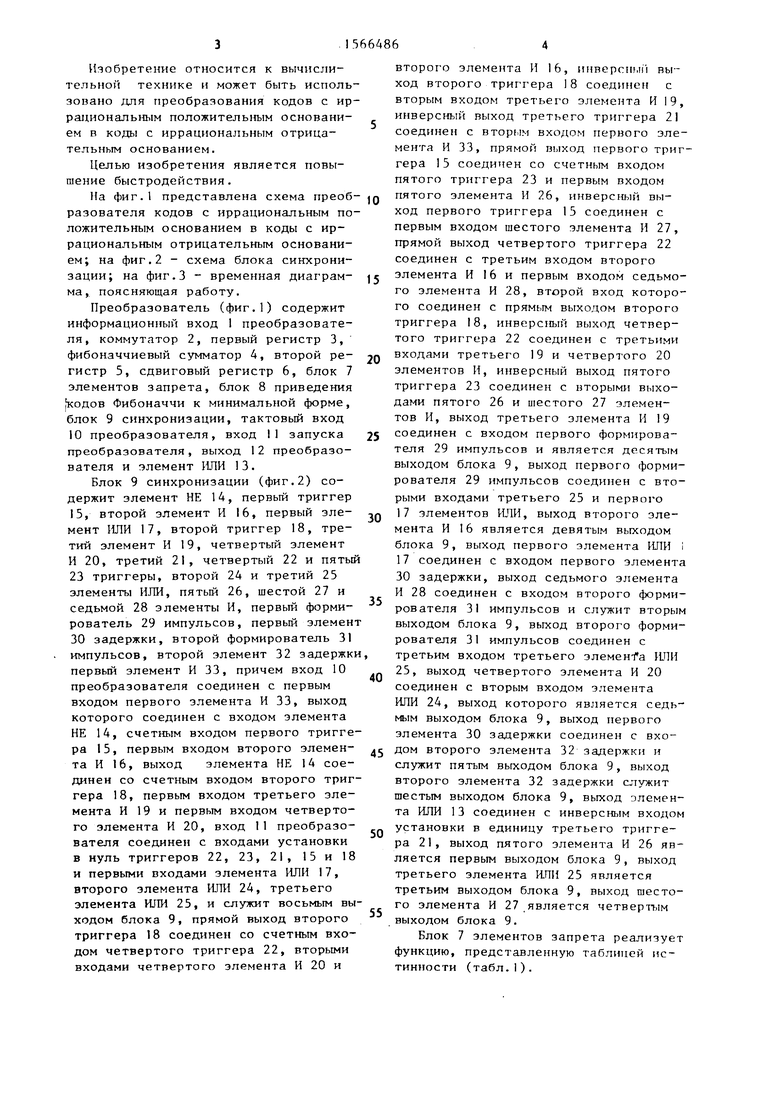

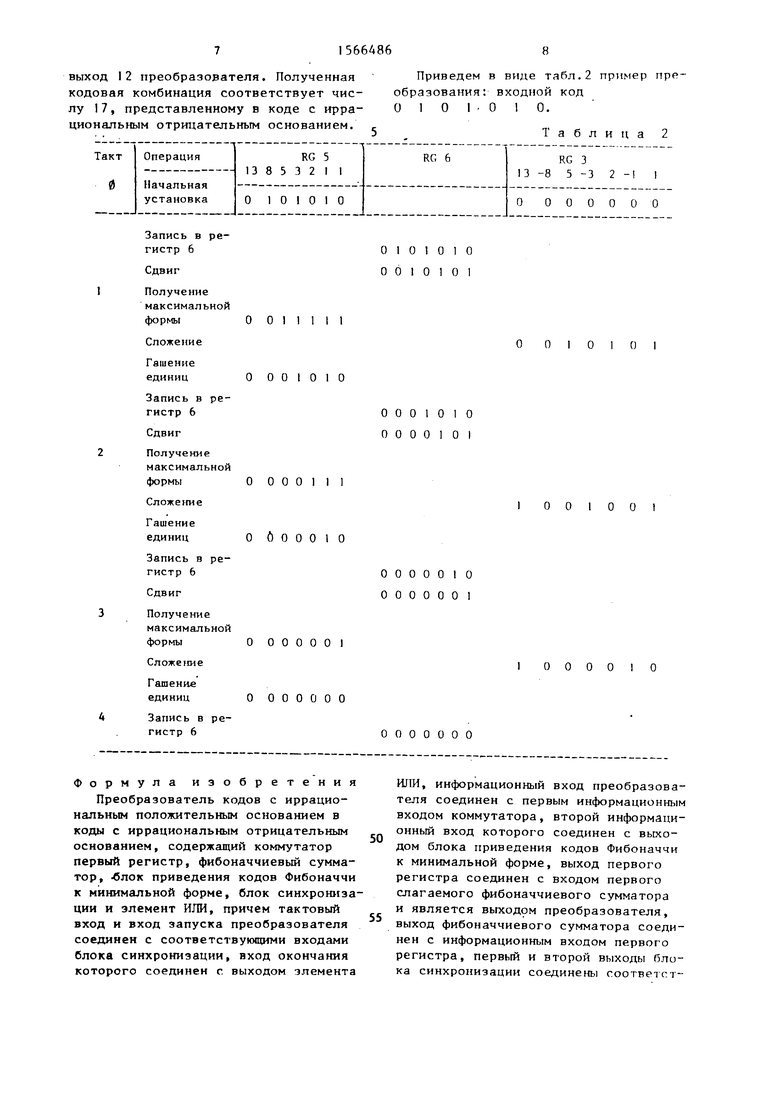

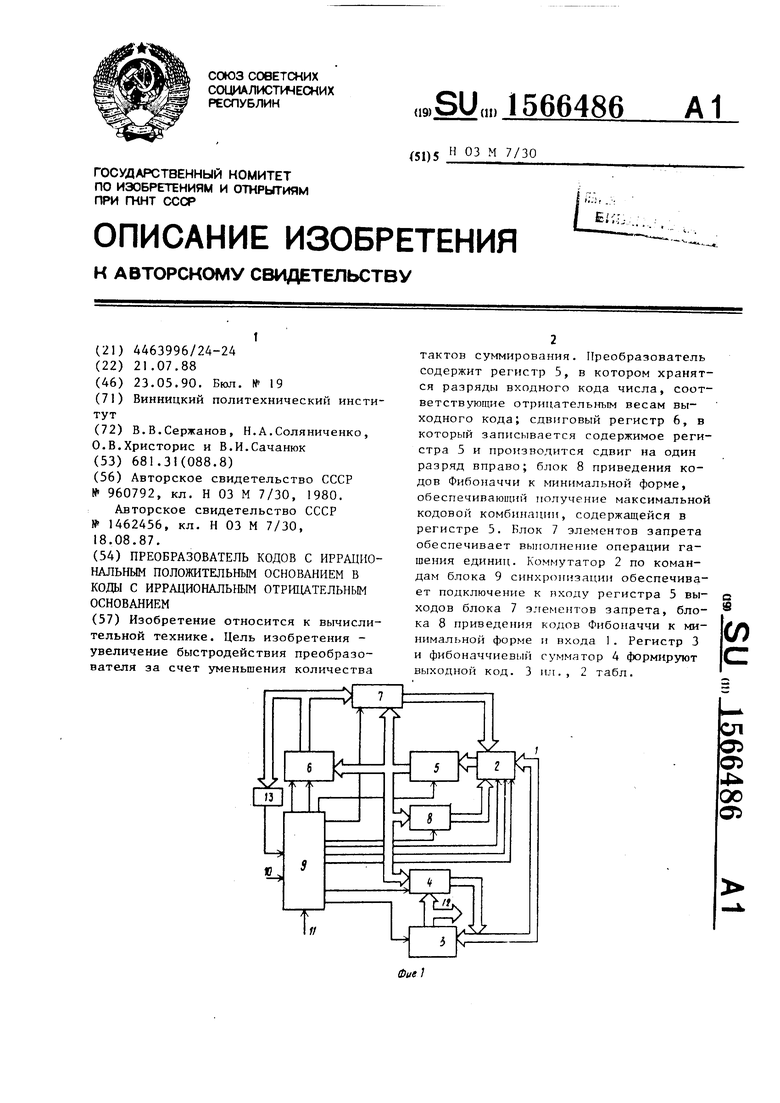

Изобретение относится к вычислительной технике. Цель изобретения - увеличение быстродействия преобразователя за счет уменьшения количества тактов суммирования. Преобразователь содержит регистр 5, в котором хранятся разряды входного кода числа, соответствующие отрицательным весам выходного кода

сдвиговый регистр 6, в который записывается содержимое регистра 5 и производится сдвиг на один разряд вправо

блок 8 приведения кодов Фибоначчи к минимальной форме, обеспечивающий получение максимальной формы кодовой комбинации, содержащейся в регистре 5. Блок 7 элементов запрета обеспечивает выполнение операции гашения единиц. Коммутатор 2 по командам блока 9 синхронизации обеспечивает подключение к входу регистра 5 выходов блока 7 элементов запрета, блока 8 приведения кодов Фибоначчи к минимальной форме и входа 1. Регистр 3 и фибоначчиевый сумматор 4 формируют выходной код. 3 ил., 2 табл.

Формула изобретения

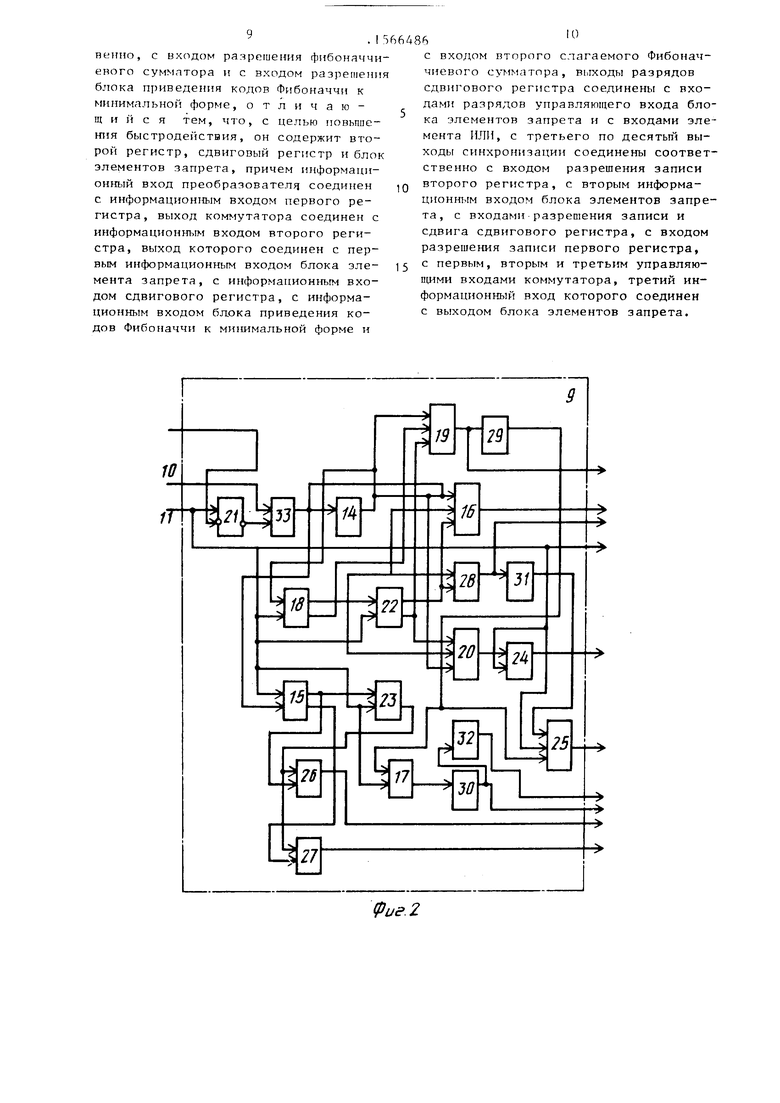

Преобразователь кодов с иррациональным положительным основанием в коды с иррациональным отрицательным основанием, содержащий коммутатор первый регистр, фибоначчиевый сумматор, -блок приведения кодов Фибоначчи к минимальной форме, блок синхронизации и элемент ИЛИ, причем тактовый вход и вход запуска преобразователя соединен с соответствующими входами блока синхронизации, вход окончания которого соединен с выходом элемента

0

5

ИЛИ, информационный вход преобразователя соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом блока приведения кодов Фибоначчи к минимальной форме, выход первого регистра соединен с входом первого слагаемого фибоначчиевого сумматора и является выходом преобразователя, выход фибоначчиевого сумматора соединен с информационным входом первого регистра, первый и второй выходы блока синхронизации соединены соответственно, с входом разрешения фибоначчи- евого сумматора и с входом разрешения блока приведения кодов Фибоначчи к минимальной форме, отличаю- Щ и и с я тем, что, с целью повышения быстродействия, он содержит второй регистр, сдвиговый регистр и блок элементов запрета, причем информационный вход преобразователя соединен с информационным входом первого регистра, выход коммутатора соединен с информационным входом второго регистра, выход которого соединен с первым информационным входом блока элемента запрета, с информационным входом сдвигового регистра, с информационным входом блока приведения кодов Фибоначчи к минимальной форме и

6648

10

с входом второго слагаемого Фибонач- чиевого сумматора, выходы разрядов сдвигового регистра соединены с входами разрядов управляющего входа блока элементов запрета и с входами элемента ИЛИ, с третьего по десятый выходы синхронизации соединены соответственно с входом разрешения записи

jg второго регистра, с вторым информационным входом блока элементов запрета, с входами разрешения записи и сдвига сдвигового регистра, с входом разрешения записи первого регистра,

15 с первым, вторым и третьим управляющими входами коммутатора, третий информационный вход которого соединен с выходом блока элементов запрета.

Фиг. 2

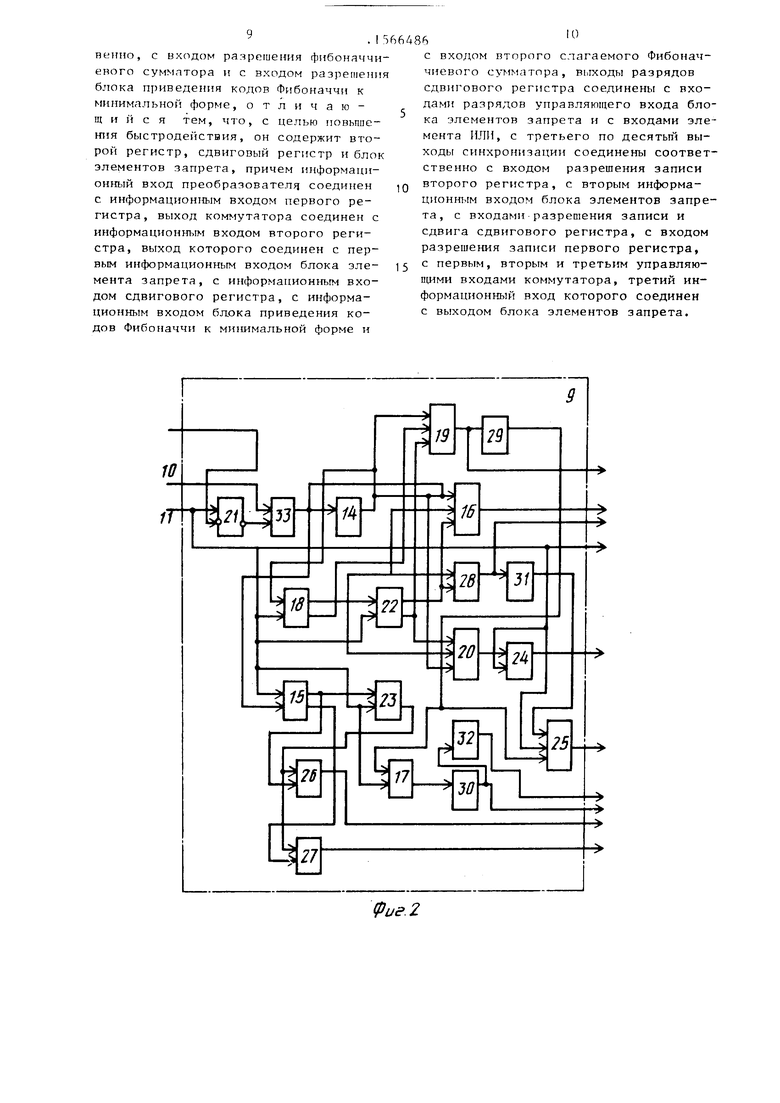

фиеЗ

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Автономный инвертор тока | 1987 |

|

SU1462456A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-21—Подача