(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для сопряжения источника и приемника информации | 1990 |

|

SU1718224A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1989 |

|

SU1686453A1 |

| Устройство для буферизации информации | 1988 |

|

SU1559350A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Устройство для контроля блоков буферной памяти | 1987 |

|

SU1501175A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании систем сбора и обработки информации. Цель изобретения - повышение достоверности работы устройства за счет обеспечения аппаратной отбраковки сбойных блоков данных при работе с блоками переменной длины. Сбои возникают из- за действия помех в канале связи. Цель достигается введением в устройство, содержащее блок памяти, счетчик, триггер, дешифратор, два элемента ИЛИ, два элемента задержки, мультиплексор и одновибратор. схемы сравнения, регистра, дополнительных триггера и дешифратора, двух элементов И 3 ил

Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения источника и приемника информации, и может быть использовано в качестве устройства буферной памяти в системах сбора и обработки информации.

Цель изобретения - повышение достоверности работы устройства.

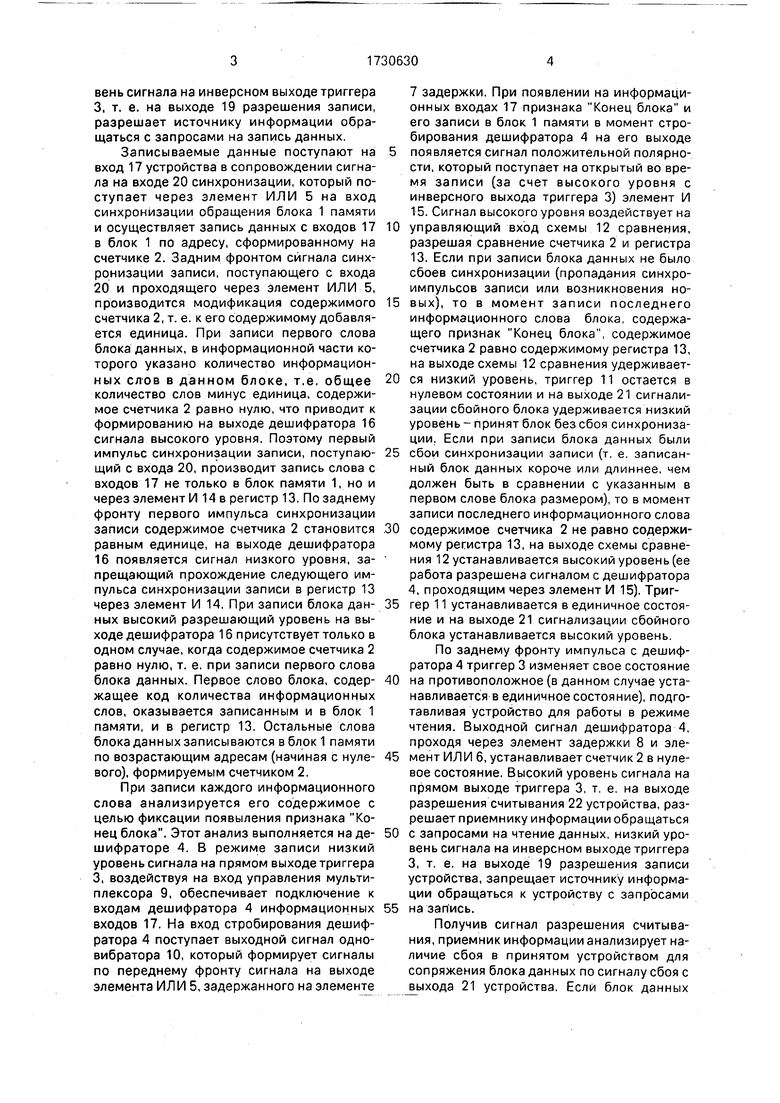

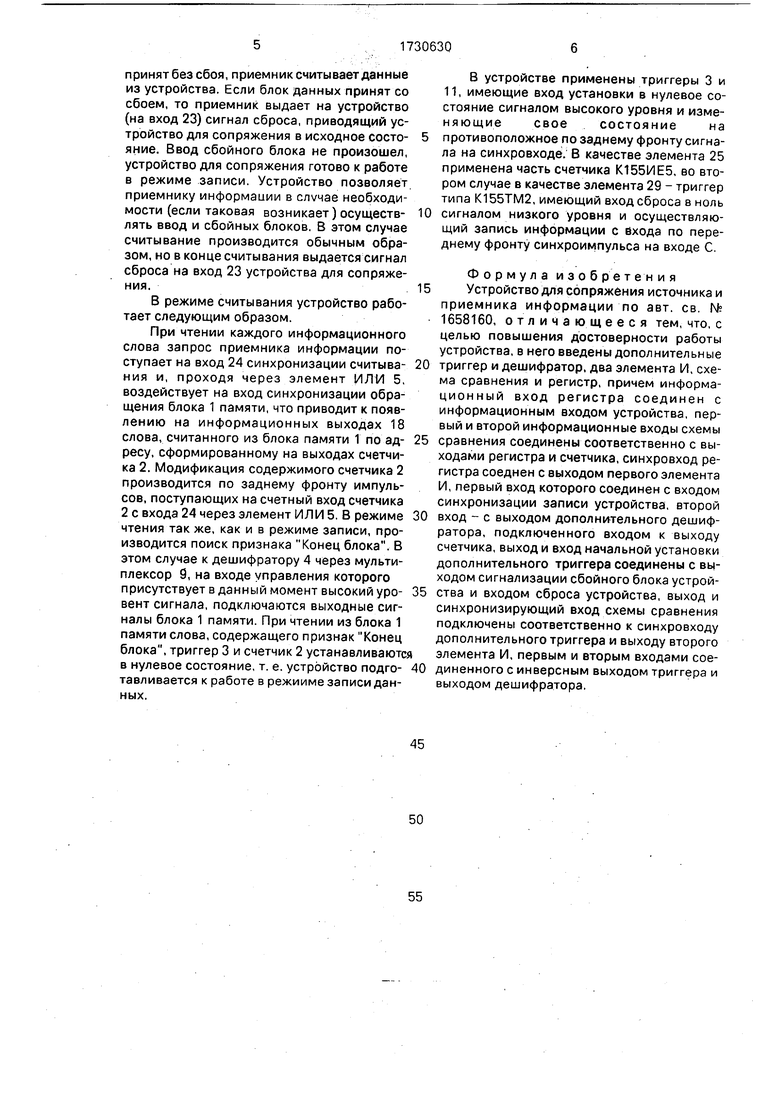

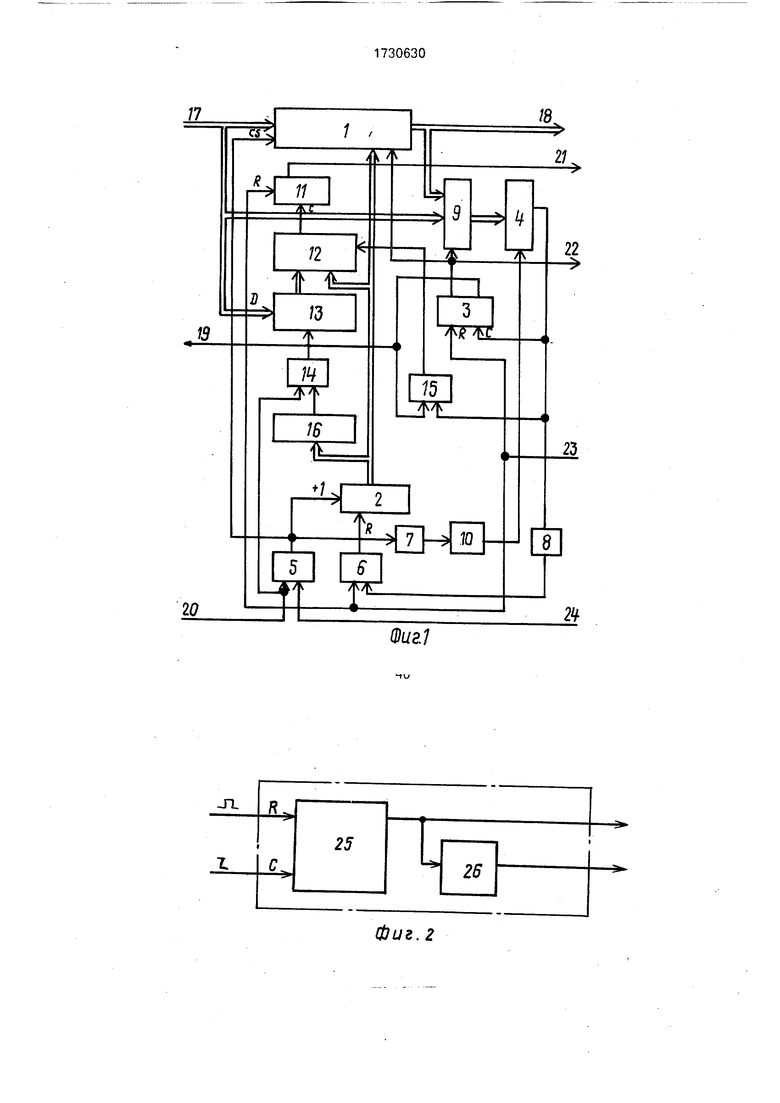

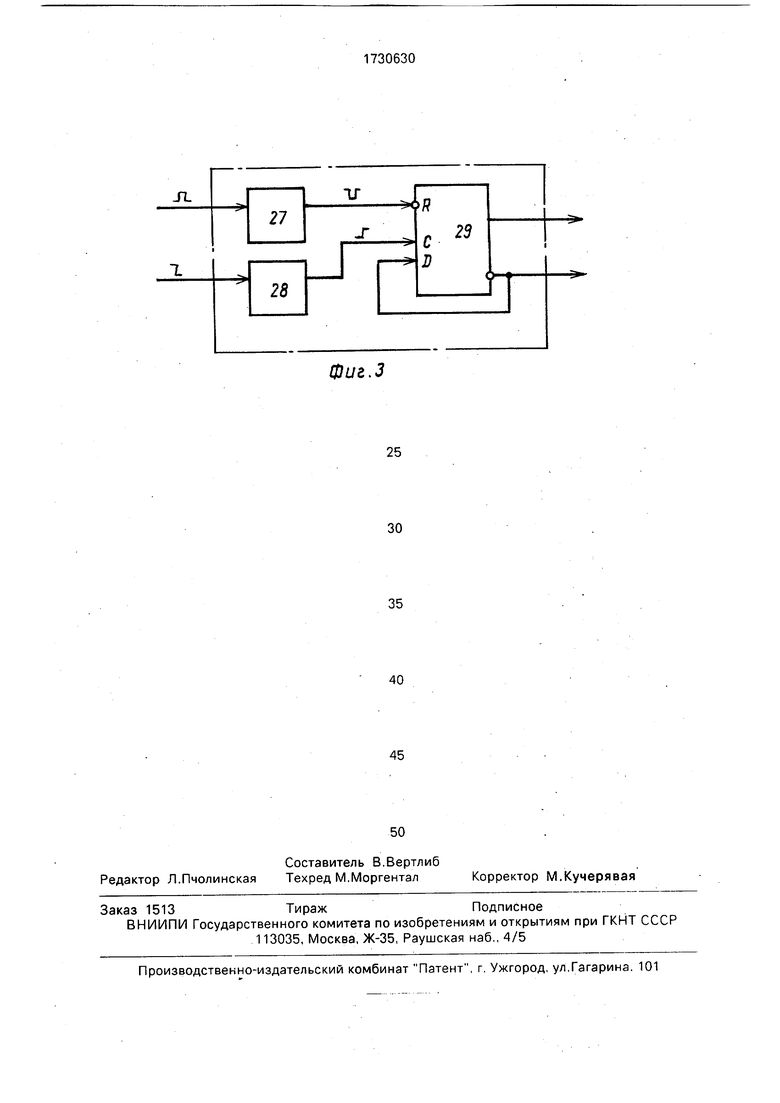

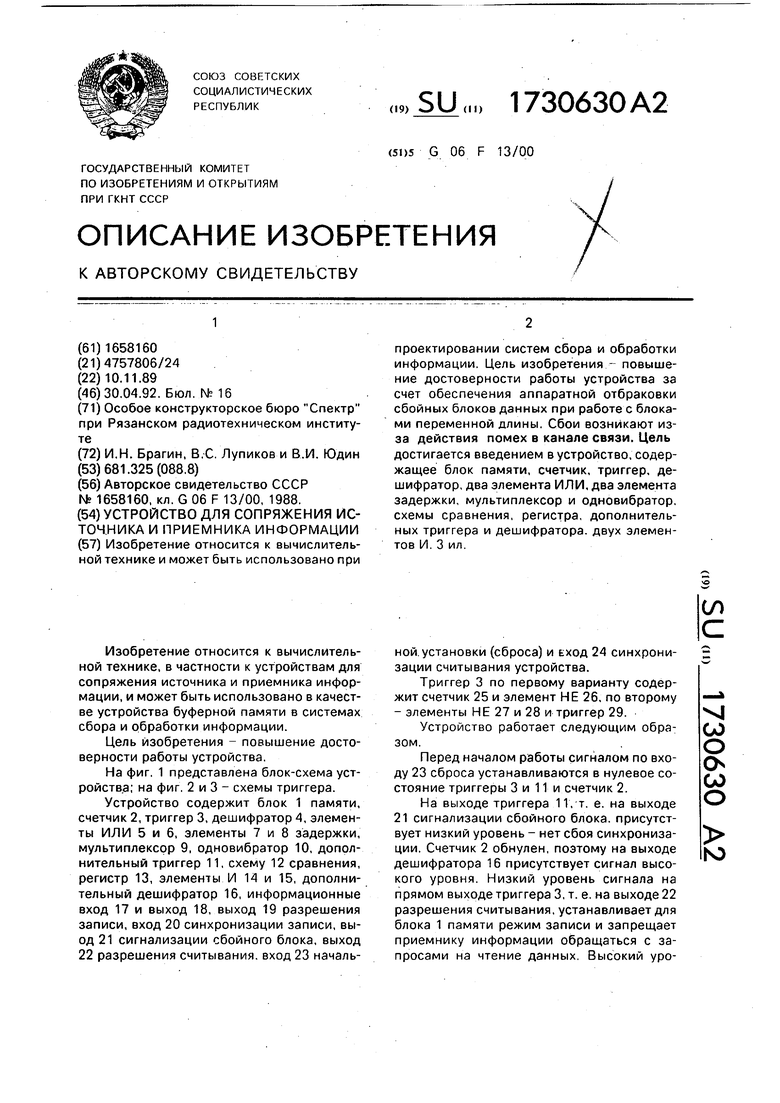

На фиг. 1 представлена блок-схема устройства; на фиг. 2 и 3 - схемы триггера.

Устройство содержит блок 1 памяти, счетчик 2, триггер 3, дешифратор 4, элементы ИЛИ 5 и 6, элементы 7 и 8 задержки, мультиплексор 9, одновибратор 10, дополнительный триггер 11,схему 12 сравнения, регистр 13, элементы И 14 и 15, дополнительный дешифратор 16, информационные вход 17 и выход 18, выход 19 разрешения записи, вход 20 синхронизации записи, вы- од 21 сигнализации сбойного блока, выход 22 разрешения считывания, вход 23 начальной установки (сброса) и ьход 24 синхронизации считывания устройства.

Триггер 3 по первому варианту содержит счетчик 25 и элемент НЕ 26, по второму - элементы НЕ 27 и 28 и триггер 29.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 23 сброса устанавливаются в нулевое состояние триггеры 3 и 11 и счетчик 2.

На выходе триггера 11, т. е. на выходе 21 сигнализации сбойного блока, присутствует низкий уровень - нет сбоя синхронизации. Счетчик 2 обнулен, поэтому на выходе дешифратора 16 присутствует сигнал высокого уровня. Низкий уровень сигнала на прямом выходе триггера 3, т. е. на выходе 22 разрешения считывания, устанавливает для блока 1 памяти режим записи и запрещает приемнику информации обращаться с запросами на чтение данных Высокий уроVICJ О ON СО О

ю

вень сигнала на инверсном выходе триггера 3, т. е. на выходе 19 разрешения записи, разрешает источнику информации обращаться с запросами на запись данных.

Записываемые данные поступают на вход 17 устройства в сопровождении сигнала на входе 20 синхронизации, который поступает через элемент ИЛИ 5 на вход синхронизации обращения блока 1 памяти и осуществляет запись данных с входов 17 в блок 1 по адресу, сформированному на счетчике 2. Задним фронтом сигнала синхронизации записи, поступающего с входа 20 и проходящего через элемент ИЛИ 5, производится модификация содержимого счетчика 2, т. е. к его содержимому добавляется единица. При записи первого слова блока данных, в информационной части которого указано количество информационных слов в данном блоке, т.е. общее количество слов минус единица, содержимое счетчика 2 равно нулю, что приводит к формированию на выходе дешифратора 16 сигнала высокого уровня. Поэтому первый импульс синхронизации записи, поступающий с входа 20, производит запись слова с входов 17 не только в блок памяти 1, но и через элемент И 14 в регистр 13. По заднему фронту первого импульса синхронизации записи содержимое счетчика 2 становится равным единице, на выходе дешифратора 16 появляется сигнал низкого уровня, запрещающий прохождение следующего импульса синхронизации записи в регистр 13 через элемент И 14. При записи блока данных высокий разрешающий уровень на выходе дешифратора 16 присутствует только в одном случае, когда содержимое счетчика 2 равно нулю, т. е. при записи первого слова блока данных. Первое слово блока, содержащее код количества информационных слов, оказывается записанным и в блок 1 памяти, и в регистр 13. Остальные слова блока данных записываются в блок 1 памяти по возрастающим адресам (начиная с нулевого), формируемым счетчиком 2.

При записи каждого информационного слова анализируется его содержимое с целью фиксации появыления признака Конец блока. Этот анализ выполняется на дешифраторе 4. В режиме записи низкий уровень сигнала на прямом выходе триггера 3, воздействуя на вход управления мультиплексора 9, обеспечивает подключение к входам дешифратора 4 информационных входов 17. На вход стробирования дешифратора 4 поступает выходной сигнал одно- вибратора 10, который формирует сигналы по переднему фронту сигнала на выходе элемента ИЛИ 5, задержанного на элементе

7 задержки. При появлении на информационных входах 17 признака Конец блока и его записи в блок 1 памяти в момент стробирования дешифратора 4 на его выходе

появляется сигнал положительной полярности, который поступает на открытый во время записи (за счет высокого уровня с инверсного выхода триггера 3) элемент И 15. Сигнал высокого уровня воздействует на

0 управляющий вход схемы 12 сравнения, разрешая сравнение счетчика 2 и регистра 13. Если при записи блока данных не было сбоев синхронизации (пропадания синхроимпульсов записи или возникновения но5 вых), то в момент записи последнего информационного слова блока, содержащего признак Конец блока, содержимое счетчика 2 равно содержимому регистра 13, на выходе схемы 12 сравнения удерживает0 ся низкий уровень, триггер 11 остается в нулевом состоянии и на выходе 21 сигнализации сбойного блока удерживается низкий уровень - принят блок без сбоя синхронизации. Если при записи блока данных были

5 сбои синхронизации записи (т. е. записанный блок данных короче или длиннее, чем должен быть в сравнении с указанным в первом слове блока размером), то в момент записи последнего информационного слова

0 содержимое счетчика 2 не равно содержимому регистра 13, на выходе схемы сравнения 12 устанавливается высокий уровень (ее работа разрешена сигналом с дешифратора 4, проходящим через элемент И 15). Триг5 гер 11 устанавливается в единичное состояние и на выходе 21 сигнализации сбойного блока устанавливается высокий уровень.

По заднему фронту импульса с дешифратора 4 триггер 3 изменяет свое состояние

0 на противоположное (в данном случае устанавливается в единичное состояние), подготавливая устройство для работы в режиме чтения. Выходной сигнал дешифратора 4, проходя через элемент задержки 8 и эле5 мент ИЛИ 6, устанавливает счетчик 2 в нулевое состояние. Высокий уровень сигнала на прямом выходе триггера 3, т. е. на выходе разрешения считывания 22 устройства, разрешает приемнику информации обращаться

0 с запросами на чтение данных, низкий уровень сигнала на инверсном выходе триггера 3, т. е. на выходе 19 разрешения записи устройства, запрещает источнику информации обращаться к устройству с запросами

5 на запись.

Получив сигнал разрешения считывания, приемник информации анализирует наличие сбоя в принятом устройством для сопряжения блока данных по сигналу сбоя с выхода 21 устройства. Если блок данных

принят без сбоя, приемник считывает данные из устройства. Если блок данных принят со сбоем, то приемник выдает на устройство (на вход 23) сигнал сброса, приводящий устройство для сопряжения в исходное состо- яние. Ввод сбойного блока не произошел, устройство для сопряжения готово к работе в режиме записи. Устройство позволяет приемнику информации в случае необходимости (если таковая возникает) осуществ- лять ввод и сбойных блоков. В этом случае считывание производится обычным образом, но в конце считывания выдается сигнал сброса на вход 23 устройства для сопряжения.

В режиме считывания устройство работает следующим образом.

При чтении каждого информационного слова запрос приемника информации поступает на вход 24 синхронизации считыва- ния и, проходя через элемент ИЛИ 5, воздействует на вход синхронизации обращения блока 1 памяти, что приводит к появлению на информационных выходах 18 слова, считанного из блока памяти 1 по ад- ресу, сформированному на выходах счетчика 2. Модификация содержимого счетчика 2 производится по заднему фронту импульсов, поступающих на счетный вход счетчика 2 с входа 24 через элемент ИЛИ 5. В режиме чтения так же, как и в режиме записи, производится поиск признака Конец блока. В этом случае к дешифратору 4 через мультиплексор 9, на входе управления которого присутствует в данный момент высокий уро- вент сигнала, подключаются выходные сигналы блока 1 памяти. При чтении из блока 1 памяти слова, содержащего признак Конец блока, триггер 3 и счетчик 2 устанавливаютс в нулевое состояние, т. е. устройство подго- тавливается к работе в режииме записи данных.

В устройстве применены триггеры 3 и 11, имеющие вход установки в нулевое состояние сигналом высокого уровня и изме- няющие свое состояние на противоположное по заднему фронту сигнала на синхровходе. В качестве элемента 25 применена часть счетчика К155ИЕ5, во втором случае в качестве элемента 29 - триггер типа К155ТМ2, имеющий вход сброса в ноль сигналом низкого уровня и осуществляющий запись информации с входа по переднему фронту синхроимпульса на входе С.

Формула изобретения Устройство для сопряжения источника и приемника информации по авт. св. № 1658160, отличающееся тем, что, с целью повышения достоверности работы устройства, в него введены дополнительные триггер и дешифратор, два элемента И, схема сравнения и регистр, причем информационный вход регистра соединен с информационным входом устройства, первый и второй информационные входы схемы сравнения соединены соответственно с выходами регистра и счетчика, синхровход регистра соеднен с выходом первого элемента И, первый вход которого соединен с входом синхронизации записи устройства, второй вход - с выходом дополнительного дешифратора, подключенного входом к выходу счетчика, выходи вход начальной установки дополнительного триггера соединены с выходом сигнализации сбойного блока устройства и входом сброса устройства, выход и синхронизирующий вход схемы сравнения подключены соответственно к синхровходу дополнительного триггера и выходу второго элемента И, первым и вторым входами соединенного с инверсным выходом триггера и выходом дешифратора.

Фиг.2

Л.

27

Фиг.З

If

23

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1658160A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1989-11-10—Подача