сд J

00

00

сд

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

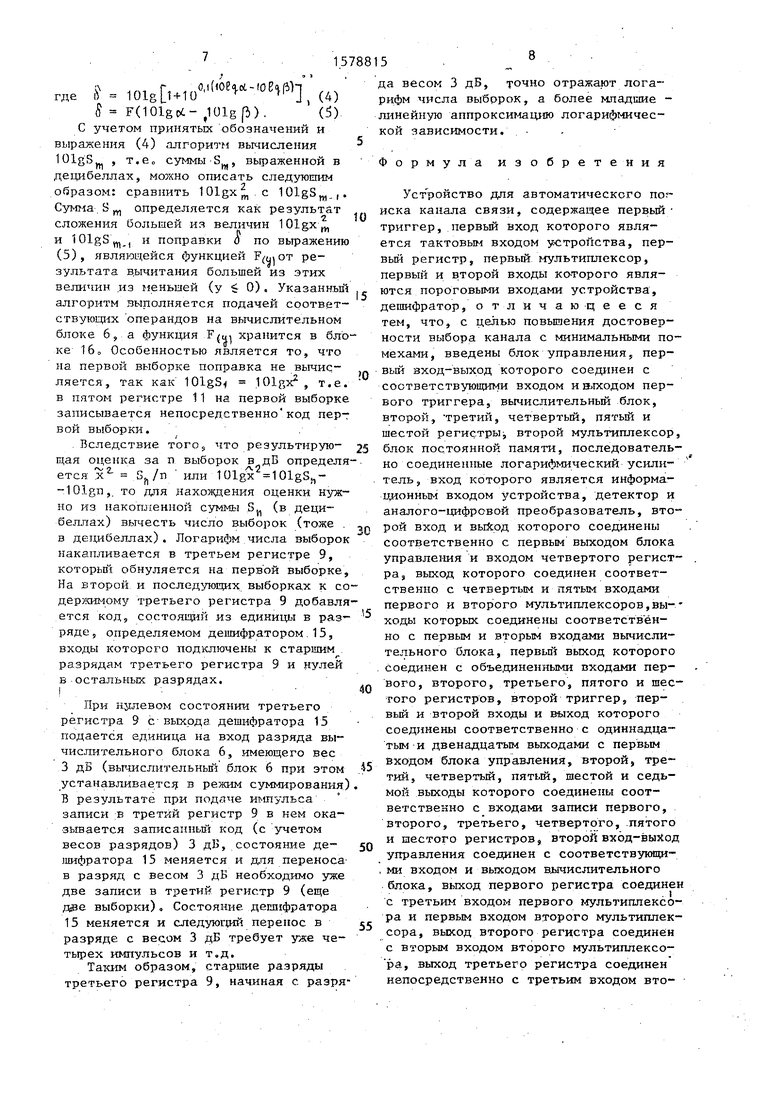

Изобретение относится к технике электросвязи. Цель изобретения - повышение достоверности выбора канала с минимальными помехами. Устройство содержит логарифмический усилитель 1, детектор 2, аналого-цифровой преобразователь 3, блок 4 управления, триггер 5, вычислительный блок 6, шесть регистров 7 - 12, два мультиплексора 13, 14, дешифратор 15, блок 16 памяти, триггер 17. Устройство подключается к выходу промежуточной частоты приемника. Блок 4 управления формирует все необходимые управляющие сигналы. В вычислительном блоке 6 выполняются операции по определению поправки. При этом старшие разряды регистра 9, начиная с разряда весом 3 дБ, точно отражают алгоритм числа выборок, а более младшие - линейную аппроксимацию логарифмической зависимости. 2 ил.

Фиг 1

готоВнос/тш резурьмота

Изобретение относится к технике электросвязи и может использоваться для автоматического поиска каналов радиосвязи.

Цель изобретения - повышение достоверности выбора канала с минимальными помехами

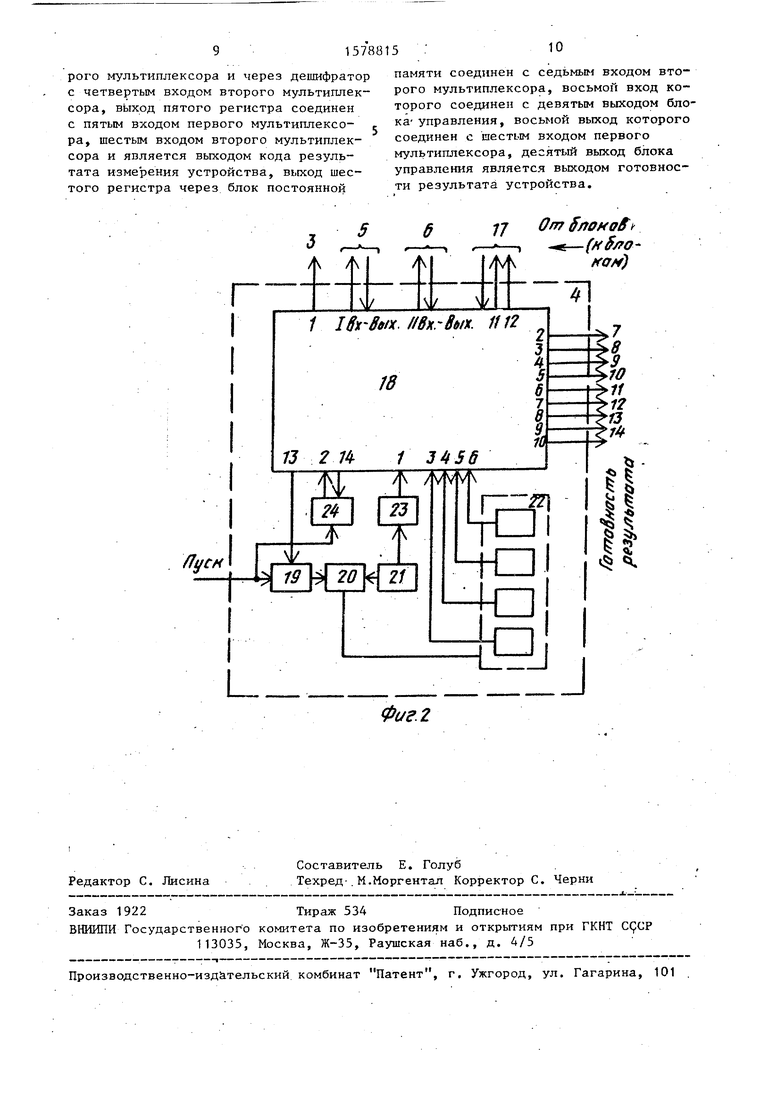

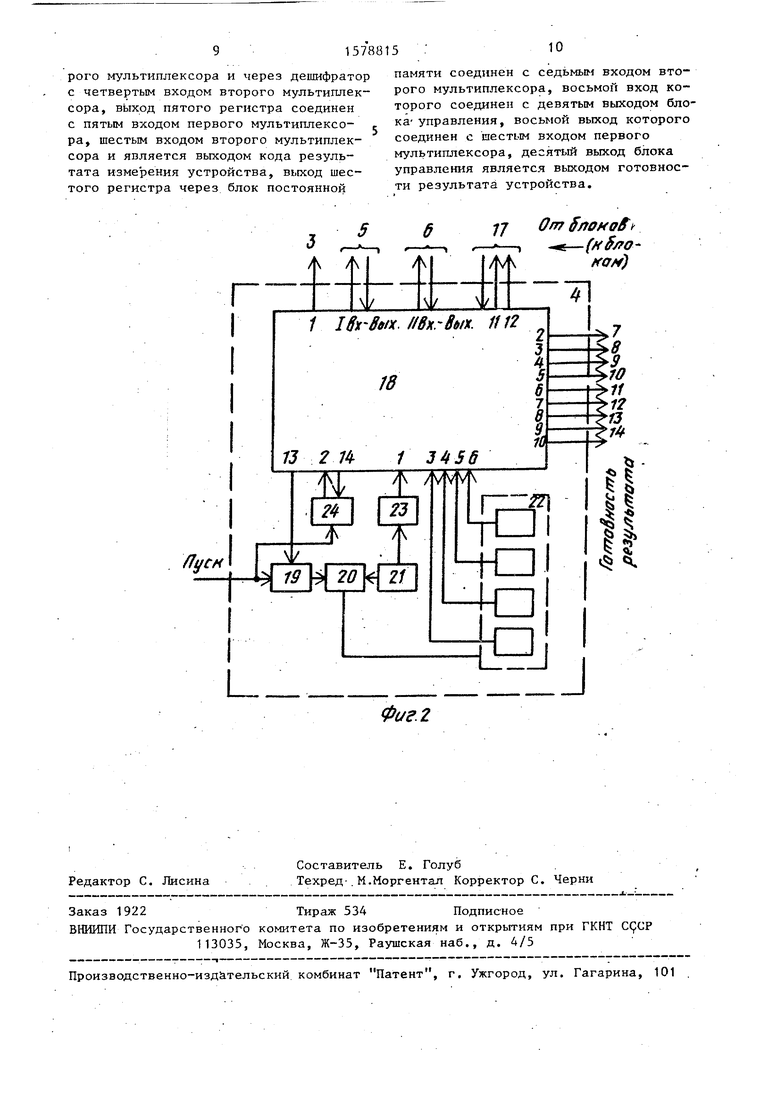

На фиго 1 представлена структурная электрическая схема предлагаемого уст ройства; на фиг. 2 - вариант выполнения блока управления о

Устройство для автоматического поиска канала связи содержит логарифмический усилитель 1, детектор 2, аналого-цифровой преобразователь (АЦП) 3, блок 4 управления, первый триггер 5, вычислительный блок 6, первый, второй третий, четвертый, пятый и шестой регистры 7-12 первый и второй мульти- плексоры 13 и 14, дешифратор 15, блок

16постоянной памяти, второй триггер.

17о Блок 4 управления содержит ( программируемую логическую матрицу 18 первый триггер 19, элемент И 20, ге- нератор 21 тактовых импульсов, счетчи 22, формирователь 23 импульсов, второй триггер 24.

Устройство работает следующим образом.

Предлагаемое устройство в основном использовании подключается к выходу промежуточной частоты (ПЧ) приемника (не показан). Перед пуском устройства (перед подачей соответствую- щего импульса на вход блока 4 управления) на входных минах выставляются следующие данные: на входе первого триггера 5 - команда наличия адаптации, на первом входе первого мультиплексора 13 - код порогового времени

Такт

Выполняемые по тактам операции

на первой выборке

13 а п у с к А

2Запись входного кода времени измерения во второй регистр 8

3Запись в первый триггер 5 1. при внешней команде наличия адаптации и О в противоположном случае

4Запись кода порога адаптации в первый регистр 7 при условии установки третьего триггера 5 в 1

Сложение кодов, записанных в первом и втором регистрах 7 и 8, и запись результатов во второй регистр 8

15

jg 20

25

8815ч

анализа, на втором входе первого мультиплексора 13- код порога адаптации (при наличии команды адаптации), при- е чем оба кода вводятся в логарифмическом масштабе (фиг„ 1).

При подаче внешнего импульса Пуск первый и второй триггеры 19 и 24 блока 4 управления (фиг.2) устанавливаются в исходное положение, при этом первый триггер 19 подает разрешение на элемент И 20 и тактовые импульсы с генератора 21 начинают заполнять счетчик 22. Коэффициент пересчета счетчика 22 определяет необходимое число тактов (в данном случае одиннадцать) н-а одну выборку процес- са - один цикл работы аналого-цифрового преобразователя (АЦП) 3. Одноврет менно сигнал с выхода ПЧ приемника проходит черео логарифмический усилитель 1 и детектор 2, после которого выделяется огибающая логарифма помехи (сигнала). АЦП 3 по командам блока 4 кодирует отдельные выборки этой огибающей, код которых также по командам от блока 4 записывается в четвертый регистр 10. Формирователь 23 импульсов формирует стробы, разнесенные по времени от счетных фронтов сметчика 22. Программируемая логическая матрица 18 формирует набор управляющих сигналов, логически связанных с состояниями триггеров 5, 17 и 24, счетчика

22и наличием строба от формирователя

23импульсов.

Набор управляющих сигналов от программируемой логической матрицы 18 обеспечивает тактированное выполнение дася 4Q первой и последукчщх выборок операций в соответствии с таблицей.

30

35

Т

на второй и последующих выборках

Ц П 3

Установка второго триггера 24 в положение 1 соответствует команде второй и последующих выборок Запись в третий триггер 9 суммы кодов этого регистра и выходного кода дешифратора 15

Сравнение кода четвертого регистра 10 с кодом пятого регистра 11 и запись 1 во второй триггер 17, если Запись О в противоположном случае

При состоянии второго триггера 17 1 вычитание из кода четвертого регистр 10 кода пятого регистра 11 и -запись

Запись нулевого кода в третий регистр 9 текущего времени анализа

10

11

Запись кода АЦП 3 в четвертый регистр 10

Запись кода четвертого регистра 10 через первый мультиплексор 13 и вычислительный блок 6 в пятый регистр 11

Сравнение кода третьего регистра 9 с кодом второго регистра 8 и аапись 1 во второй триггер4 17 и запись О в этот второй триггер 17 в противоположном случае

Сравнение кода пятого регистра 11 с кодом первого регистра 7 и при условиях установки первого триггера 5 1 и с, а- с эапись во второй триггер 17 1. Сохранение старого состояния второго триггера 17 в противоположном случае

При условии состояния второго триггера 17 1 вычитание из кода пятого регистра 11 кода третьего регистра 9 и запись результата в пятый регистр 11 и выдача готовности результата. Сброс первого триггера 19 по заднему фронту строба (для остановки измерителя)

Примечание, oi - код, записанный в регистр.

Выделение необходимых команд по Номеру такта для первой и для последующих выборок определяется состоянием счетчика 22 и второго триггера 24 блока 4.

На выходах программируемой логической матрицы 18 формируются в соответствии с таблицей команды коммутации первого и второго мультиплексоров 13 и 14 для подачи необходимых операндов на входы вычислительного блока 6. Программируемая логическая матрица 18 формирует коды операций управления вычислительным блоком 6 в соответст35

где п - число выборок;

х. - квадрат выборок (j - номер

и борки); Sn 2х; сумма для п выборок.

i i

Для текущего значения га указан сумма Sm определяется

.

3m-i

ш

m m-i -Гх - х.-.. .J J

Прологарифмируем выражение (1)

x2 10lgSrt lOlgS -HOLgO + Јs).

sm-l

Аналогично выражению (2) может вии с таблицей, кроме того, формирует ,,-

.. vu Mwyyei (5 быть получено выражение

стробы для запуска А1ЩЗ 3 для установки триггеров 5Э 19, 24 и всех регист- lOleS ров 7-12 в соответствии с таблицей.m

10lgx + 101g(1 -%Ј.

Вычисление среднеквадратичного значения реализации случайного процесса -п по дискретным выборкам осуществляется по формуле:

lix -JIT п fr S Ч n

этого значения

г

результата в шестой регистр 12. При состоянии второго триггера 17 О запись в шестой регистр 12 of,, Сложение кода пятого регистра 11 с кодом содержимого блока 16 по адресу, записанному в шестом регистре 12, и запись результата в пятый регистр 11

где п - число выборок;

х. - квадрат выборок (j - номер выи борки); Sn 2х; сумма для п выборок.

i i

Для текущего значения га указанная сумма Sm определяется

. (1)

3m-i

m m-i -Гх - х.-.. .J J

Прологарифмируем выражение (1)

x2 10lgSrt lOlgS -HOLgO + Јs).

sm-l

(2)

10lgx + 101g(1 -%Ј. (3)

Выражения (2) и (3) можно обобщить, введя обозначения:

m

(,

2- . fti Sm- 2 „ при ,.,; ,,,

5

10lBSM 10lgp+10lg(1 )

ioigf}-Hoig i + 10о,1(.ое3р)-| ioigp+ $ ,

j.

результат больпей ия величин 10lgx,

где ff- 10lg H100 l((4) 8 F(10lgpC- ,10lgp). (5) С учетом принятых обозначений и выражения (4) алгоритм вычисления lOigS , т.е„ суммы S, выраженной в децибеллах, можно описать следуюпим образом: сравнить lOlgx, с 10lgSw, Сумма S m определяется как сложения

л СП

и 101gSm, и поправки 6 по выражению (5), являющейся функцией результата вычитания большей из этих величин из менылей (у 0) , Указанный алгоритм выполняется подачей соответ- ствуюцих операндов на вычислительном блоке 6, а функция F хранится в блоке 16 Особенностью является то, что на первой выборке поправка не вычисляется, так как 10lgS lOlgx2, т.е. в пятом регистре 11 на первой выборке записывается непосредственно код первой выборки.

/

Вследствие того5 что реэультирую-

щая оценка за п выборок в дБ определяется х2- Sh /n или 10lgx 10lgSrt- 10lgn, то для нахождения оценки нужно из накопленной суммы SM (в децибеллах) вычесть число выборок (тоже в децибеллах). Логарифм числа выборок накапливается в третьем регистре 9, который обнуляется на первой выборке, На второй и последующих выборках к содержимому третьего регистра 9 добавляется код, состоящий из единицы в pas - ряде 5 определяемом дешифратором 15, входы которого подключены к старшим разрядам третьего регистра 9 и нулей

в остальных разрядах.

I

При кулевом состоянии третьего регистра 9 с выхода дешифратора 15 подается единица на вход разряда вычислительного блока 6, имеющего вес 3 дБ (вычислительный блок 6 при этом устанавливается в режим суммирования) В результате при подлче импульса записи в третий регистр 9 в кем оказывается записанный код (с учетом весов разрядов) 3 дБ, состояние дешифратора 15 меняется и для переноса в разряд с весом 3 дБ необходимо уже две записи в третий регистр 9 (еще дае выборки)„ Состояние дешифратора 15 меняется и следуюций перенос в разряде с весом 3 дБ требует уже четырех импульсов и т.д.

Таким образом, старшие разряды

третьего регистра 9, начиная с раэря

J

5

5

0

0

5

0

45

0

5

да весом 3 дБ, точно отражают логарифм числа выбррок, а более младшие - линейную аппроксимацию логарифмической зависимости.

Формула изобретения

Устройство для автоматического по иска канала связи, содержащее первый триггер, первьй вход которого является тактовым входом устройства, первьй регистр, первьй мультиплексор, первый и второй входы которого являются пороговыми входами устройства, дешифратор, отличающееся тем, что, с целью повышения достоверности выбора канала с минимальными помехами, введены блок управления, первый вход-выход которого соединен с соответствующими входом и выходом первого триггера, вычислительный блок, второй, третий, четвертый, пятый и шестой регистры, второй мультиплексор, блок постоянной памяти, последовательно соединенные логарифмический усилитель, вход которого является информационным входом устройства, детектор и аналого-цифровой преобразователь, второй вход и выход которого соединены соответственно с первым выходом блока управления и входом четвертого регистра, выход которого соединен соответственно с четвертым и пятым входами первого и второго мультиплексоров,вы-- ходы которых соединены соответственно с первым и вторым входами вычислительного блока, первый выход которого соединен с объединенными входами первого, второго, третьего, пятого и шестого регистров, второй триггер, первьй и второй входы и выход которого соединены соответственно с одиннадцатым и двенадцатым выходами с первым входом блока управления, второй, третий, четвертый, пятый, шестой и седьмой выходы которого соединены соответственно с входами записи первого, второго, третьего, четвертого, пятого и шестого регистров, второй вход-выход управления соединен с соответствующи- , ми входом и выходом вычислительного блока, выход первого регистра соединен с третьим входом первого мультиплексора и первым входом второго мультиплексора, выход второго регистра соединен с вторым входом второго мультиплексора, выход третьего регистра соединен непосредственно с третьим входом второго мультиплексора и через дешифратор с четвертым входом второго мультиплексора, выход пятого регистра соединен с пятым входом первого мультиплексо- , ра, шестым входом второго мультиплексора и является выходом кода результата измерения устройства, выход шестого регистра через блок постоянной

Г

/Гуси

l

памяти соединен с седьмым входом второго мультиплексора, восьмой вход которого соединен с девятым выходом блока- управления, восьмой выход которого соединен с шестым входом первого мультиплексора, десятый выход блока управления является выходом готовности результата устройства.

От $rto/«jf (xfao- ком)

Фиг. 2

| Авторское свидетельство СССР №4225048, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-07-15—Публикация

1989-01-02—Подача