Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и устройствах, работающих в избыточной двоичной системе счисления с цифрами 1, 0 и 1.

Цель изобретения - повышение быстродействия.

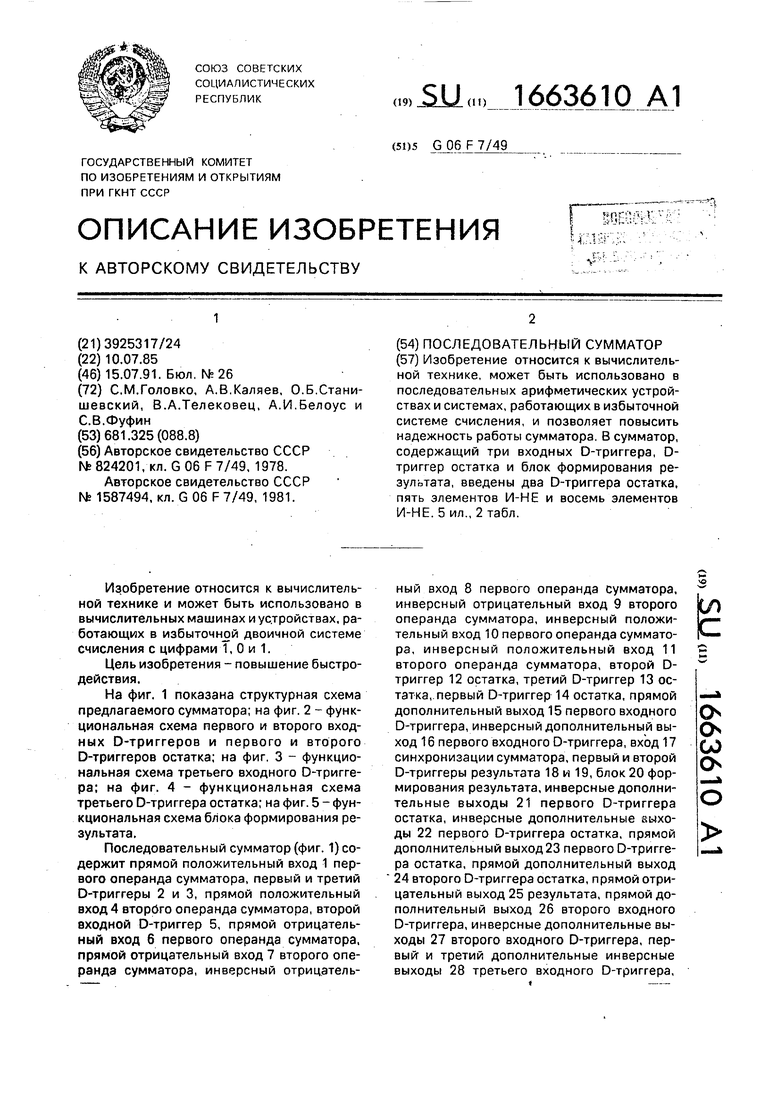

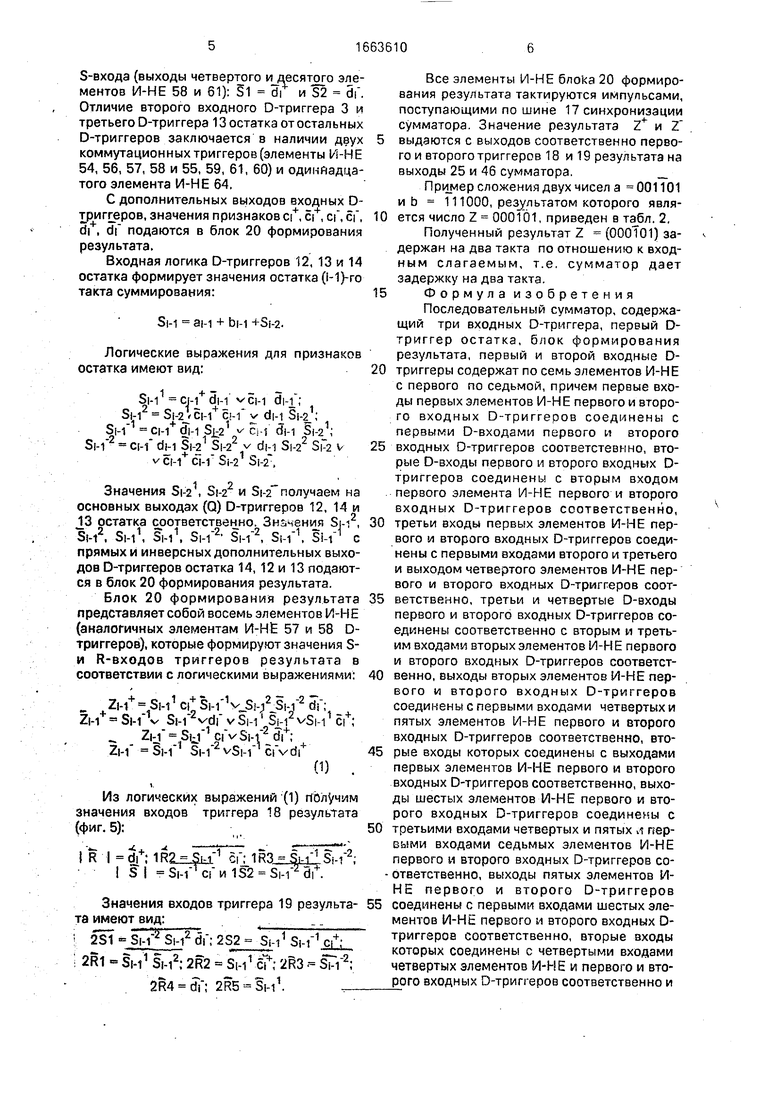

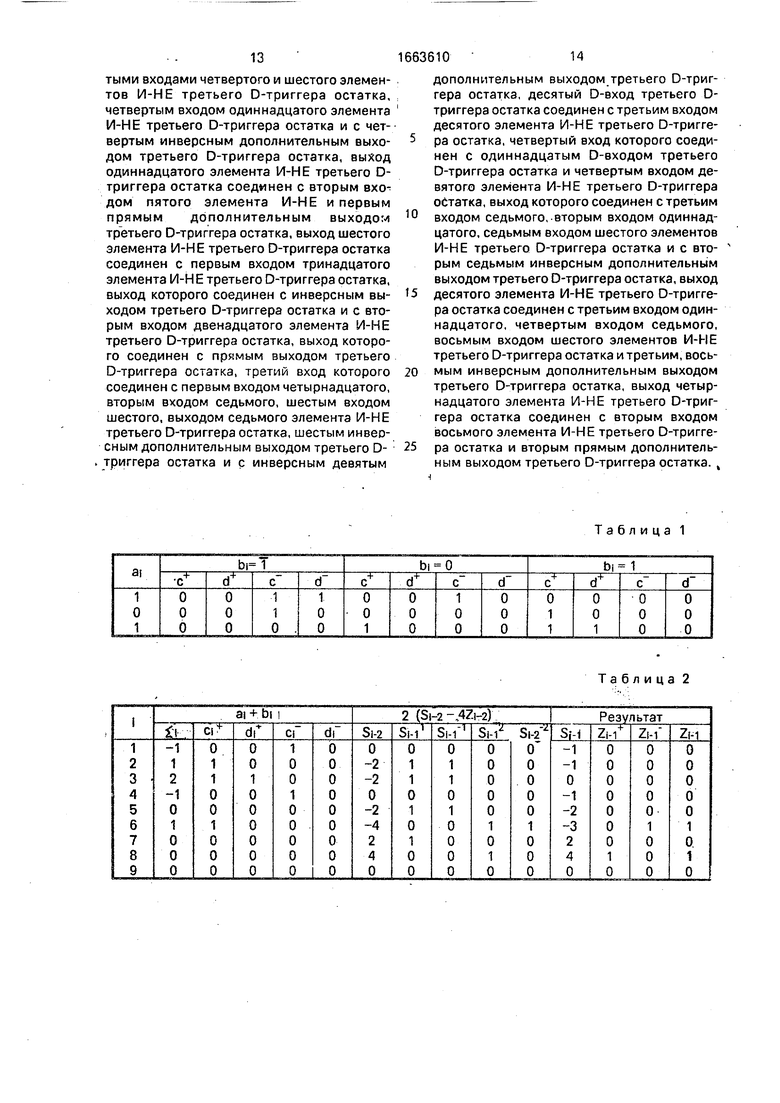

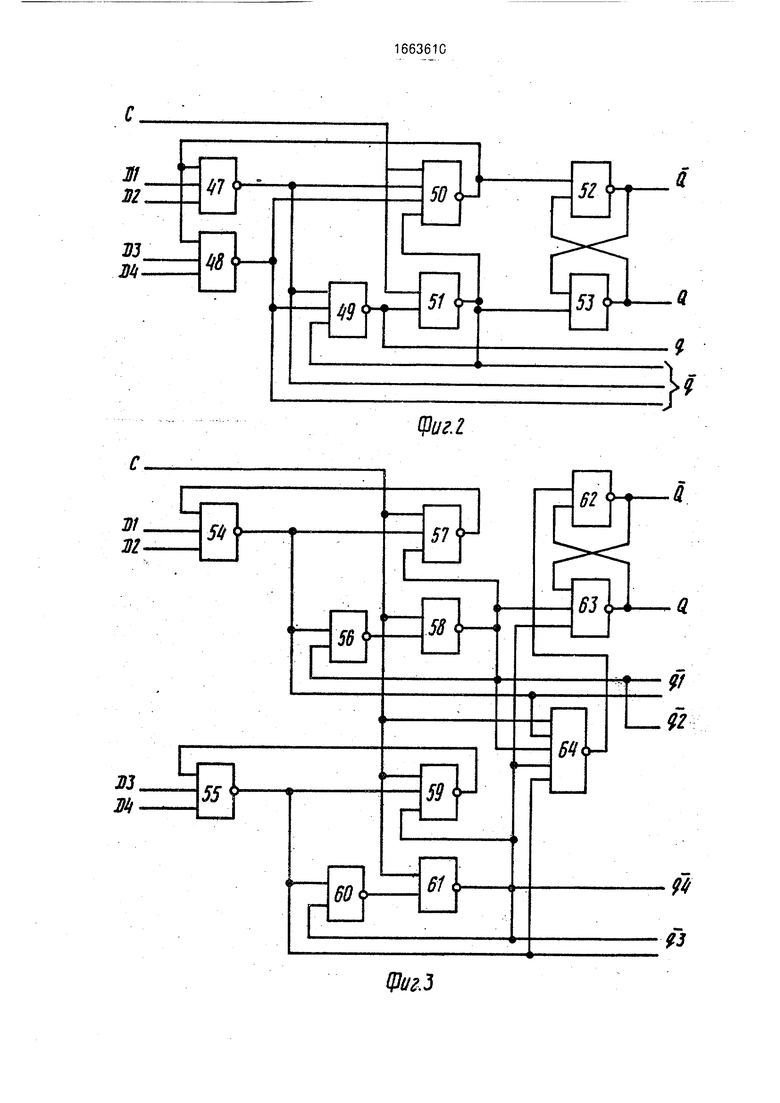

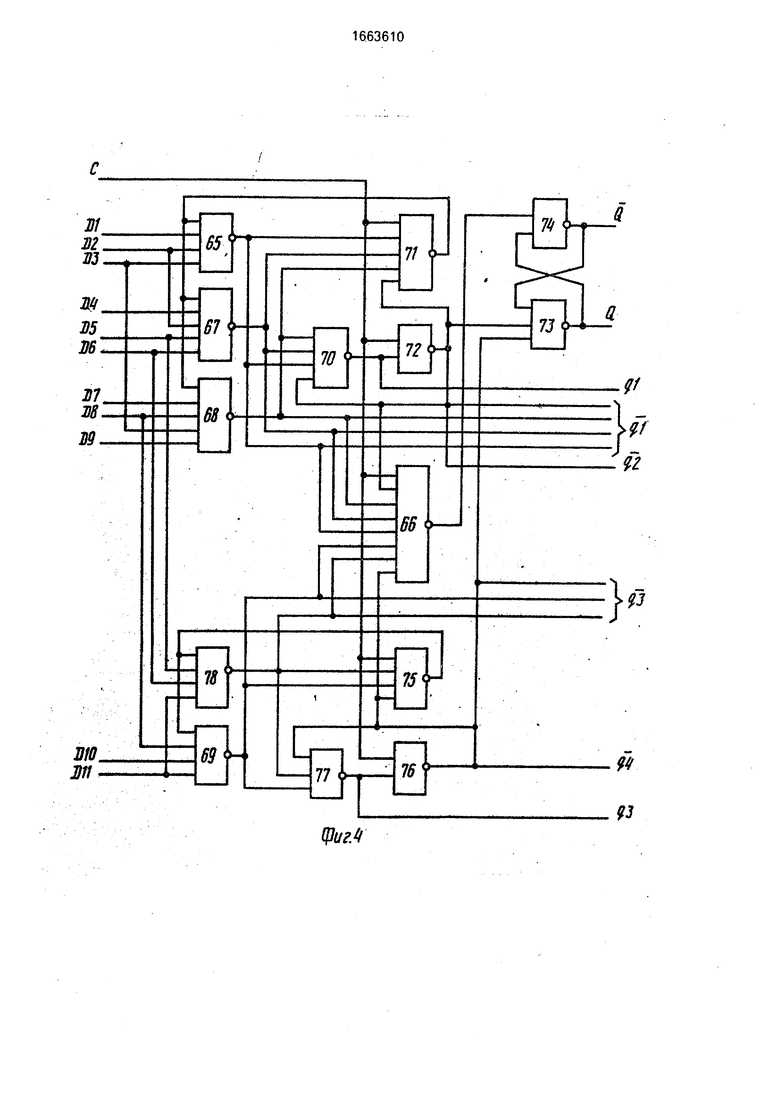

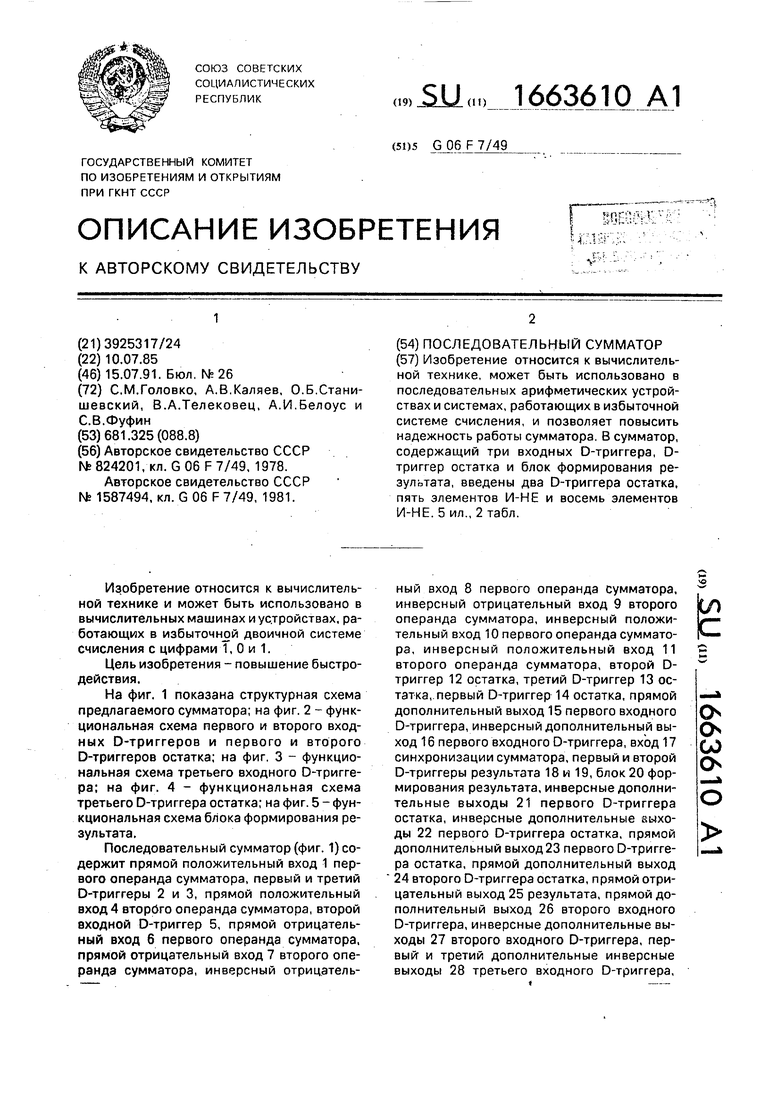

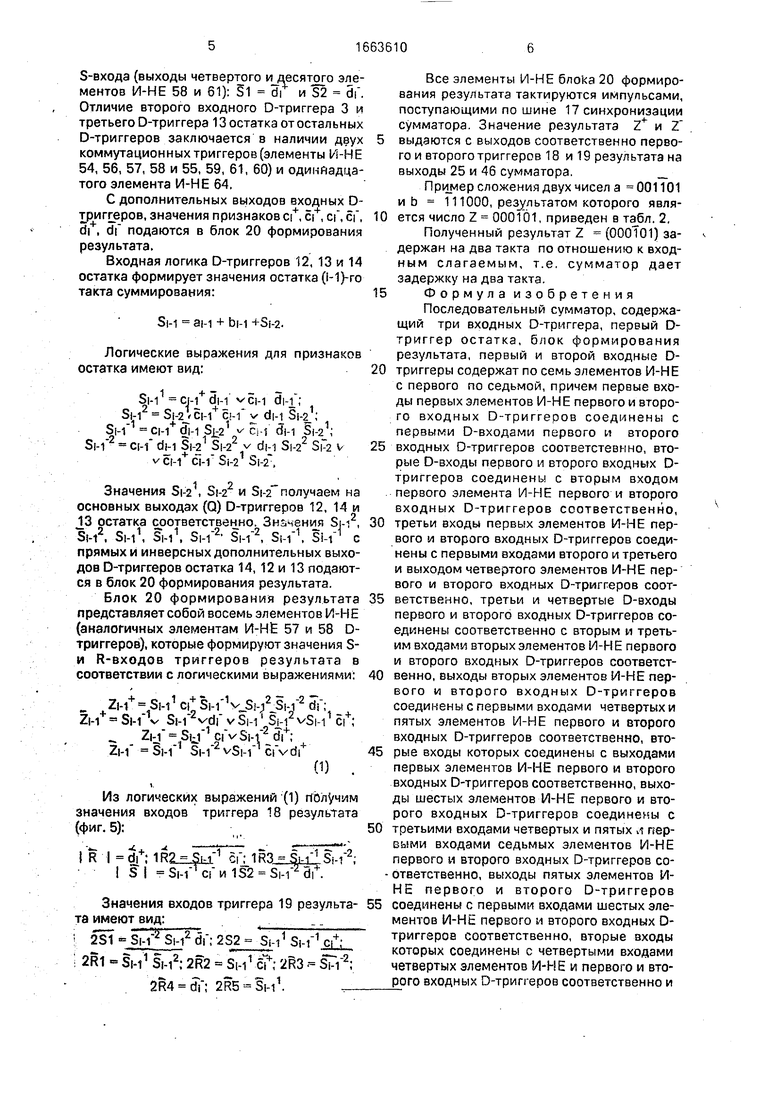

На фиг. 1 показана структурная схема предлагаемого сумматора; на фиг. 2 - функциональная схема первого и второго входных D-триггеров и первого и второго D-триггеров остатка; на фиг. 3 - функциональная схема третьего входного D-триггера; на фиг. 4 - функциональная схема третьего D-триггера остатка; на фиг. 5 - функциональная схема блока формирования результата.

Последовательный сумматор (фиг. 1) содержит прямой положительный вход 1 первого операнда сумматора, первый и третий D-триггеры 2 и 3, прямой положительный вход 4 вторбго операнда сумматора, второй входной D-триггер 5, прямой отрицательный вход 6 первого операнда сумматора, прямой отрицательный вход 7 второго операнда сумматора, инверсный отрицательный вход 8 первого операнда сумматора, инверсный отрицательный вход 9 второго операнда сумматора, инверсный положительный вход 10 первого операнда сумматора, инверсный положительный вход 11 второго операнда сумматора, второй D- триггер 12 остатка, третий D-триггер 13 остатка, первый D-триггер 14 остатка, прямой дополнительный выход 15 первого входного D-триггера, инверсный дополнительный выход 16 первого входного D-триггера, вход 17 синхронизации сумматора, первый и второй D-триггеры результата 18 и 19, блок 20 формирования результата, инверсные дополнительные выходы 21 первого D-триггера остатка, инверсные дополнительные аыхо- ды 22 первого D-триггера остатка, прямой дополнительный выход 23 первого D-триггера остатка, прямой дополнительный выход 24 второго D-триггера остатка, прямой отрицательный выход 25 результата, прямой дополнительный выход 26 второго входного D-триггера, инверсные дополнительные выходы 27 второго входного D-триггера, первый и третий дополнительные инверсные выходы 28 третьего входного D-триггера,

О

о

w

О

о

второй дополнительный инверсный выход 29 третьего входного D-триггера, четвертый и пятый инверсные дополнительные выходы 30 третьего входного D-триггера, шестой инверсный дополнительный выход 31 третьего входного D-триггера, прямой первый дополнительный выход 32 третьего D-триггера остатка, первый, второй, третий и четвертый инверсные выходы 33 третьего D-триггера остатка, пятый инверсный дополнительный выход 34 третьего D-триггера остатка, шестой, седьмой и восьмой инверсные дополнительные выходы 35 третьего D-триггера остатка, второй прямой дополнительный выход 36 третьего D-триггера остатка, девятый инверсный дополнительный выход 37 третьего D-триггера остатка, выходы 38 - 45 блока формирования результата, прямой положительный выход 46 результата.

Каждый первый и второй входные D- триггеры и каждый первый и второй D-триг- геры остатка (фиг. 2) содержат семь элементов И-НЕ 47 - 53.

Третий входной D-триггера (фиг. 3} содержит одиннадцать элементов Й-НЕ 54 - 64.

Третий D-триггер остатка (фиг, 4) содержит четырнадцать элементов И-НЕ 65 - 78.

Блок формирования результата содержит восемь элементов И-НЕ 79 - 86.

Алгоритм работы сумматора Елмеет вид

2|-1

1 при Si-1 3 : О при Si-i I 3 ; Т при Si-i -3 ,

где SM at -ь bi + 2(Si-2 - 4Zi-a) - текущая сумма.

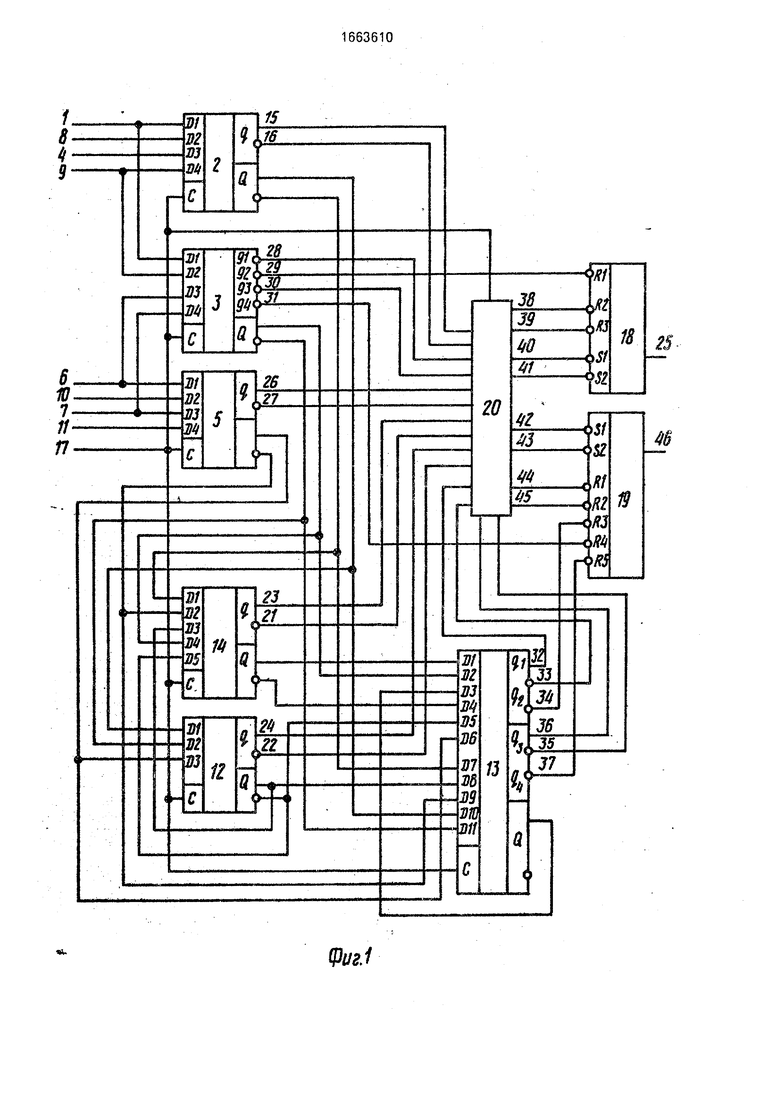

Входная логика входных D-триггеров 2, 3 и 5 преобразует значения слагаемых а и bi, поступающих последовательно разряд за разрядом, начиная со старшего разряда, на входные шины 1, 4, 6, 7, 8,..., 11 сумматора, в значения признаков с+, с, d+ и сГ в соответствии с табл. 1.

На основании табл. 1 получим:

+ 4-г- Ci ai bi

Г 4V bi

+ as- ;

ci af bi V bf as ; df ai+ и di ai bf.

Работу D-трмггера рассмотрим на основе первого входного D-триггера 2 (фиг. 2). В отсутствие тактового импульса (на С-входе триггера нулевой потенциал) с выходов элементов И-НЕ 50 и 51 на входы выходного D-триггера подается единичный потенциал и триггер сохраняет свое состояние. ЕСЛИ на

одним из входов элемента И-НЕ 47 или 48 буде.т нулевой потенциал (ci+ 0), то с выходов Дпементов И-НЕ на входы элементов И-Ht и 59 будет подаваться единичный

тяенцлал, а с выхода элемента И-НЕ 49 на вход элементу И-НЕ 51 - нулевой потенциал. По переднему фронту тактового импульса, поступающего на С-вход триггера, с выхода элемента И-НЕ 51 на вход (вход S)

элемента И-НЕ 53 будет подаваться по- прежнему единичный потенциал, а с выхода элемента И-НЕ 50 нг вход (вход R) элемента И-НЕ 52 поступит нулевой потенциал и выходной триггер (элементы И-НЕ 52 и 53) устанрвится в нулевое состояние, т.е. на прямой выход (Q) триггера будет выдаваться нулевок потенаиал(с|-1+ 0), а на инверсный выход (Q) - единичный потенциал си+ 1. При этом на дополнительные выходы (q и q)

триггера будуть выдаваться значения ci+ (с выхода третьего элемент И-НЕ 49) (с выходов элементов И-НЕ 47, 48 и 51). Чтобы изменение входного сигнала (например, на входах элемента И-НЕ 47) во время тактовогс импульса не ши/.ло на работу D-триггера (запись по переднему фронту импульса), в триггер введена триггерная защелка, т.е. выход четвертого элемента И-НЕ 51 соединен с входом второго элемента И-НЕ 50.

Поэтому же дополнительный инверсный выход (q cf1) образован выходами трех элементов И-НЕ 47,48 и 51 (аналогично входам второго элемента И-НЕ 50). Прямой дополнительный выход (q cf) является выходом

третьего элемента И-НЕ 49 (аналогично вхо- дам четвертого элемента И-НЕ 51). Если же на входах элемента И-НЕ 47 или элемента И-НЕ 48 отсутствует нулевой потенциал (например, а Ь - 1), то на одном из входов

элементов И-НЕ 50 и 49 будет нулевой потенциал, а на выходе элемента И-НЕ 49 - единичный потенциал. С приходом тактового импульса с выхода элемента И-НЕ 51 нулевой потенциал перебросит выходной

триггер в единичное состояние (Q см 1 и Q сы+ 0), При этом на прямом дополнительном выходе (q) триггера будет единичный потенциал (cf 1), а на инверсном дополнительном выходе (q)- нулевой потенциал (cj+ 0). Аналогично образуются признаки df, df, cf к cf во втором и третьем входных D-триггерах З и 5, Одиннадцатый элемент И-НЕ 64 второго входного триггера 3 аналогичен второму его элементу И-НЕ 57

и выполняет функцию

R 8+

а;

Выходной триггер (элементы И-НЕ 63 и J52) второго входного D-триггера имеет два

S-входа (выходы четвертого идесятого элементов И-НЕ 58 и 61): S1 di и S2 df. Отличие второго входного D-триггера З и третьего D-триггера 13 остатка от остальных D-триггеров заключается в наличии двух коммутационных триггеров (элементы И-НЕ 54, 56, 57, 58 и 55, 59, 61, 60) и одиннадцатого элемента И-НЕ 64.

С дополнительных выходов входных D- триггеров, значения признаков ci+, ci+, cf, cf, di+, df подаются в блок 20 формирования результата.

Входная логика D-триггеров 12, 13 и 14 остатка формирует значения остатка (И)-го такта суммирования:

SM аи + bi-1 -f-Si-2.

Логические выражения для признаков остатка имеют вид:

Si-11 ci-i+di-i vci-1

Зм2 Si-2 см+ CM v di-i SiV;

- CM dj-i Sy1 v ci-i Ян Si-2 ;

di-1 S|-2 S|-2 v d|-1 S|-2 V v CM+ CI-Г Si-2 Si-2,

Значения Si-21, Si-22 и Si-2 получаем на основных выходах (Q) D-триггеров 12, 14 и 13 остатка соответственно. 5м2, St-12. Si-11, Зм1, , , Si-i 1 с прямых и инверсных дополнительных выходов D-триггеров остатка 14, 12 и 13 подаются в блок 20 формирования результата.

Блок 20 формирования результата представляет собой восемь элементов И-НЕ (аналогичных элементам И-НЕ 57 и 58 D- триггеров), которые формируют значения S- и R-входов триггеров результата в соответствии с логическими выражениями:

SM

ZM+ Зм1 Si-Г1 vJSM jSM df;

7, . - О. m . С. ,,rt, .- С, . С, xCi A ,

;2 Si-Г2

Zi-Г Si-Г V v SM Si-12 vSi-i ЕГ; cfvSi-Г2 di+;

O. O .2 fc ,Ј 1 -J t

ZM Si-rvSi-r ciVdi

CD

Из логических выражений (1) гГблучим значения входов триггера 18 результата (фиг. 5):

IR l di+;1R

1 of: S I Зм 1сГи152 .

Значения входов триггера 19 результата имеют вид:

2R1

281 °JM ZSM2 df; 252- Si-i1 3|-Г1сь- 1 §м1 §м2; 2R2 Зм1 сТ+; 2ЙЗ зГГ2; 2R4 2R5 Si-i1.

Все элементы И-НЕ блока 20 формирования результата тактируются импульсами, поступающими по шине 17 синхронизации сумматора. Значение результата и Z

выдаются с выходов соответственно первого и второго триггеров 18 и 19 результата на выходы 25 и 46 сумматора.

сложения двух чисел а 001101 иЬ 111000, результатом которого явля0 ется число Z 000101, приведен в табл. 2.

Полученный результат Z (ОООТ01) задержан на два такта по отношению к входным слагаемым, т.е. сумматор дает задержку на два такта.

5Ф о р м у л а и з о б р е т е н и я

Последовательный сумматор, содержащий три входных D-триггера, первый D- триггер остатка, блок формирования результата, первый и второй входные D0 триггеры содержат по семь элементов И-НЕ с первого по седьмой, причем первые входы первых элементов И-НЕ первого и второго входных D-триггеров соединены с первыми D-входами первого и второго

5 входных D-триггеров соответственно, вторые D-входы первого и второго входных D- триггеров соединены с вторым входом первого элемента И-НЕ первого и второго входных D-триггеров соответственно,

0 третьи входы первых элементов И-НЕ первого и второго входных D-триггеров соединены с первыми входами второго и третьего и выходом четвертого элементов И-НЕ первого и второго входных D-триггеров соот5 ветственно, третьи и четвертые D-входы первого и второго входных D-триггеров соединены соответственно с вторым и третьим входами вторых элементов И-НЕ первого и второго входных D-триггеров соответст0 венно, выходы вторых элементов И-НЕ первого и второго входных D-триггеров соединены с первыми входами четвертых и пятых элементов И-НЕ первого и второго входных D-триггеров соответственно, вто5 рые входы которых соединены с выходами первых элементов И-НЕ первого и второго входных D-триггеров соответственно, выходы шестых элементов И-НЕ первого и второго входных D-триггеров соединены с

0 третьими входами четвертых и пятых и первыми входами седьмых элементов И-НЕ первого и второго входных D-триггеров со- - ответственно, выходы пятых элементов И- НЕ первого и второго D-триггеров

5 соединены с пераыми входами шестых элементов И-НЕ первого и второго входных D- триггерое соответственно, вторые входы которых соединены с четвертыми входами четвертых элементов И-НЕ и первого и второго входных D-триггеров соответственно и

С-входами первого и второго входных D- триггеров соответственно, выходы седьмых элементов И-НЕ первого и второго входных D-триггеров соединены с инверсными выходами первого и второго входных D-триггеров соответственно и с вторыми входами третьих элементов И-НЕ первого и второго входных D-триггеров соответственно, вторые входы которого соединены с выходами седьмых элементов И-НЕ первого и второго входных D-триггеров соответственно и прямыми выходами первого и второго входных D-триггеров соответственно, первые D-вхо- ды первого и второго входных D-триггеров соединены соответственно с прямым положительным входом первого операнда и прямым отрицательным входом первого операнда сумматора, третий входной D- триггер содержит девять элементов И-НЕ, первые входы первого и второго элементов И-НЕ третьего входного D-триггера соединены с его С-входом, выход второго элемента И-НЕ третьего входного D-триггера соединен с первыми входами третьего, четвертого и вторым входом первого элемента И-НЕ третьего входного D-триггера, выход пятого элемента И-НЕ третьего входного D- триггера соединен с третьим входом первого и вторым входом четвертого элементов И-НЕ третьего входного D-триггера, выход четвертого элемента И-НЕ третьего входного D-триггера соединен с вторым входом второго элемента И-НЕ третьего входного D-триггера, первый и второй входы пятого элемента И-НЕ третьего входного D-триггера соединены соответственно с первым и вторым D-входами третьего входного D- триггера, третий вход пятого элемента И-Н Е третьего входного D-триггера соединен с выходом первого элемента И-НЕ третьего входного D-триггера, выход третьего элемента И-НЕ третьего входного D-триггера соединен с прямым выходом третьего входного D-трмггера и первым входом шестого элемента И-НЕ третьего входного D-триггера, выход которого соединен с вторым входом третьего элемента И-НЕ третьего входного D-триггера и инверсным выходом третьего входного D-триггера, первый и второй входы седьмого элемента И-НЕ третьего входного D-триггера соединены соответственно с третьим и четвертым входами третьего входного D-триггера, первый D-вход третьего входного D-триггера соединен с первым D-входом первого входного D-триггера, блок формирования результата содержит восемь элементов И-НЕ, первые входы первого, второго третьего, четвертого элементов И-НЕ блока формирования результата соединены с С-входами первого,

второго и третьего входных D-триггеров и с тактирующим входом сумматора, отличающийся тем, что, с целью повышения быстродействия сумматора, в него введены

первый, второй и третий D-триггеры остатка и первый, второй триггеры результата, второй D-вход первого входного D-триггера соединен с инверсным отрицательным входом первого операнда сумматора., прямой поло0 хительный вход второго операнда сумматора соединен с третьим D-входом первого входного D-триггера и вторым D-входом третьего входного D-триггера, третий D- вх од которого соединен с прямым отрица5 тельным входом первого операнда сумматора, инверсный положительный вход первого операнда сумматора соединен с вторым D-эходом второго входного D-триггера. третий D-вход которого соединен с

0 прямым отрицательным входом второго операнда сумматоре и четвертым D-зходом третьего входного D-триггера, инверсный положительный вход второго операнда сумматора соединен с четвертым D-входом вто5 рого сходного D-триггера, инверсный отрицательный вход второго операнда сумматора соединен с четвертым D-входом первого входногс D-триггера, в третий входной D-триггер введены четыре элемента И-НЕ с

0 десятого по тринадцатый, причем первые входы десятого, одиннадцатого, двенадцатого элементов И-НЕ третьего входного D- триггера соединены с первым входом второго элемента И-НЕ третьего входного

5 D-триггера, выход которого соединен с первым и вторым инверсным дополнительным выходом третьего входного D-триггера и вторым входом двенадцатого элемента И- НЕ третьего входного D-триггера, выход ко0 торого соединен с вторым входом тринадцатого элемента И-НЕ третьего входного D-триггера, выход пятого И-НЕ третьего входного D-триггера соединен с третьим инверсным дополнительным выходом

5 третьего входного D-триггера и с третьим входом двенадцатого элемента И-НЕ треть- .его входного D-триггера, четвертый вход которого соединен с вторыми входами третьего и десятого, первым входом тркнад0 цатого и выходом одиннадцатого элементов И-НЕ третьего входного D-триггера, третий вход седьмого элемента И-НЕ третьего входного D-триггера соединен с выходом десятого элемента И-НЕ третьего входного

5 1 триперз третий вход которого соединен с вторым входом тринадцатого и выходов седьмого элементов И-НЕ третьего входного D-триггера, выход шестого элемента И- НЕ третьего входного D-триггера соединен с вторым входом сдимкадцатого элемента

И-НЕ третьего входного D-триггера, пятый вход двенадцатого элемента И-НЕ третьего входного D-триггерз соединен с вторым входом тринадцатого элемента И-НЕ третьего входного D-триггера, выходы седьмого и одиннадцатого элементов И-НЕ соединены соответственно с четвертым и пятым инверсным дополнительным выходом третьего входного D-триггера, второй вход десятого элемента И-НЕ третьего входного D-тригге- ра соединеен с шестым инверсным дополнительным выходом третьего входного D-триггера, выходы пятых элементов И-НЕ первого и второго входов D-тркг геров соответственно и первого и второго D-триггеров остатка соответственно соединены с прямым дополнительным выходом первого и второго входных D-триггероз соответственно и прямым дополнительным выходом первого и второго D-триггеров остзгка соответственно, выходы первых, вторых и шестых элементов И-НЕ первого и второго входных D-триггеров соединены соответственно с первым и вторым, третьим инверсными дополнительными выходами первого и второго входных D-триггеров соответственно, выходы первых, вторых и шестых элементов И-НЕ первого и второго D-триггеров остатка соединены соответственно с первым, вторым, третьим инверсными до- полнительными выходами первого и второго D-триггеров остатка соответственно, пятый D-вход первого D-триггера остатка соединен с четвертым входом второго элемента И-НЕ первого D-триггера остатка, С- входы первого, второго, третьего D-триггеров остатка соединены с тактирующим входом сумматора, первый D-вход третьего триггера остатка соединен с прямым выходом первого D-триггера остатка, второй D-вход третьего D-трлггера остатка соединен с четвертым D-входом первого D- триггера остатка и прямым выходом третьего входного D-триггера, третий D-вход третьего D-триггера остатка соединен с его прямым выходом, четвертый D-вход третьего D-триггера остатка соединен с инверсным выходом первого D-триггера остатка, инверсный выход второго D-триггера остатка соединен с пятыми D-входами первого и третьего D-триггеров остатка, прямой выход второго входного D-триггера соединен с третьим D-входом второго D-триггера остатка и шестым входом третьего D-триггера остатка, седьмой D-вход которого соединен с первым D-входом первого D-триггера остатка и инверсным выходом первого входного D-триггера, восьмой D-вход третьего D-rpt/srrepa остатка соединен с прямым выходом второго D-триггера остатка и третьим

D-входом первого D-триггера остатка, второй D-вход которого соединен с прямым выходом второго входного D-триггера и девятым D-входом третьего D-триггера остатка, десятый D-вход которого соединен с прямым выходом первого входногоО-триге- ра и первым D-входом второго D-триггера остатка, второй D-вход которого соединен с инверсным выходом третьего входного D- триггера и одиннадцатым D-входом.третье- го D-триггера остатка, второй, третий, четвертый входы первого элементов И-НЕ блока формирования результата соединены соответственно с первым,вторым и третьим инверсными дополнительными выходами второго входного D-триггера, первый и второй входы пятого элемента И-НЕ блока фор- мирования результата соединены соответственно с первым и вторым инверсным дополнительным выходом третьего входного D-триггера, третий инверсный дополнительный выход которого соединен с первым R-входом первого триггера результата, второй R-вход которого соединен с выходом первого элемента И-НЕ блока формирования результата, выход второго элемента И-НЕ блока формирования результата соединен с третьим R-входом первого триггера результата, первый и второй S-входы которого соединены соответственно с выходом шестого и пятого элементов И-НЕ блока формирования результата, второй и третий входы третьего элемента И-НЕ блока формирования результата соединены соответственно с четвертым и пятым инверсным дополнительными выходами третьего входного D-триггера, первые входы шестого, седьмого, восьмого и третий вход пятого элементов И-НЕ блока формирования результата соединены с тактирующим входом сумматора, второй вход шестого элемента И-НЕ блока формирования результата соединен с прямым дополнительным выходом второго входного D-триггера, четвертый вход третьего элемента И-НЕ блока формирования результата соединен с прямым дополнительным выходом первого D-триггера остатка, прямой дополнительный выход второго D-триггера остатка соединен с ьторы- ми входами четвертого и восьмого элементов И-НЕ блока формирования результата, третий, четвертый, пятый входы восьмого элемента И-НЕ блока формирования результата соединены соответственно с первым, вторым и третьим инверсным дополнительными выходами первого входного D-триггера, прямой дополнительный выход которого соединен с третьим входом четвертого элемента И-НЕ блока формирования результата, второй, третий, четвертый вхо

11

ды седьмого элемента И-НЕ олока формирования результата соединены соответственно с первым, вторым, третьим инверсными дополнительными выходами первого D-триггера остатка, первый, второй, третий инверсные дополнительные выходы второго D-триггера остатка соединены соответственно с пятым, шестым, седьмым входами седьмого элемента И-НЕ блока формирования результата, выход которого соединен с первым R-входом второго триггера результата, второй R-вход которого соединен с выходом восьмого элемента И-НЕ блока формирования результата, выходы третьего и чет- вертого элементов И-НЕ блока формирования результата соединены соответственно с первым и вторым S-входами второго триггера результата, первый прямой дополнительный выход третьего Dтриггера остатка соединен с четвертым входом пятого элемента И-НЕ блока формирования результата, второй, третий,четвертый, пятый входы двадцатого элемента И-НЕ блока формирова ния результата соединены соответственно с пятым, шестым, седьмым, восьмым входами третьего элемента И-НЕ блока формирования результата и соответственно с первым, вторым, третьим, четвертым инверсными дополнительными выходами третьего D-триггера ос- татка, пятый инверсный дополнительный выход которого соединен с третьим R-входом второго триггера результата, четвертый R-вход которого соединен с четвертым инверсным дополнительным выходом третьего входного D-триггера, пятый вход первого и третий вход шестого элементов И-НЕ блока формирования результата соединены с прямым третьим дополнительным выходом третьего D-триггера остатка, шестой, седьмой, восьмой инверсные дополнительные выходы третьего D-триггера остатка соединены соответственно с шестым, седьмым, восьмым входом второго и соответственно с четвертым, пятым, шестым входами четвертого элемента И-НЕ блока формирования результата, девятый инверсный дополнительный выход третьего D-триггера остатка соединен с пятым R-входом второго триггера результата, выход которого соединен с положительным выходом результата сумматора, отрицательный выход результата которого соединен с выходом первого триггера результата, третий D-триггер остатка содержит четырнадцать элементов И- НЕ, причем первый вход первого элемента И-НЕ D-триггера остатка соединен с пер- вым D-входом третьего D-триггера остатка, второй D-вход которого соединен с вторым входом пераого и с первым входом второго

12

0

5

0 0 5

5

0

5

элемента И-НЕ третьего D-триггера остатка, третий D-вход третьего D-триггера остатка соединен с третьим входом первого и первым входом третьего элементов И-НЕ третьего D-триггера остатка, четвертый D-вхо д третьего D-триггера остатка соединен с вторым входом вгооого элемента И-НЕ третьего D-триггера остатка, второй вход третьего, третий вход второго, четвертый вход первого элемента И-НЕ третьего D-триггера остатка соединен с выходом четвертого элемента И-НЕ третьего D-триггера остатка, первый вход которо о соединен с первыми входами пятого, шестого, седьмого, восьмого элементов И-НЕ третьего D-триггера остатка и с С-БХОДОМ третьего D-триггера остатка, выход седьмого элемента И-НЕ третьего D-триггера остатка соединен с первыми входами девятого и десятого элементов И-НЕ третьего D-триггера остатка, пятый D-вход третьего D-триггера остатка соединен с четвертым входом второго и вторым входом девятого элементов И-НЕ третьего D-триггера остатка, шестой D-вход третьего D-триггера остатка соединен с пятым входом второго и третьим входом девятого элементов И-НЕ третьего D-триггера остатка, седьмой D-вход третьего D-триггера остатка соединен с третьим входом третьего элемента И-НЕ третьего D-триггера остатка, восьмой D-вход третьего D-триггера остатка соединен с четвертым входом третьего и вторым входом десятого элементов И-НЕ третьего D-триггера остатка, девятый D-вход которого соединен с пятым входом третьего элемента И-НЕ третьего D- триггера остатка, выход которого соединен с вторыми входами четвертого и шестого, с первым входом одиннадцатого элементов И-НЕ третьего D-триггера остатка и с первым инверсным дополнительным выходом третьего D-триггера остатка, выход пятого элемента И-НЕ третьего D-триггера остатка соединен с вторым входом одиннадцатого, с третьими входами шестого и четвертого элементов И-НЕ третьего D-триггера остатка, первым входом двенадцатого элемента И-НЕ третьего D-триггера остатка, вторым инверсным дополнительным выходом третьего D-триггера остатка и с пятым инверсным дополнительным выходом третье- roD-триггера остатка, выход второго элемента И-НЕ третьего входного D-триггера соединен с третьим входом одиннадцатого, с четвертыми входами четвертого и шестого элементов И-НЕ третьего D-триггера остатка и третьим инверсным дополнительным выходом третьего D-триггера остатка, выход первого элемента И-НЕ третьего D-триггера остатка соединен с пя

13

тыми входами четвертого и шестого элементов И-НЕ третьего D-триггера остатка, четвертым входом одиннадцатого элемента И-НЕ третьего D-триггера остатка и с четвертым инверсным дополнительным выходом третьего D-триггера остатка, выход одиннадцатого элемента И-НЕ третьего D- триггера остатка соединен с вторым входом пятого элемента И-НЕ и первым прямым дополнительным выходом третьего D-триггера остатка, выход шестого элемента И-НЕ третьего D-триггера остатка соединен с первым входом тринадцатого элемента И-НЕ третьего D-триггера остатка, выход которого соединен с инверсным выходом третьего D-триггера остатка и с вторым входом двенадцатого элемента И-НЕ третьего D-триггера остатка, выход которого соединен с прямым выходом третьего D-триггера остатка, третий вход которого соединен с первым входом четырнадцатого, вторым входом седьмого, шестым входом шестого, выходом седьмого элемента И-НЕ третьего D-триггера остатка, шестым инверсным дополнительным выходом третьего D- триггера остатка и с инверсным девятым

0

63610

0 5

5

14

дополнительным выходом третьего D-триггера остатка, десятый D-вход третьего D- триггера остатка соединен с третьим входом десятого элемента И-НЕ третьего D-триггера остатка, четвертый вход которого соединен с одиннадцатым D-входом третьего D-триггера остатка и четвертым входом девятого элемента И-НЕ третьего D-триггера остатка, выход которого соединен с третьим входом седьмого, вторым входом одиннадцатого, седьмым входом шестого элементов И-НЕ третьего D-триггера остатка и с вторым седьмым инверсным дополнительным выходом третьего D-триггера остатка, выход десятого элемента И-НЕ третьего D-триггера остатка соединен с третьим входом одиннадцатого, четвертым входом седьмого, восьмым входом шестого элементов И-НЕ третьего D-триггера остатка и третьим, восьмым инверсным дополнительным выходом третьего D-триггера остатка, выход четырнадцатого элемента И-НЕ третьего D-триггера остатка соединен с вторым входом восьмого элемента И-НЕ третьего D-триггера остатка и вторым прямым дополнительным выходом третьего D-триггера остатка. %

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Адаптируемый четверичный сумматор | 1986 |

|

SU1417011A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1987 |

|

SU1439577A1 |

| Четверичный сумматор | 1983 |

|

SU1124290A1 |

Изобретение относится к вычислительной технике, может быть использовано в последовательных арифметических устройствах и системах, работающих в избыточной системе счисления, и позволяет повысить надежность работы сумматора. В сумматор, содержащий три входных D-триггера, D-триггер остатка и блок формирования результата, введены два D-триггера остатка, пять элементов И - НЕ и восемь элементов И - НЕ. 5 ил., 2 табл.

Таблица 1

Таблица 2

«ft.

flw./

W9401-

г

50

- jffiffi

50

Фиг. г

ЩигЗ

fc4

| Устройство для сложения в избыточнойдВОичНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824201A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1981 |

|

SU1587494A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-15—Публикация

1985-07-10—Подача