9

ел

00

| сд

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Сигнатурный анализатор | 1987 |

|

SU1499349A1 |

| Сигнатурный анализатор | 1985 |

|

SU1247876A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Сигнатурный анализатор | 1990 |

|

SU1748154A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1797118A1 |

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

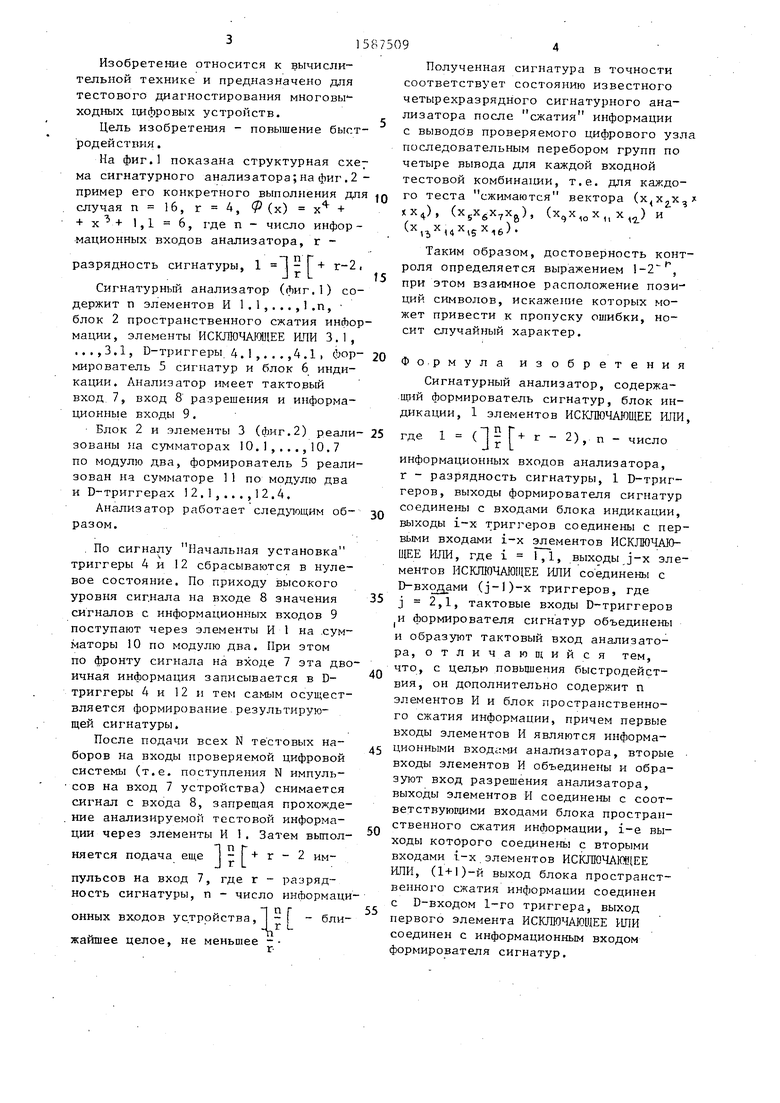

Изобретение относится к вычислительной технике и может использоваться при построении систем тестового диагностирования дискретных объектов. Цель изобретения - повышение быстродействия контроля. Сигнатурный анализатор содержит элементы И 1, блок 2 пространственного сжатия информации, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3, D - триггеры 4, формирователь 5 сигнатур и блок 6 индикации. Анализатор за один такт осуществляет преобразования, которые в анализаторе BIIBO осуществляются лишь за ]N/R[ тактов, где N - число контролируемых каналов, а R - разрядность сигнатуры. 2 ил.

Изобретение относится к вычислительной технике и предназначено для тестового диагностирования многовы - ходных цифровых устройств.

Цель изобретения - повышение быстродействия.

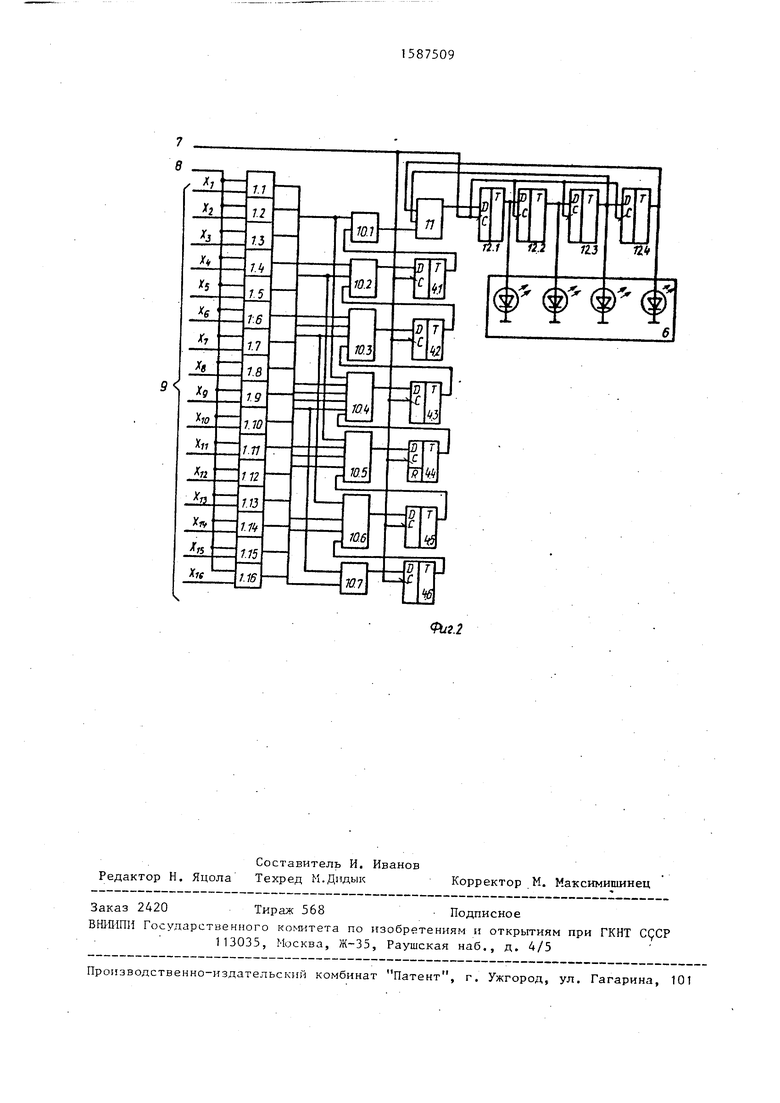

На фиг.1 показана структурная схеу ма сигнатурного анализатора; на фиг.2 Полученная сигнатура в точности соответствует состоянию известного четырехразрядного сигнатурного анализатора после сжатия информации с выводов проверяемого цифрового узла последовательным перебором групп по четыре вывода для каждой входной тестовой комбинации, т.е. для каждопример его конкретного выполнения для ,о го теста сжимаются вектора (х х х х случая п 16 г А, Т Сх) х н- ,х,). (x,x,x,xj, (х„х,„ х .. х ..) и

+ X + 1,1-6, где п - число информационных входов анализатора, г - разрядность сигнатуры, 1 1 - Г

(х,,,х,4Х,5Х

16

):

+ г-2.

15

Сигнатурньй анализатор (фиг.1) содержит п элементов И 1.1,...,l.n, блок 2 пространственного сжатия информации , элементы ИСКЛЮЧАКШ1ЕЕ ИЛИ 3.1, ...,3.1, D-триггеры. 4. 1 ,.. .,4.1 , фор- 20 мирователь 5 сигнатур и блок 6 инди- ° кации. Анализатор имеет тактовый вход, 7, вход 8 разрешения и информационные входы 9.

Блок 2 и элементы 3 (фиг.2) реали- 25 зованы на сумматорах 10.1,. . .,10.7 по модулю два, формирователь 5 реализован на сумматоре 11 по модулю два и D-триггерах I2.1,...,12.4.

Анализатор работает следующим образом.

Таким образом, достоверность контроля определяется выражением 1-2, при этом взаимное расположение позиций символов, искажение которых может привести к пропуску ошибки, носит случайный характер.

рмула изобретения Сигнатурный анализатор, содержа- цгнй формирователь сигнатур, блок индикации, 1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, где 1

(-2).

п - число

30

информационных входов анализатора, г - разрядность сигнатуры, 1 D-триг- геров, выходы формирователя сигнатур соединен с входами блока индикации, вьгходы i-x триггеров соединены с первыми входами i-x Э 1ементов ИСКЛЮЧАКЬ- D1EE ШШ, где i 1,1, выходы j-x элементов ИСКЛЮЧАЮЩЕЕ ИЛИ со ёдинены с D-вхо ами (j-l)-x триггеров, где j 2,1, тактовые входы D-триггеров |И формирователя сигнатур объединены и образуют тактовый вход анализатора, отличающийся тем, 40 целью повьщ ения быстродействия, он дополнительно содержит п элементов И и блок пространственного сжатия информации, причем первые входы элементов И являются информа- 45 ционными входами анализатора, вторые . входы элементов И объединены и образуют вход разрешения анализатора, выходы элементов И соединены с соот- ветствуюодами входами блока лростран- jQ ственного сжатия информации, i-e выходы которого соединены с вторыми входами t-x.элементов ИСКЛЮЧАКЦЕЕ ИЛИ, (1+1)-й выход блока пространственного сжатия информации соединен 55 D-входом 1-го триггера, выход первого элемента ИСКЛЮ -ШОЩЕЕ ИЛИ соединен с информационным входом формирователя сигнатур.

. По сигналу Начальная установка триггеры 4 и 12 сбрасываются в нулевое состояние. По приходу высокого уровня сигнала на входе 8 значения сигналов с информационных входов 9 поступают через элементы И 1 на .сумматоры 10 по модулю два. При этом по фронту сигнала на входе 7 эта двоичная информация записывается в D- триггеры 4 и 12 и тем самым осуществляется формирование,результирующей сигнатуры.

После подачи всех N тестовых наборов на входы проверяемой цифровой системы (т.е. поступления N импульсов на вход 7 устройства) снимается сигнал с входа 8, запрещая прохождение анализируемой тестовой информации через элементы И 1. Затем вьшолняется подача еще Г 2 импульсов на вход 7, где г - разрядность сигнатуры, п - число информационных входов устройства 1 - Г - ближайшее целое, не меньшее -

г

Полученная сигнатура в точности соответствует состоянию известного четырехразрядного сигнатурного анализатора после сжатия информации с выводов проверяемого цифрового узла последовательным перебором групп по четыре вывода для каждой входной тестовой комбинации, т.е. для каждого теста сжимаются вектора (х х х х ,х,). (x,x,x,xj, (х„х,„ х .. х ..) и

го теста сжимаю ,х,). (x,x,x,xj

(х,,,х,4Х,5Х

16

):

°

Таким образом, достоверность контроля определяется выражением 1-2, при этом взаимное расположение позиций символов, искажение которых может привести к пропуску ошибки, носит случайный характер.

°

рмула изобретения Сигнатурный анализатор, содержа- цгнй формирователь сигнатур, блок индикации, 1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, где 1

(-2).

п - число

25

30

информационных входов анализатора, г - разрядность сигнатуры, 1 D-триг- геров, выходы формирователя сигнатур соединен с входами блока индикации, вьгходы i-x триггеров соединены с первыми входами i-x Э 1ементов ИСКЛЮЧАКЬ- D1EE ШШ, где i 1,1, выходы j-x элементов ИСКЛЮЧАЮЩЕЕ ИЛИ со ёдинены с D-вхо ами (j-l)-x триггеров, где j 2,1, тактовые входы D-триггеров |И формирователя сигнатур объединены и образуют тактовый вход анализатора, отличающийся тем, 0 целью повьщ ения быстродействия, он дополнительно содержит п элементов И и блок пространственного сжатия информации, причем первые входы элементов И являются информа- 5 ционными входами анализатора, вторые . входы элементов И объединены и образуют вход разрешения анализатора, выходы элементов И соединены с соот- ветствуюодами входами блока лростран- Q ственного сжатия информации, i-e выходы которого соединены с вторыми входами t-x.элементов ИСКЛЮЧАКЦЕЕ ИЛИ, (1+1)-й выход блока пространственного сжатия информации соединен 5 D-входом 1-го триггера, выход первого элемента ИСКЛЮ -ШОЩЕЕ ИЛИ соединен с информационным входом формирователя сигнатур.

| Ргос | |||

| Int | |||

| Test Conf | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

| Устройство для контроля логических элементов | 1983 |

|

SU1182525A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1988-04-25—Подача