Этим завершается обмен устройства управления памятью с памятью коллек- тивного пользования в режиме Запись w

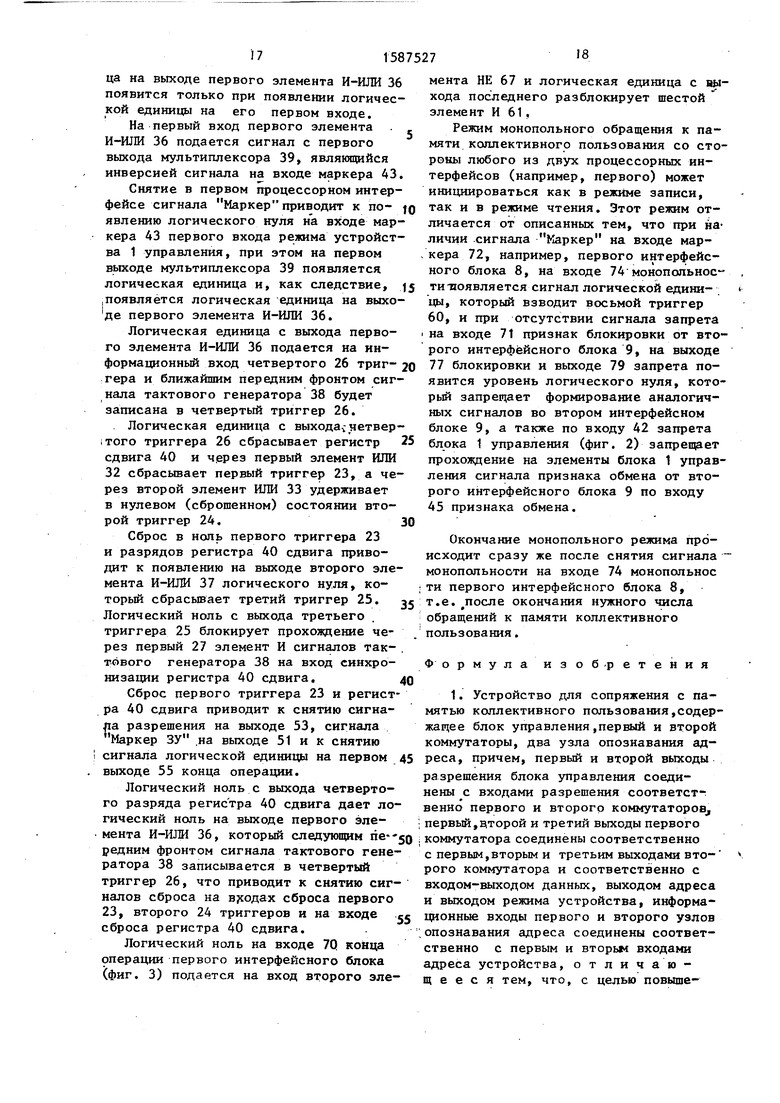

Сброс регистра 40 сдвига (фиг. 2) устройства 1 управления, первого 23 и второго 24 триггеров приводит к появлению на выходе второго 37 элемен- fQ та И-ИЛИ сигнала логического нуля, который сбрасывает третий триггер 25, что в свою очередь блокирует прохождение через первый элемент И 27 ..сигналов тактового генератора 38 на вход jj синхронизации регистра 40 сдвига.

Сигнал логического нуля с выхода первого элемента И-ИЛИ 36, возникающий в результате обнуления четвертот

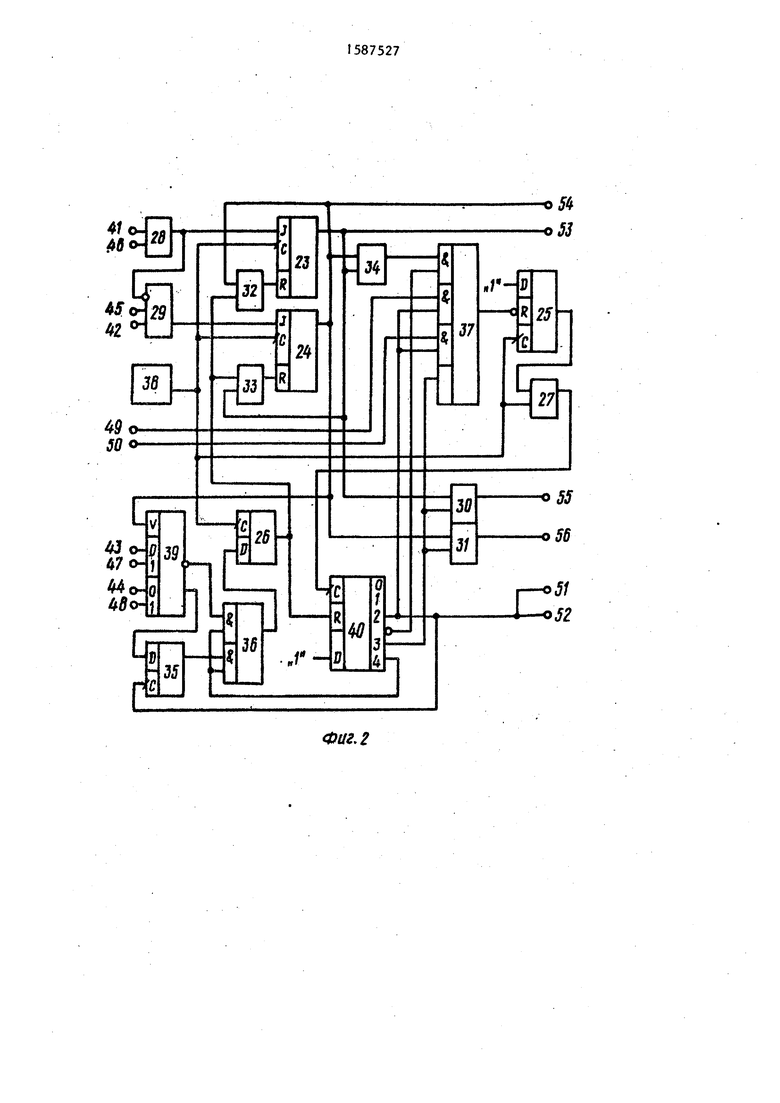

довательно, и на первом входе ше элемента И 61, приводит к появле на выходе последнего сигнала, лог кой единицы.

Передний фронт сигнала с выхо шестого элемента И 61 является с бом записи регистра 57 режима и бом записи первого регистра 10 у |ройства сопряжения с памятью кол тивного пользования (фиг. 1).

В первый регистр 10 записывае адрес с входа 15 адреса и сигнал Чтение с входа 16 режима перво процессорного интерфейса.

В нулевой разряд регистра 57 р

го разряда регистра 40 сдвига, следу- JQ первого интерфейсного блока 8

(фиг. 3) записьюается логическая ница, а в первый разряд - логиче ноль сигнала Чтение с входа 73 си первого интерфейсного блока 8

ющим передним фронтом сигнала тактового генератора будет записан в четвёртый триггер 26.

Записью нуля в четвертый 26 триггер снимается сигнал сброса на пер- 25 вых входах первого 32 и второго 33 элементов ИЛИ, а следовательно, и на выходах сброса первого 23 и второго. 24 триггеров и снимается сигнал сбро- :са на входе сброса регистра 40 сдвига .30 i Снятие сигнала логической единицы на входе конца операции 70 первого интерфейсного блока 8 (фиг. 3) снимает сигналы сброса на входах сброса шестого 58 триггера и регистра 57 ре- жима и через второй элемент НЕ 67 разблокирует шестой элемент И 61.

Таким образом, все элементы уст(фиг. 3) записьюается логическая единица, а в первый разряд - логический ноль сигнала Чтение с входа 73 запи си первого интерфейсного блока 8.

Логический ноль сигнала Чтение на первом входе третьего элемента И-ИЛИ 62 исключает псЛвление сигнала высокого уровня на выходе последнего при приходе на третий его вход сигнал логической единицы с выхода шестого элемента И 61.

Логический ноль с выхода третьего элемента И-ИЛИ 62 блокирует коммутатор 68.

Низкий уровень сигнала Чтение н входе первого элемента НЕ 66 обеспечивает на его выходе уровень логической единицы, которьй подается на второй вход элемента И 65. При прихоройства 1 управления и первого интер- Q де на первьй вход элемента И 65 сигфейсноро блока 8 приводятся в исходное состояние и устройство управле- ния памятью готово к дальнейшей рабом те.

В режиме Чтение данных из памяти дз коллективного пользования на входе 15 адреса процессорного интерфейса, например первого, выставляется адрес считьюаемой ячейки памяти, а на входе

режима 16 - сигнал Чтение , являющийся инрерсйей сигнала Запись, и сигнал Маркер.

После распознавания адреса памяти коллективного пользования логическая единица с-выхода первого узла опозна вания адреса подается на вход 69 nep-v вого интерфейсного блока 8 (фиг. 3) и далее на втор.ой вход шестого Элемента И 61 .

50

55

нала логической единицы с выхода шес того элемента И 61, на выходе третьего элемента И-НЕ 65 появляется логический ноль, подающийся на вход установки в единицу седьмого триггера 59

Седьмой триггер 59 устанавливается в единичное состояние, так как на его входе, установки в ноль присутствует логическая единица сигнала Маркер с входа маркера 72.

Логическая единица с выхода седьмо го 59 триггера поступает на четвертьй вход третьего элемента И-ШШ 62 и на выход 75 разрешения первого интерфейс ного блока: 8,

Сигнал высокого уровня с выхода 75 разрешения первого интерфейсного блока 8 (фиг. 1) открьюает третий коммутатор 12, разрешая прохождение данных

довательно, и на первом входе шестого элемента И 61, приводит к появлению на выходе последнего сигнала, логической единицы.

Передний фронт сигнала с выхода шестого элемента И 61 является стробом записи регистра 57 режима и стробом записи первого регистра 10 уст- |ройства сопряжения с памятью коллективного пользования (фиг. 1).

В первый регистр 10 записывается адрес с входа 15 адреса и сигнал Чтение с входа 16 режима первого процессорного интерфейса.

В нулевой разряд регистра 57 режи первого интерфейсного блока 8

(фиг. 3) записьюается логическая единица, а в первый разряд - логический ноль сигнала Чтение с входа 73 записи первого интерфейсного блока 8.

Логический ноль сигнала Чтение на первом входе третьего элемента И-ИЛИ 62 исключает псЛвление сигнала высокого уровня на выходе последнего при приходе на третий его вход сигнал логической единицы с выхода шестого элемента И 61.

Логический ноль с выхода третьего элемента И-ИЛИ 62 блокирует коммутатор 68.

Низкий уровень сигнала Чтение н входе первого элемента НЕ 66 обеспечивает на его выходе уровень логической единицы, которьй подается на второй вход элемента И 65. При приходе на первьй вход элемента И 65 сиг

нала логической единицы с выхода шес того элемента И 61, на выходе третьего элемента И-НЕ 65 появляется логический ноль, подающийся на вход установки в единицу седьмого триггера 59.

Седьмой триггер 59 устанавливается в единичное состояние, так как на его входе, установки в ноль присутствует логическая единица сигнала Маркер с входа маркера 72.

Логическая единица с выхода седьмого 59 триггера поступает на четвертьй вход третьего элемента И-ШШ 62 и на выход 75 разрешения первого интерфейсного блока: 8,

Сигнал высокого уровня с выхода 75 разрешения первого интерфейсного блока 8 (фиг. 1) открьюает третий коммутатор 12, разрешая прохождение данных

131587527

с входа-выхода 20 данных устройства

для подключения памяти на вход-выход 14 данных первого процессорного интерфейса.

На входах блока 1 управления (фиг. 2) устанавливаются следугацие сигналы: сигнал логической единицы на входе 41 признака обмена; сигнал логической единицы на входе 43 маркера, |Q подающийся с выхода маркера 80 первого интерфейсного блока (фиг. 3);- сигнал логического нуля на входе 44 записи, подающийся с выхода 82 записи первого интерфейсного блока 8. 15

На первом входе второго элемента И 28 устройства 1 управления (фиг. 2) присутствует логическая единица с входа 41 признака обмена, на втором входе - логическая единица, обуслов- 20 ленная отсутствием сигнала Запрет на входе 46 запрета с выхода 79 запрета второго интерфейсного блока 9 (фиг. 3) .с..

Сигнал логической единицы с выхода 25 второго элемента И 28 ближайшим передним фронтом сигнала тактового генератора 38 взводит первый триггер 23.

Логическая единица с выхода первого триггера 23 через первый выход 53 30 разрешения открьгоает первый коммутатор 2 (фиг. 1) и разрешает прохождение на выход 21 адреса, записанного в первом регистре 10.

Логическая единица на выходе перво го триггера 23 устройства 1 управления (фиг. 2) через второй элемент ИЛИ 33 удерживает в нулевом состоянии второй триггер 24, г( через третий элемент ИЛИ 34 подается на седьмой вход второго элемента И-ШШ 37, на шестом входе которого присутствует логическая единица .с инверсного выхода второго разряда регистра 40 сдвига. Это вляется условием появления на выходе второго элемента И-ИЛИ 37 логичесСигнал логической единицы с прямо го выхода второго разряда регистра 4 сдвига подается на первый выход 51 маркера блока 1 управления и далее через открытый первый коммутатор 2 ; (фиг. 1) подается на 22 режима устройства и является сигналом Маркой единицы, которая подается на

вход сброса третьего триггера 25 и

разрешает запись в последний логичес- п кер .

кой единицы передним (условно вторым) Таким образом осуществляется зафронтом сигнала тактового генерато- держка сигнала Маркер ЗУ на выходе

14

0

5

0

5

0

5

Передними фронтами сигналов тактог вого генератора 38, проходящих через первый элемент И 27 на вход синхронизации регистра 40 сдвига, осуществляется запись и сдвиг логической единицы в первый, а затем и во второй разряд регистра 40 сдвига.

Сдвиг логической единицы во второй разряд регистра 40 сдвига приводит к появлению логического нуля на инверс - ном выходе второго разряда регистра 40 сдвига. Логический ноль с инверсного выхода второго разряда регистра 40 бдвига подается на шестой вход второго элемента И-ИЛИ 37, что приводит к появлению на выходе последнего лог гического нуля, который подается на вход сброса третьего триггера 25 и сбрасывает его. Логический ноль с выхода третьего триггера 25 блокирует прохождение через первый элемент И 27 сигналов тактового генератора 38 на вход синхронизации регистра 40 га.

Таким образом прекращается дапь нейший сдвиг логической единицы в третий и четвертый разряды регистра 40 сдвига.

Передним фронтом сигнала логической единицы с прямого выхода второго разряда регистра 40 сдвига в пятый триггер 35 записывается логический ноль сигнала Чтение с второго выхода мультиплексора 39.

Причем на второй выход мультиплексора 39 сигнал Чтение низкого уровня проходит с входа 44 записи, так как на управляющем входе мультиплексора 39 присутствует логический ноль с выхода второго триггера 24.

Сигнал логической единицы с прямого выхода второго разряда регистра 40 сдвига подается на первый выход 51 маркера блока 1 управления и далее через открытый первый коммутатор 2 ; (фиг. 1) подается на 22 режима устройства и является сигналом Мар

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Устройство для ввода-вывода информации | 1980 |

|

SU955008A1 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для отсчета времени | 1990 |

|

SU1817085A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании мультипроцессорных систем с общей памятью. Целью изобретения является повышение быстродействия при обращении к памяти коллективного пользования за счет совмещения во времени процесса записи в одном из процессорных интерфейсов с процессом записи или чтения в другом процессорном интерфейсе. Указанная цель достигается тем, что устройство содержит блок 1 управления, первый и второй коммутаторы 2 и 3, первый и второй узлы 4 и 5 опознавания адреса, первую и вторую адресные вставки 6 и 7, первый и второй интерфейсные блоки 8 и 9, первый и второй регистры 10 и 11, третий и четвертый коммутаторы 12 и 13. 2 з.п. ф-лы, 3 ил.

ра 38.

Логическая единица с выхода третьего триггера 25 подается на второй вход первого элемента И 27, разрешая прохождение через последний сигналов тактового генератора 38 на вход син- .хронизации регистра 40 сдвига.

22 режима относительно сигналов на выходе 21 адреса устройства.

После того как на выходе 21 адреса появляется адрес, на выходе 22 режима появляется сигнал Чтение и - сигнал Маркер ЗУ, память выставляет данные на входе-выходе 20 данных и

15

сигнал Готовность ЗУ. Данные с входа-выхода 20 данных устройства через открытый коммутатор 12 проходят на вход-выход 14 данных первого jipo- цессорного интерфейса.

Сигнал Готовность ЗУ подается на первый.вход 49 готовности блока 1 уп- |равления (фиг; 2).

де 81 первого интерфейсного блока 8 и к снятию логической единицы на ин формационном входе шестого тригге ра 58.

.Логическая единица с входа 70 конца опе зации подается на второй вход третьего элемента И-ИЛИ 62, на четвертом входе которого присутствует

Логическая единица Готовность ЗУ ю логическая едшица с выхода седьмого

триггера 59. Логические единицы на втором и четвертом входах третьего элемента И-ИЛИ 62 являются условием появления на его выходе сигнала логической единицы, который подается на вход разрешения пятого коммутатора 68 и разрешает прохождение JJOгичecкoй единицы с информационного входа последнего на выход 78 готовности первого интерфейсного блока 8.

.

ic первого входа 49 готовности подается на четвертый вход второго элемента И-ШШ 37, на третьем входе которого присутствует логическая единица с прямого выхода второго разряда регист ра 40 сдвига. Наличие логических единиц на третьем и четвертом входах второго элемента И-ИЛИ 37 является условием появления на выходе последнего сигнала логической единицы. Логичес- кая единица с выхода второг о элемента И-ИЛИ 37 подается на вход сброса тре- ..тьего триггера 25, разрешая запись в последний логической единицы ближайшим передним фронтом сигнала тактово го генератора 38.

Логическая единица с выхода третьего триггера 25 разрешает прохождение через первый элемент И 27 сигналов тактового генератора 38 на вход синхронизации регистра 40 сдвига.

В регистре 40 сдвига происходит сдвиг логической единицы в третий разряд и сигнал логической единицы с выхода третьего разряда подается на вторые входы четвертого 30 и пятого 31 элементов И, а также на первый вход второго элемента И-ИЛИ.

Причем логическая единица на перв входе второго элемента И-ШШ 37 явля ется условием, подтвер5кдакщем наличие логической единицы на его выходе

На первом входе четвертого элемента И 30 присутствует логическая единица с выхода первого .триггера 23,. поэтому появление на втором входе четвертого элемента И 30 логической единицы с выхода третьего разряда регистра 40 сдвига приводит к появлению на выходе четвертого элемента И 30 сигнала логической единицы, который через первый выход 55 концй опе- рации блока 1 управления подается на вход 70 первого интерфейсного блока 8 (фиг. 3).

Сигнал логической единицы на входе 70 конца операции сбрасывает регистр 57 режима, что приводит к снятию сигнала признака обмена на выхо

логическая едшица с выхода седьмого

5

0

5 0

40

5

45

50

55

триггера 59. Логические единицы на втором и четвертом входах третьего элемента И-ИЛИ 62 являются условием появления на его выходе сигнала логической единицы, который подается на вход разрешения пятого коммутатора 68 и разрешает прохождение JJOгичecкoй единицы с информационного входа последнего на выход 78 готовности первого интерфейсного блока 8.

Сигнал с выхода готовности первого интерфейсного блока 8 (фиг. 1) является сигналом Готовность от устройства сопряжения с памятью коллективного пользования. По сигналу Готовность процессор считывает. данные с входа-выхода 14 данных первого процессорного интерфейса и завершает обмен с памятью коллективного пользования в режиме чтения данных. При этом на входе 15 адреса первого процессорного интерфейса снимается адрес, а на входе 16 режима С1шмается сигнал Маркер.

Логический ноль на входе 72 маркера первого интерфейсного блока 8 (фиг. 3) устанавливает в ноль седьмой 59 триггер, что приводит к появлению логического нуля на выходе 75 разрешения и на четвертом входе третьего элемента И-ИЛИ 62 блокирует пятый коммутатор 68, что приводит к снятию сигнала Готовность на выходе 78.

Таким образом, на входе-выходе 14 данных (фиг. 1) первого процессорного интерфейса снимаются данные (закрывается третий коммутатор 12) и снимается Готовность.

Сдвиг логической единицы в четвертый разряд регистра 40 сдвига блока управления (фиг. 2) приводит к появлению сигн ала логической единицы с вы- кода четвертого разряда регистра 40 сдвига на четвертом и третьем входах первого элемента И-ИЛИ 36.

На втором входе первого элемента И-ИЛИ 36 присутствует логический ноль сигнала Чтение, записанньм в пятый триггер 35, поэтому логическая единица на выходе первого элемента И-ИЛИ 36 появится только при появлении логической единицы на его первом входе.

На первый вход первого элемента И-Ш1И 36 подается сигнал с первого выхода мультиплексора 39, являющийся инверсией сигнала на входе маркера A3.

Снятие в первом процессорном интерфейсе сигнала Маркер приводит к по- jg явлению логического нуля на входе маркера 43 первого входа режима устройства 1 управления, при этом на первом выходе мультиплексора 39 появляется логическая единица и, как следствие, 15 Iпоявляется логическая единица на выхо- де первого элемента И-ИЛИ 36.

Логическая единица с выхода первого элемента И-ИЛИ 36 подается на информационный вход четвертого 26 триг- 20 гера и ближайшим передним фронтом сигнала тактового генератора 38 будет записана в четверть триггер 26.

Логическая единица с выхода четвер- 1ТОГО триггера 26 сбрасывает регистр 25 сдвига 40 и через первый элемент ИЛИ 32 сбрасывает первый триггер 23, а через второй элемент ИЛИ 33 удерживает в нулевом (сброшенном) состоянии второй триггер 24.30

Сброс в ноль первого триггера 23 и разрядов регистра 40 сдвига приводит к появлению на выходе второго элемента И-ИЛИ 37 логического нуля, который сбрасьюает третий триггер 25. эг Логический ноль с выхода третьего триггера 25 блокирует прохоядение через первый 27 элемент И сигналов так- . тового генератора 38 на вход синхронизации регистра 40 сдвига.40

Сброс первого триггера 23 и регистра 40 сдвига приводит к снятию сигнала разрешения на выходе 53, сигнала Маркер ЗУ .на выходе 51 и к снятию сигнала логической единицы на первом 45 выходе 55 конца операции.

Логический ноль с выхода четвертого разряда регистра 40 сдвига дает логический ноль на выходе первого элемента И-ИЛИ 36, который следующим rie -jO редним фронтом сигнала тактового генератора 38 записывается в четвертый триггер 26, что приводит к снятию сигналов сброса на врсодах сброса первого 23, второго 24 триггеров и на входе .« сброса регистра 40 сдвига.

Логический ноль на входе 7Q конца операции первого интерфейсного блока (фиг. 3) подается на вход второго элемента НЕ 67 и логическая единица с выхода последнего разблокирует шестой элемент И 61,

Режим монопольного обращения к памяти коллективного пользования со стороны любого из двух процессорных интерфейсов (например, первого) может инициироваться как в режиме записи, так и в режиме чтения. Этот режим отличается от описанных тем, что при наличии .сигнала Маркер на входе мар- кера 72, например, первого интерфейсного блока 8, на входе 74 монопольное- ти появляется сигнал логической едини- цы, который взводит восьмой триггер 60, и при отсутствии сигнала запрета

на входе 71 признак блокировки от второго интерфейсного блока 9, на выходе 77 блокировки и выходе 79 запрета появится уровень логического нуля, который запрещает формирование аналогичных сигналов во втором интерфейсном блоке 9, а также по входу 42 запрета блока 1 управления (фиг. 2) запрещает прохождение на элементы блока 1 управления сигнала признака обмена от второго интерфейсного блока 9 по входу 45 признака обмена.

Окончание монопольного режима происходит сразу же после снятия сигнала монопольнооти на входе 74 монопольное ти первого интерфейсного блока 8, т.е.после окончания нужного числа обращений к памяти коллективного пользования.

Формула изоб.ретения

ния быстродействия при обращении к па- , пяти коллективного пользования за счет совмещения во времени процесса : записки в одном из процессорных интер- фейсов с процессом записи или чтения в другом процессорном интерфейсе, в него введены два интерфейсных блока, третий и четвертый коммутаторы и два регистра, причем информационные входы fQ третьего и четвертого коммутаторов соединены с третьим входом-выходом . данные устройства, выходы третьего и четвертого коммутаторов соединены соответственно с первым и вторым входом- з выходом данных устройства, входы разрешения третьего и четвертого коммута - торов соединены с выходами разрешения соответственно первого и второго интерфейсных блоков, первый, второй и 20 .третий информационные входы первого регистра соединены соответственно с первым входом-выходом данных устройства, с первым входом адреса устройства и с nepBbiM входом режима устройства, 25 первый, второй и третий информацион-. ные входы второго регистра соединены соответственно с вторым входом-выходом данных устройства, с вторым входом адреса устройства и с вторым входом ре-30 жима устройства, первый, второй и Tjpe- тий выходы первого регистра соединены соответственно с первым, вторым и третьим информационными входа первого коммутатора, первый, второй и третий s выходы второго регистра соединены со-, ответственно с первым, вторым и тре- ,тьим информационными входами второго коммутатора, входы записи первого и ) второго регистров соединены с выходами до записи соответственно первого и вто- рого интерфейсных блоков, входы опознавания адреса первого и второго интерфейсных блоков соединены с выходами соответственно первого и второго 45 узла опознавания адреса, входы признака блокировки первого и второго интерфейсных блоков соединены с выходам блокировки соответственно второго и первого интерфейсных: йлоков, входы JQ режима первого и второго интерфейсных блоков соединены соответственно с первым и вторым входами режима устройства, выходы режима первого и второго интерфейсных блоков соединены,соответ сс ственно с первым и вторым входами режима блока управления, первый и второй выходы конца операции которого соединены с одноименными входами соответственно первого и второго интерфейсных блокоб, выходы готовности первого и второго интерфейсных блоков являются соответственно первым и вторым выходами готовности устройства, первый и второй выходы маркера блока управления соединены с третьими ин формационными входами соответственно первого и второго коммутаторов, первый и вто1$ой входы готовности блока управления соединены с третьими информационными выходами соответственно первого и второго коммутаторов.

2о Устройство по п. 1, отлича- ю щ е е с я тем, что блок управления содержит тактовый генератор, мультиплексор, регистр сдвига, пять триггеров, пять элементов И, три элемента ИЛИ и два элемента И-ИШ причем выход тактового генератора соединен с входами синхронизации первого, второго, третьего и четвертого триггеров и с первьш входом первого элемента И, второй вход которого соединен с выходом первого триггера,выход первого элемента И соединен с входом синхронизации регистра сдвига, вход сброса которого соединен с первыми входами первого и второго элементов ИЛИ и с выходом второго триггера, информационньй вход которого соединен с выходом первого элемента И-ИЛИ, первые входы первой и второй групп входов которого соединетт ны с четвертым разрядом выхода регистра сдвига, третий разряд выхода которого соединен с первыми входами второго и третьего элементов И и входом второго элемента И-ИЛИ, первые входы первой и второй групп входов которого соединены с первыми и вторыми выходами маркера блока и с выходом рого разряда регистра сдвига, инверс- ньй выход второго разряда которого соединен с первым входом третьей, группы входов второго элемента И-ИЛИ, вы- ход которого соединен с входом сброса первого триггера, вторые входы первой, второй и третьей группы входов второго элемента И-ИЛИ соединены соответственно, с первым входом готовности блока, с вторым входом готовнос- Ти блока, с выходом третьего элемента ЩИ, выход третьего триггера соединен b цервым входом третьего элемента Ш1К, с вторым входом второго элемента-ИЛИ, с вторым входом второго элемента И и с первым выходом разрешения блока, ВЫХОД четвертого триггера соединен

21

первого элемента ИЛИ третьего элемента ИЛИ третьего элемента И,

с вторым входом с вторым входом с вторым входом

с управляющим входом мультиплексора и с вторым выходом разрешения блока, выходы второго и третьего элементов И являются соответственно первым и вторым выходами конца операции блока, выходы первого и второго элементов ИЛИ соединены с входами сброса соответственно третьего и четвертого триггеров, информационные входы третьего и четвертого триггеров соединены с вы ходами соответственно четвертого и пятого элементов И, первые входы четвертого и пятого элементов И соединены с соответствующими разрядами соответственно первого и второго входов режима блока, вторые входы четвертого и пятого элемента И соединены с соответствующими разрядами соответственна второго и первого входов режима блока, третий инверсный вход пятого элемента И соединен с выходом четвертого элемента И, первые входы первой и второй групп входов мультиплексора соединены с соответствующими разрядами первого входа режима блока, вторые входы первой и второй групп входов мультиплексора.соединены с соответст- вунщими разрядами второго входа режима блока, первый инверсный выход мультиплексора соединен с вторым входом первой группы входов первого элемента И-ИЛИ, второй вход второй группы входов которого соединен с выходом пятого триггера, информационный вход которого соединен с вторым выходом мультиплексора, вход синхронизации пятого триггера соединен с вторым разрядом выхода регистра сдвига.

, И,

10

15

20

25

И таае- ьзрjOп58752722

записи блока, выход второго элемента. И соединен с входом установки первого триггера, вход сброса которого соединен с вторым входом второго элемента И и с соответствующим разрядом второго входа режима..блока, выход первого триггера соединен с первым входом четвертого элемента И, второй вход кото-. рого является входом признака блокировки блока, выход четвертого элемента И соединен с выходом блокировки . блока и с соответствукяцим разрядом выхода режима блока, второй вход пер- вой группы входов элемента И-ИЛИ соединен с входом первого элемента НЕ, с первым разрядом информационного входа регистра и с соответствующим разрядом второго входа режима блока, первый вход второй группы входов элемента И-ИЛИ соединен с входами сброса второго триггера и регистра, с входом второго элемента НЕ и с входом конца операции блока, второй вход второй группы входов элемента И-ИЛИ соединен с выходом третьего триггера и с выходом разрешения блока, выход элемента И-ИЛИ соединен с управляющим входом коммутатора, выход которого является выходом готовности блока, вход установки третьего триггера соединен с выходом третьего элемента И, второй вход которого соединен с выходом первого элемента НЕ, вход сброса третьего триггера соединен с входом

30

35

40

45

синхронизации второго триггера, с пер- вым входом первого элемента И, с соот- ветствуюощм разрядом второго входа режима блока и с соответствукяцим разрядом выхода режима, второй вход первого элемента И является входом опознавания адреса блока, третий вход первого элемента И соединен с выходом второго элемента НЕ, четвертый вход первого элемента И соединен с инверсным выходом второго триггера, информационный вход которого соединен с вторым разрядом выхода регистра и с соответствующим разрядом выхода режима блока, первый разряд выхода регистра соединен с соответствующим разрядом выхода режима блока.

Фиг. 2

Фаг.З

| Предохранитель от вывинчивания электрических ламп накаливания | 1924 |

|

SU1304A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1990-08-23—Публикация

1988-07-05—Подача