ел

о

4. J

со

00

Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи и переработки цифровой информации позволяет повысить быстродействие. Устройство содержит генератор 1 тактовых импульсов, 2P-канальный преобразователь 2 параллельного кода в последовательность импульсов и блоки 3 подсчета единиц. Благодаря введению узла 4 суммирования и контроля и соответствующим соединениям в устройстве обеспечивается распараллеливание процесса преобразования. 9 з.п. ф-лы, 6 ил.

w 5.1 5.(р+1) 52 5(р+2)

Риг /

5р 52р

Изобретение относится к автомати- |е и вычислительной технике и может Зыть использовано при. создании сис- пем передачи и переработки цифровой -информации.

Цель изобретения - повышение быстродействия.

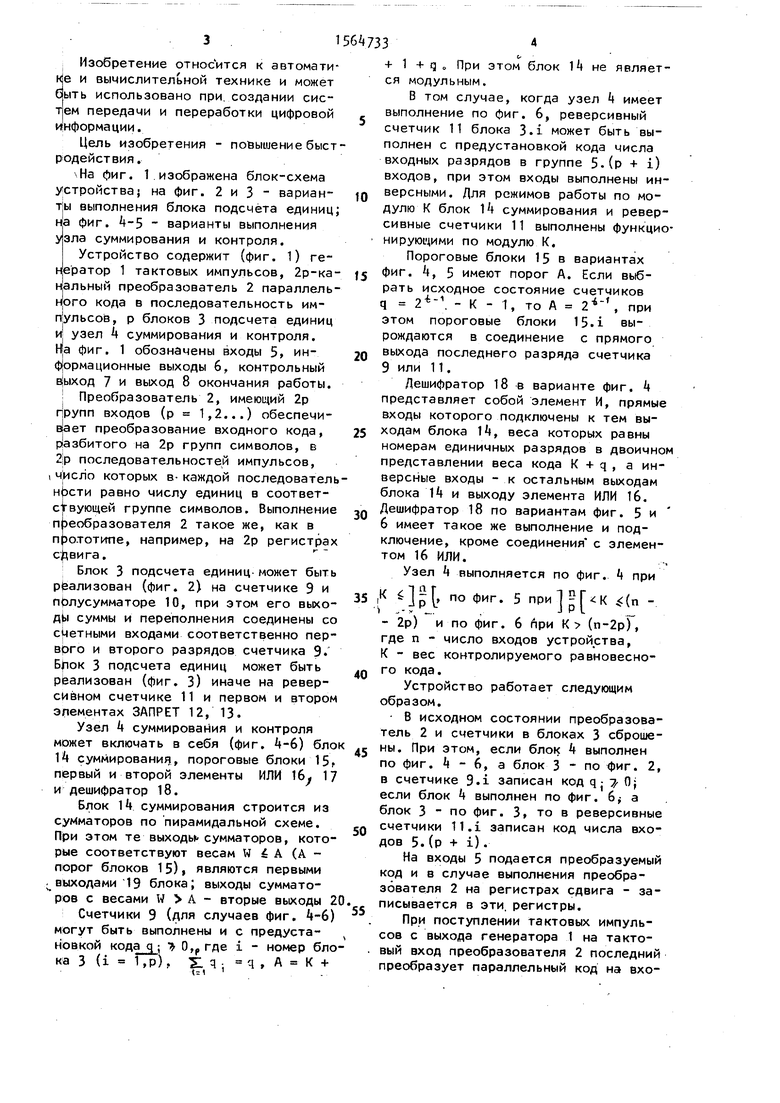

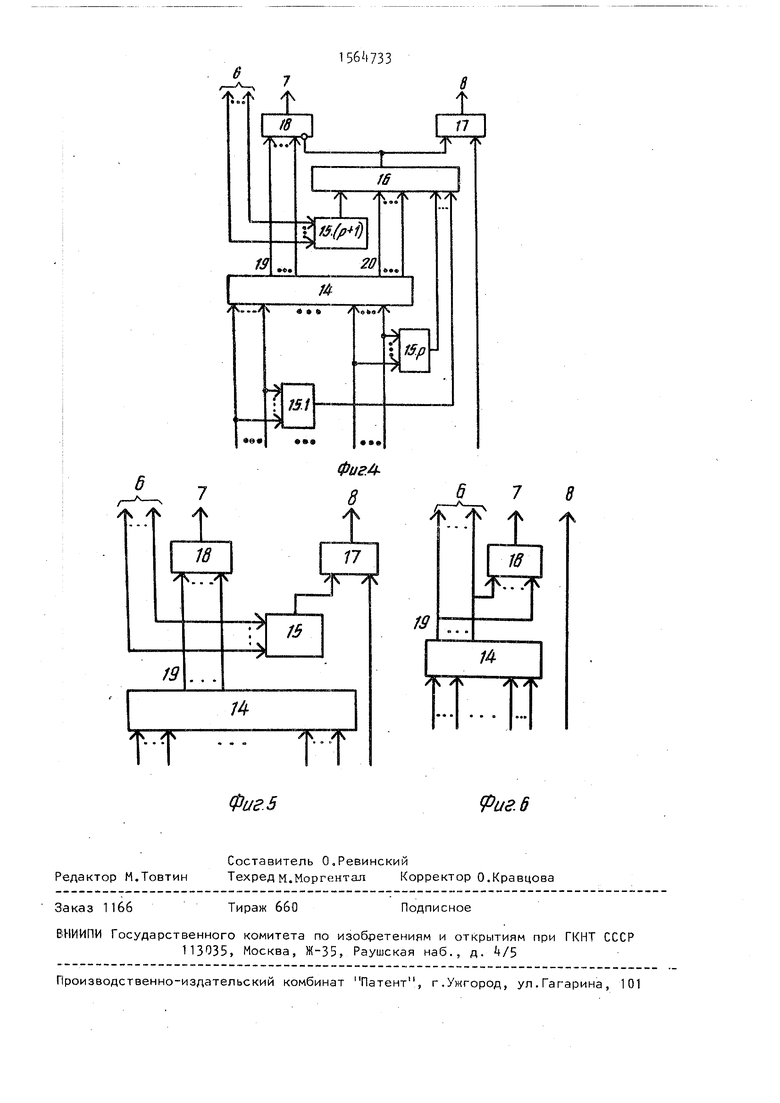

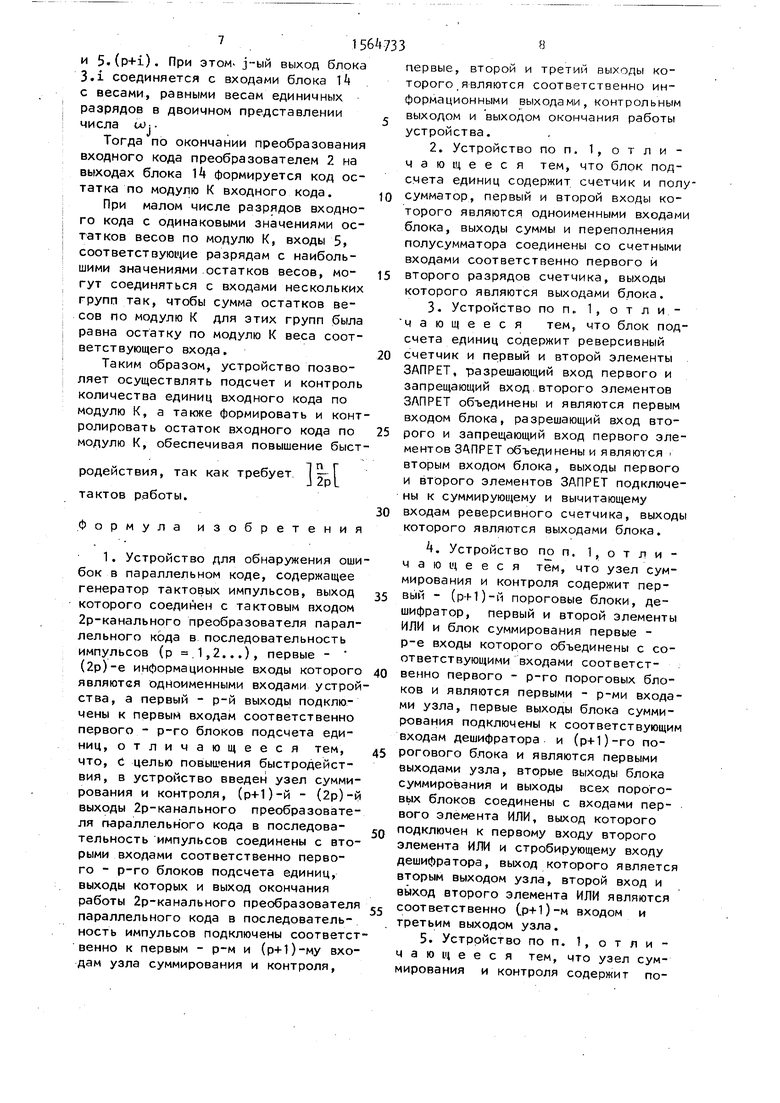

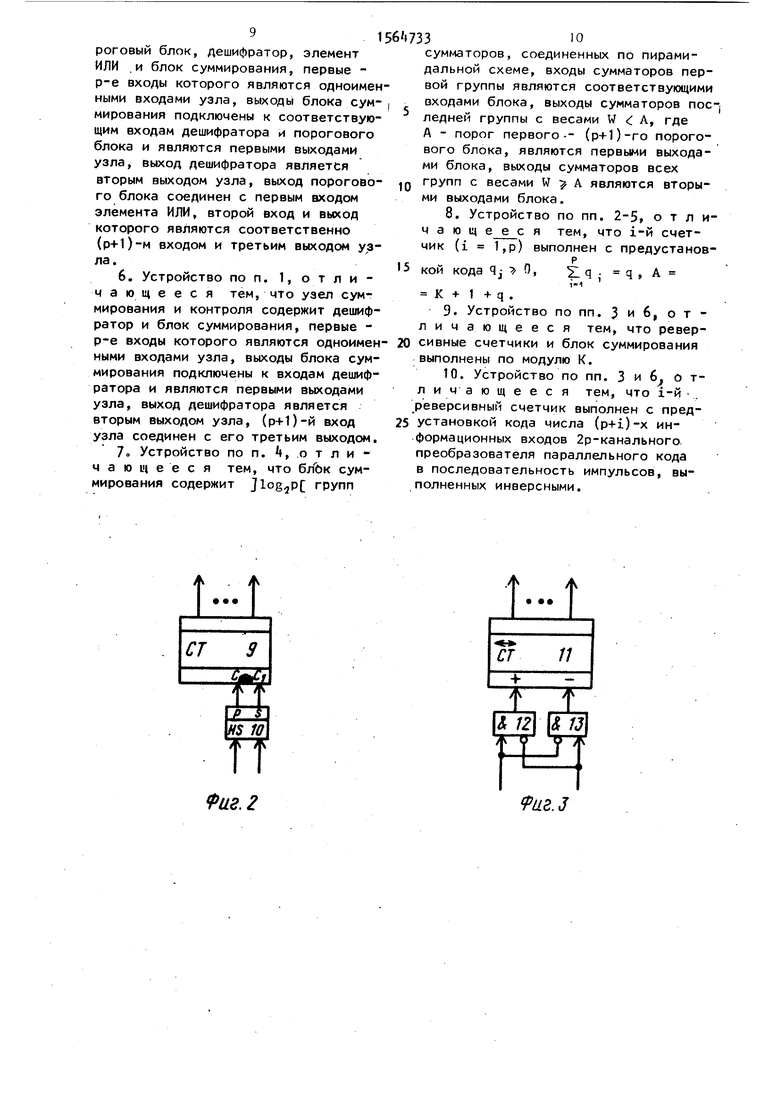

На фиг. 1 изображена блок-схема устройства} на фиг. 2 и 3 варианту выполнения блока подсчета единиц; на фиг. 4-5 - варианты выполнения узла суммирования и контроля.

Устройство содержит (фиг. 1) генератор 1 тактовых импульсов, 2р-канальный преобразователь 2 параллельного кода в последовательность импульсов, р блоков 3 подсчета единиц и узел 4 суммирования и контроля. фиг. 1 обозначены входы 5 информационные выходы 6, контрольный йыход 7 и выход 8 окончания работы.

Преобразователь 2, имеющий 2р групп входов (р 1,2...) обеспечи- преобразование входного кода, разбитого на 2р групп символов, в 2р последовательностей импульсов, i число которых в- каждой последователь- н|эсти равно числу единиц в соответ- с гвующей группе символов. Выполнение преобразователя 2 такое же, как в прототипе, например, на 2р регистрах сдвига.

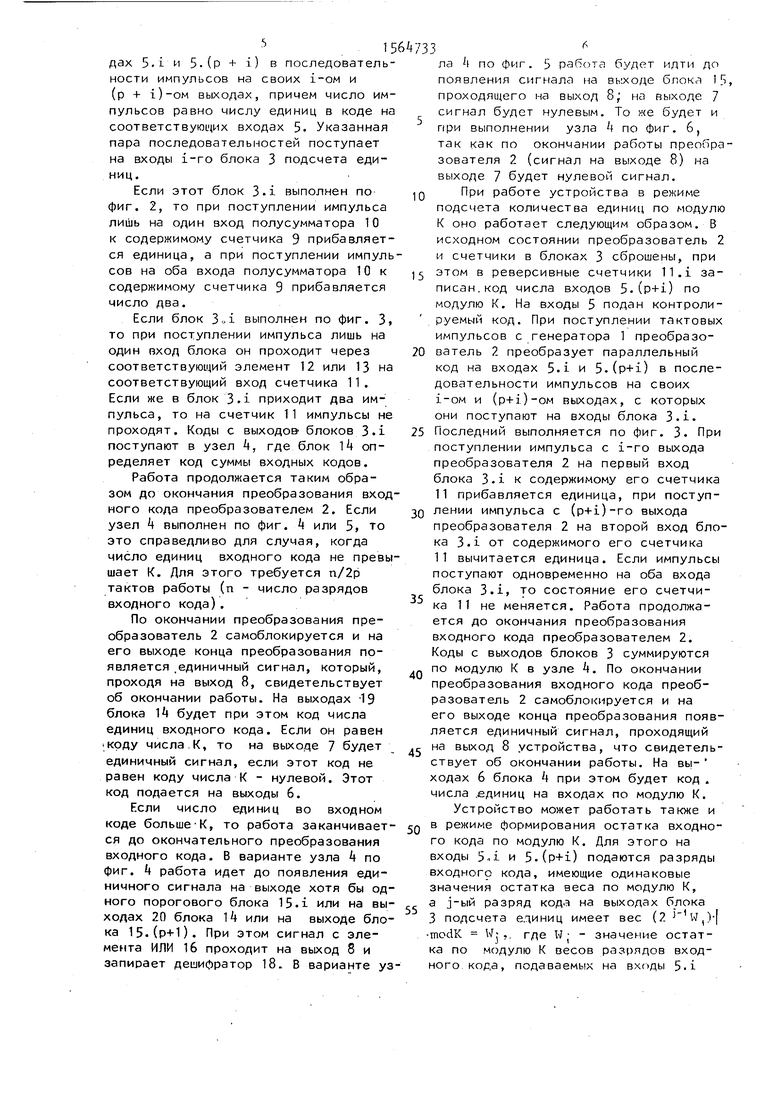

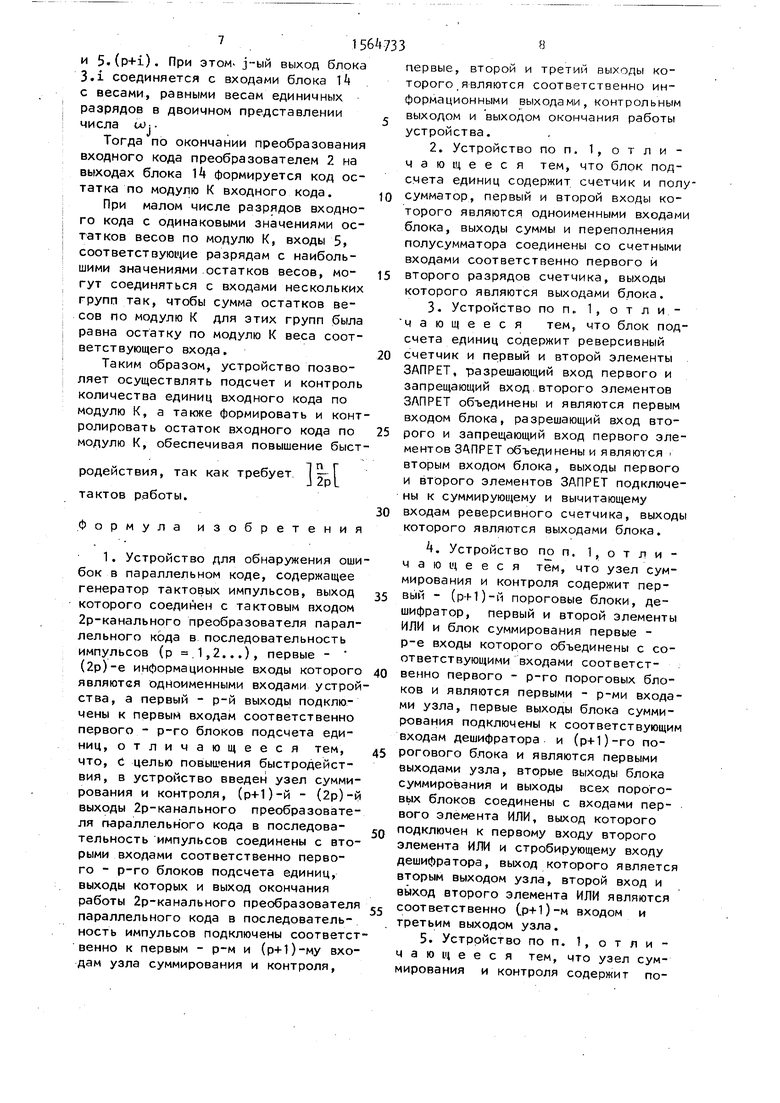

Блок 3 подсчета единиц-может быть реализован (фиг. 2) на счетчике 9 и полусумматоре 10, при этом его выходы суммы и переполнения соединены со сметными входами соответственно пер- врго и второго разрядов счетчика 9. BJIOK 3 подсчета единиц может быть реализован (фиг. 3) иначе на реверсивном счетчике 11 и первом и втором элементах ЗАПРЕТ 12, 13.

Узел 4 суммирования и контроля может включать в себя (фиг. 4-6) блок 14 суммирования, пороговые блоки 15f первый и второй элементы ИЛИ 16 17 и дешифратор 18.

Блок 11 суммирования строится из сумматоров по пирамидальной схеме. При этом те выходы- сумматоров, которые соответствуют весам W Ј А (А - порог блоков 15), являются первыми . выходами 19 блока; выходы сумматоров с весами W А - вторые выходы 20,

Счетчики 9 (для случаев фиг. 4-6) могут быть выполнены и с предуста- s новкой 0,,, где i - номер бло1564/33

н- 1 + q „ При этом блок 14 не является модульным.

В том случае, когда узел 4 имеет выполнение по фиг. 6, реверсивный счетчик 11 блока 3.i может быть выполнен с предустановкой кода числа входных разрядов в группе 5.(р + i) входов, при этом входы выполнены ин- JQ версными. Для режимов работы по модулю К блок 14 суммирования и реверсивные счетчики 11 выполнены функцио- пирующими по модулю К.

Пороговые блоки 15 в вариантах 15 фиг. 4, 5 имеют порог А. Если выбрать исходное состояние счетчиков q . - К - 1, то А , при этом пороговые блоки 15.i вырождаются в соединение с прямого 20 выхода последнего разряда счетчика 9 или 11.

Дешифратор 18 в варианте фиг. 4 представляет собой элемент И, прямые входы которого подключены к тем вы- 25 ходам блока 14, веса которых равны номерам единичных разрядов в двоичном представлении веса кода К + q, а инверсные входы - к остальным выходам блока 14 и выходу элемента ИЛИ 16. ,д Дешифратор 18 по вариантам фиг. 5 и 6 имеет такое же выполнение и подключение, кроме соединения с элементом 16 ИЛИ.

Узел 4 выполняется по фиг. 4 при

35

40

ка 3 (i 1 ,р)..

- qi (

К +

,к р по фиг. 5 при 5 Г К (п - 2р) и по фиг. 6 при К (п-2р), где п - число входов устройства, К - вес контролируемого равновесного кода.

Устройство работает следующим образом.

- В исходном состоянии преобразователь 2 и счетчики в блоках 3 сброше- лг ны. При этом, если блок 4 выполнен по фиг. 4 - 6, а блок 3 по фиг. 2, в счетчике 9.i записан код qj 7/ 0; если блок 4 выполнен по фиг. 6; а блок 3 по фиг. 3 то в реверсивные счетчики 11.1 записан код числа входов 5. (р + i).

На входы 5 подается преобразуемый код и в случае выполнения преобразователя 2 на регистрах сдвига - записывается в эти. регистры.

При поступлении тактовых импульсов с выхода генератора 1 на тактовый вход преобразователя 2 последний преобразует параллельный код на вхо50

55

5

0

,к р по фиг. 5 при 5 Г К (п - 2р) и по фиг. 6 при К (п-2р), где п - число входов устройства, К - вес контролируемого равновесного кода.

Устройство работает следующим образом.

- В исходном состоянии преобразователь 2 и счетчики в блоках 3 сброше- лг ны. При этом, если блок 4 выполнен по фиг. 4 - 6, а блок 3 по фиг. 2, в счетчике 9.i записан код qj 7/ 0; если блок 4 выполнен по фиг. 6; а блок 3 по фиг. 3 то в реверсивные счетчики 11.1 записан код числа входов 5. (р + i).

На входы 5 подается преобразуемый код и в случае выполнения преобразователя 2 на регистрах сдвига - записывается в эти. регистры.

При поступлении тактовых импульсов с выхода генератора 1 на тактовый вход преобразователя 2 последний преобразует параллельный код на вхо0

5

дах 5.1 и 5-(р + i) в последовательности импульсов на своих i-ом и (р + 1)-ом выходах, причем число импульсов равно числу единиц в коде на соответствующих входах 5. Указанная пара последовательностей поступает на входы 1-го блока 3 подсчета единиц.

Если этот блок 3.1 выполнен по фиг. 2, то при поступлении импульса лишь на один вход полусумматора 10 к содержимому счетчика 9 прибавляется единица, а при поступлении импульсов на оба входа полусумматора 10 к содержимому счетчика 9 прибавляется число два.

Если блок 3 выполнен по фиг. 3, то при поступлении импульса лишь на один вход блока он проходит через соответствующий элемент 12 или 13 на соответствующий вход счетчика 11. Если же в блок 3-1 приходит два импульса, то на счетчик 11 импульсы не проходят. Коды с выходов- блоков 3.i поступают в узел k, где блок k определяет код суммы входных кодов.

Работа продолжается таким образом до окончания преобразования входного кода преобразователем 2. Если узел 4 выполнен по фиг. k или 5, то это справедливо для случая, когда число единиц входного кода не превышает К. Для этого требуется п/2р тактов работы (п - число разрядов входного кода).

По окончании преобразования преобразователь 2 самоблокируется и на его выходе конца преобразования появляется .единичный сигнал, который, проходя на выход 8, свидетельствует об окончании работы. На выходах 19 блока Т будет при этом код числа единиц входного кода. Если он равен коду числа.К, то на выходе 7 будет единичный сигнал, если этот код не равен коду числа К - нулевой. Этот код подается на выходы 6.

Если число единиц во входном коде больше-К, то работа заканчивается до окончательного преобразования входного кода. В варианте узла 4 по фиг. Ц работа идет до появления единичного сигнала на выходе хотя бы одного порогового блока 15.i или на выходах 20 блока 14 или на выходе блока 15.(р+1). При этом сигнал с элемента ИЛИ 16 проходит на выход 8 и запирает дешифратор 18. В варианте уз

733

10

15

20

ла k по фиг. 5 работа будет идти до появления сигнала на выходе блока 15, проходящего на выход 8; на выходе 7 сигнал будет нулевым. То we будет и при выполнении узла k по фиг. 6, так как по окончании работы преобразователя 2 (сигнал на выходе 8) на выходе 7 будет нулевой сигнал.

При работе устройства в режиме подсчета количества единиц по модулю К оно работает следующим образом. В исходном состоянии преобразователь 2 и счетчики в блоках 3 сброшены, при этом в реверсивные счетчики 11.1 записан, код числа входов 5-(р+1) по модулю К. На входы 5 подан контролируемый код. При поступлении тактовых импульсов с генератора 1 преобразователь 2 преобразует параллельный код на входах 5.1 и 5.(р+1) в последовательности импульсов на своих i-ом и (р+1)-ом выходах, с которых они поступают на входы блока 3.1- 25 Последний выполняется по фиг. 3. При поступлении импульса с 1-го выхода преобразователя 2 на первый вход блока 3.1 к содержимому его счетчика 11 прибавляется единица, при поступлении импульса с (р+1)-го выхода преобразователя 2 на второй вход блока 3.1 от содержимого его счетчика 11 вычитается единица. Если импульсы поступают одновременно на оба входа блока 3.1, то состояние его счетчика 11 не меняется. Работа продолжается до окончания преобразования входного кода преобразователем 2. Коды с выходов блоков 3 суммируются по модулю К в узле 4. По окончании преобразования входного кода преобразователь 2 самоблокируется и на его выходе конца преобразования появляется единичный сигнал, проходящий на выход 8 устройства, что свидетельствует об окончании работы. На вы- ходах 6 блока А при этом будет код . числа .единиц на входах по модулю К.

Устройство может работать также и в режиме формирования остатка входного кода по модулю К. Для этого на входы 5.1 и 5.(р+1) подаются разряды входного кода, имеющие одинаковые значения остатка веса по модулю К, а j-ый разряд кода на выходах блока 3 подсчета единиц имеет вес (2 J W,)-| modK W-., где W; - значение остатка по модулю К весов разрядов входного кода, подаваемых на входы 5-1

30

35

40

45

50

7156

и 5-(p+i). При этом j-ый выход блока 3.i соединяется с входами блока 1 с весами, равными весам единичных разрядов в двоичном представлении числа W:Тогда по окончании преобразования входного кода преобразователем 2 на выходах блока 14 формируется код остатка по модулю К входного кода.

При малом числе разрядов входного кода с одинаковыми значениями остатков весов по модулю К, входы 5, соответствующие разрядам с наибольшими значениями остатков весов, могут соединяться с входами нескольких групп так, чтобы сумма остатков весов по модулю К для этих групп была равна остатку по модулю К веса соответствующего входа.

Таким образом, устройство позволяет осуществлять подсчет и контроль количества единиц входного кода по модулю К, а также формировать и контролировать остаток входного кода по

модулю К, обеспечивая повышение быстродействия, так как требует I - 1 тактов работы.

Формула изобретения

(2р)-е информационные входы которого 40 венно первого - р-го пороговых бло

являются одноименными входами устройства, а первый - р-й выходы подключены к первым входам соответственно первого - р-го блоков подсчета единиц, отличающееся тем, что, С целью повышения быстродействия, в устройство введен узел суммирования и контроля, (р+1)-й - (2р)-й выходы 2р-канального преобразователя параллельного кода в последовательность импульсов соединены с вторыми входами соответственно первого - р-го блоков подсчета единиц, выходы которых и выход окончания работы 2р-канального преобразователя параллельного кода в последовательность импульсов подключены соответственно к первым - р-м и (р+1)-му входам узла суммирования и контроля,

первые, второй и третий выходы которого .являются соответственно информационными выходами, контрольным выходом и выходом окончания работы устройства.

чающееся тем, что блок подсчета единиц содержит счетчик и полусумматор, первый и второй входы которого являются одноименными входами блока, выходы суммы и переполнения полусумматора соединены со счетными входами соответственно первого и второго разрядов счетчика, выходы которого являются выходами блока.

венно первого - р-го пороговых бло5

0

ков и являются первыми - р-ми входами узла, первые выходы блока суммирования подключены к соответствующим входам дешифратора и (р+1)-го порогового блока и являются первыми выходами узла, вторые выходы блока суммирования и выходы всех пороговых блоков соединены с входами первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ и стробирующему входу дешифратора, выход которого является вторым выходом узла, второй вход и выход второго элемента ИЛИ являются соответственно (р+1)-м входом и третьим выходом узла.

чик (i 1,р) выполнен с предустановр 5 кой кода 4j Я, 5L q - q , А

К + 1 + q .

ными входами узла, выходы блока суммирования подключены к входам дешифратора и являются первыми выходами узла, выход дешифратора является вторым выходом узла, (р+1)-й вход узла соединен с его третьим выходом. 7 о Устройство по п. kf отличаю щ е е с я тем, что блЪк суммирования содержит Jlog/,p групп

, 6 733Ю

сумматоров, соединенных по пирамидальной схеме, входы сумматоров первой группы являются соответствующими входами блока, выходы сумматоров последней группы с весами W А, где А - порог первого-- (р+1)-го порогового блока, являются первыми выходами блока, выходы сумматоров всех групп с весами W А являются вторыми выходами блока.

чик (i 1,р) выполнен с предустановр 5 кой кода 4j Я, 5L q - q , А

выполнены по модулю К.

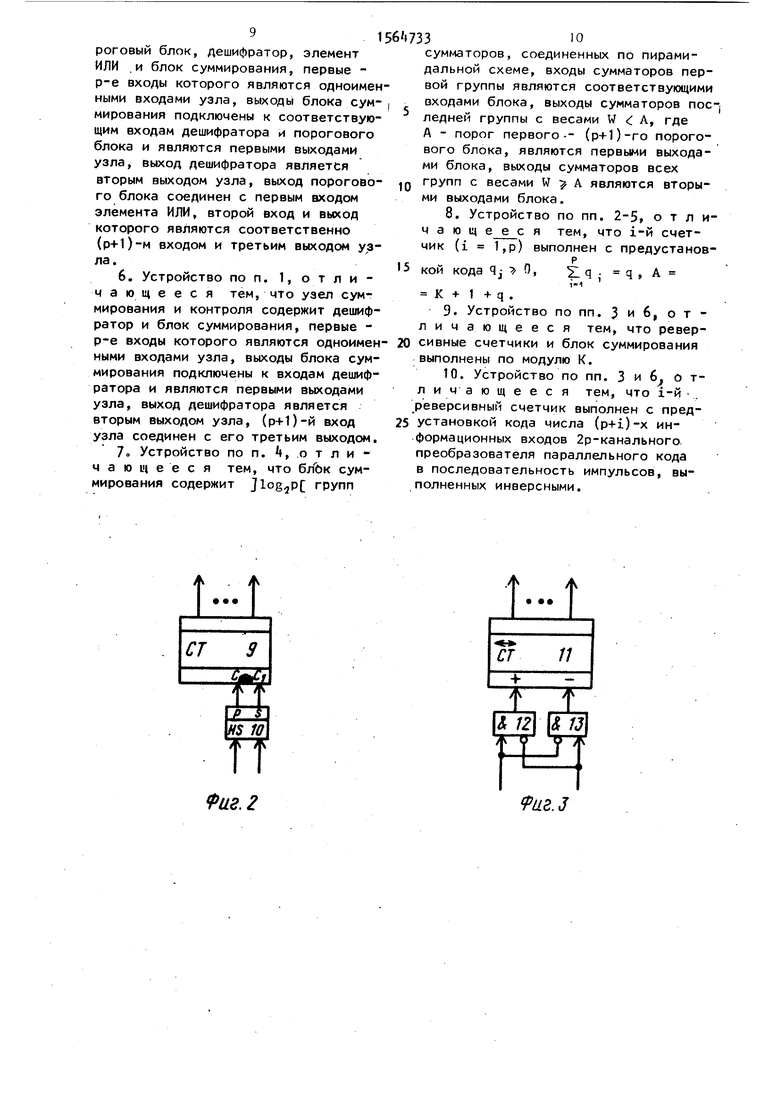

Фиг. J

rr - T-T

Фие.5

Составитель О.Ревинский Редактор М.ТовтинТехред м.МорганталКорректор О.Кравцова

Заказ 1166

Тираж 660

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. k/S

Производственно-издательский комбинат Патент, г.Ужгород, ул.Гагарина, 101

fit/a 6

Подписное

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь кодов | 1985 |

|

SU1285603A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1983 |

|

SU1357960A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-05-15—Публикация

1987-12-08—Подача