Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин с плавающей запятой.

.Целью изобретения является упрощение устройства для суммирования двух чисел с плавающей запятой.

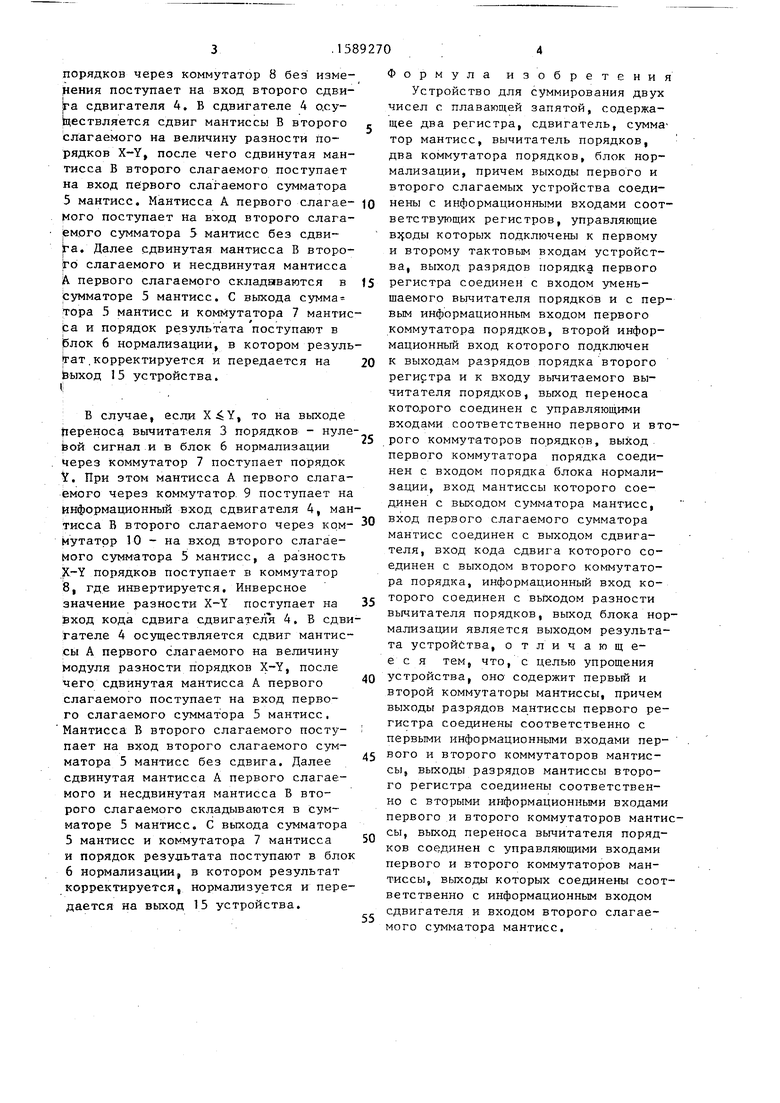

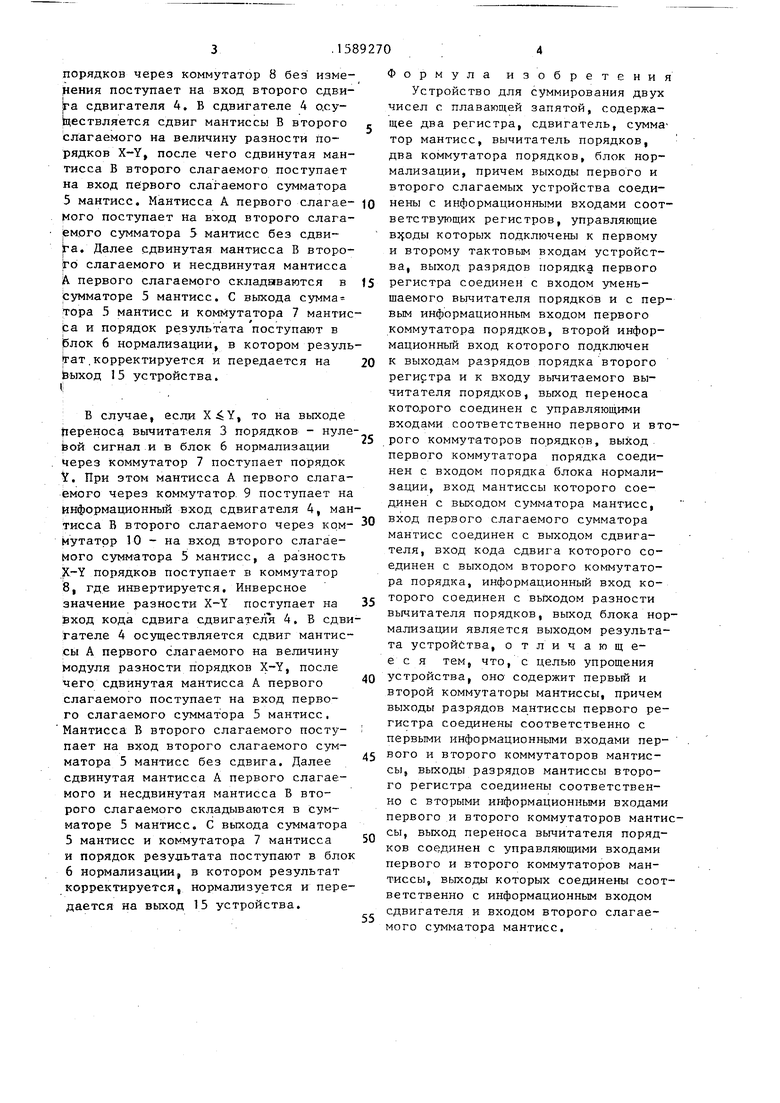

На чертеже представлена схема устройства для суммирования двух чисел с плавающей запятой.

Устройство для суммирования двух чисел с плавающей запятой содержит регистры 1 и 2, вычитатель 3 порядков, сдвигатель 4, сумматор 5 мантисс, блок 6 нормализации, коммутаторы 7 и 8 порядков, коммутаторы 9 и 10 мантиссы, входы П и 12 слагаемых устройства, тактовые входы 13 и 14 устройства, выход 15 суммы устройства.

Устройство для суммирования двух чисел с плавающей запятой работает следующим образом.

Вначале определяется разность порядков. Для этого с выхода регистра 1 порядок X первого слагаемого подается на первый вход вычитателя 3 порядков, с выхода регистра 2 порядок Y второго слагаемого- подается на второй вход вычитателя 3 порядков. В вычита- теле 3 порядков определяется разность порядков X-Y в обратном коде. При этом, если X Y (в этом случае запись разности порядков в обратном.коде совпадает с записью разности порядков с прямом коде), то на выходе переноса вычитателя 3 порядков будет единичный сигнал и в блок 6 нормализации через коммутатор 7 поступает больший порядок X. При этом мантисса В второго слагаемого через коммутатор 9 поступает на информационный вход сдвига- теля 4, мантисса А слагаемого через коммутатор 10 поступает на вход второго слагаемого сумматора 5 мантисс, а разность X-Y с выхода вычитателя 1

i

(Л

с

ел

IN9

порядков через коммутатор 8 без измерения поступает на вход второго сдви- |га сдвигателя 4. В сдвигателе 4 о,су- цествляется сдвиг мантиссы В второго слагаемого на величину разности порядков X-Y, после чего сдвинутая мантисса В второго слагаемого поступает на вход первого слагаемого сумматора 5 мантисс. Мантисса А первого слагав- мого поступает на вход второго слагаемого сумматора 5 мантисс без сдви- |га. Далее сдвинутая мантисса В второ- |г6 слагаемого и несдвинутая мантисса А первого слагаемого складаваются в сумматоре 5 мантисс. С выхода сумма тора 5 мантисс и коммутатора 7 мантисса и порядок результата поступают в (Блок 6 нормализации, в котором резуль ат.корректируется и передается на Ьыход 15 устройства.

В случае, если , то на выходе fiepeHoca вычитателя 3 порядков - нулевой сигнал и в блок 6 нормализации Через коммутатор 7 поступает порядок Y. При этом мантисса А первого слагаемого через коммутатор, 9 поступает на информационный вход сдвигателя 4, мантисса В второго слагаемого через ком- Мутатрр 10 - на вход второго слагаемого сумматора 5i мантисс, а разность X-Y порядков поступает в коммутатор 8, где инвертируется. Инверсное значение разности X-Y поступает на вход кода сдвига сдвигател я 4. В сдвигателе 4 осзлцествляется сдвиг мантиссы А первого слагаемого на величину модуля разности порядков X-Y, после Чего сдвинутая мантисса А первого слагаемого поступает на вход первого слагаемого сумматора 5 мантисс, Мантисса В второго слагаемого посту- пает на вход второго слагаемого сумматора 5 мантисс без сдвига. Далее сдвинутая мантисса А первого слагаемого и несдвинутая мантисса В второго слагаемого складываются в сумматоре 5 мантисс. С выхода сумматора

5мантисс и коммутатора 7 мантисса и порядок результата поступают в блок

6нормализации, в котором результат корректируется, нормализуется и передается на выход 15 устройства.

5 0

5

0

5

Формула изобретения

Устройство для суммирования двух чисел с плавающей запятой, содержащее два регистра, сдвигатель, сумматор мантисс, вычитатель порядков, два коммутатора порядков, блок нормализации, причем выходы первого и второго слагаемых устройства соединены с информационными входами соответствующих регистров, управляющие В2{оды которых подключены к первому и второму тактовым входам устройства, выход разрядов порядка первого регистра соединен с входом уменьшаемого вычитателя порядков и с первым информационным входом первого коммутатора порядков, второй инфор- мационньш вход которого подключен к выходам разрядов порядка второго регистра и к входу вычитаемого вычитателя порядков, выход переноса кото.рого соединен с управляющими входами соответственно первого и второго коммутаторов порядков, выход первого коммутатора порядка соединен с входом порядка блока нормализации, вход мантиссы которого соединен с выходом сумматора мантисс, вход первого слагаемого сумматора мантисс соединен с выходом сдвигателя, вход кода сдвига которого соединен с выходом второго коммутатора порядка, информационный вход которого соединен с вь1ходом разности вычитателя порядков, выход блока нормализации является выходом результата устройства, о тличающе- е с я тем, что, с целью упрощения устройства, оно содержит первый и второй коммутаторы мантиссы, причем выходы разрядов мантиссы первого регистра соединены соответственно с первыми информационными входами пер- вого и второго коммутаторов мантиссы, выходы разрядов мантиссы второго регистра соединены соответственно с вторыми информационными входами первого и второго коммутаторов мантиссы, выход переноса вычитателя порядков соединен с управляющими входами первого и второго коммутаторов мантиссы, выходы которых соединены соответственно с информационным входом сдвигателя и входом второго слагаемого сумматора мантисс.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1290300A1 |

| Устройство для вычисления синуса | 1986 |

|

SU1319025A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Арифметическое устройство | 1984 |

|

SU1193661A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1295387A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

Изобретение относится к вычислительной технике, может быть использовано при реализации арифметических устройств электронных вычислительных машин с плавающей запятой. Цель изобретения - упрощение устройства. Предложенное устройство содержит два регистра, вычитатель порядков, сдвигатель, сумматор мантисс, блок нормализации, два коммутатора порядков и два коммутатора мантисс. 1 ил.

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1290300A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-30—Публикация

1988-11-23—Подача