Изобретение относится к цифровой вычислительной технике и может быть иепользовано в вычислительных машина и устройствах, выполняющих математические операции над числами как в традиционной неизбыточной двоичной системе счисления, так и в избыточно знакоразрядной системе счисления с цифрами {-1, О, 1}.

Целью изобретения является расши-

рение области применения за счет обеспечения возможности обработки операндов как при двоичном, так и знак разрядном кодировании.

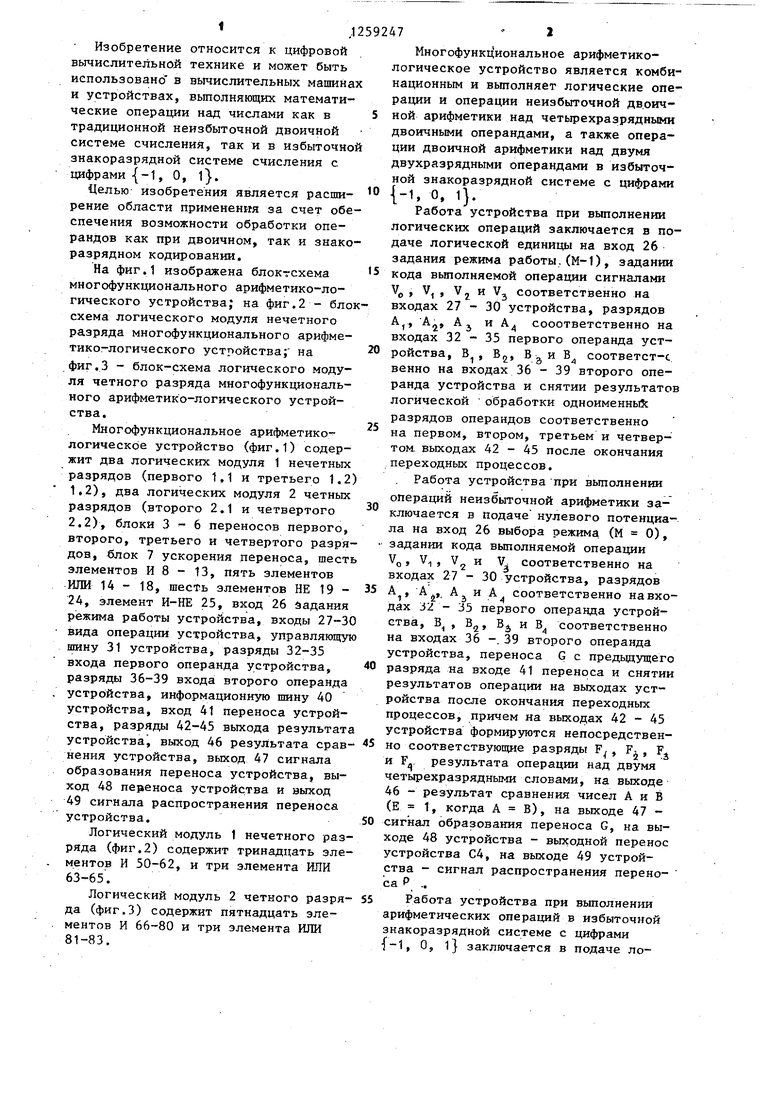

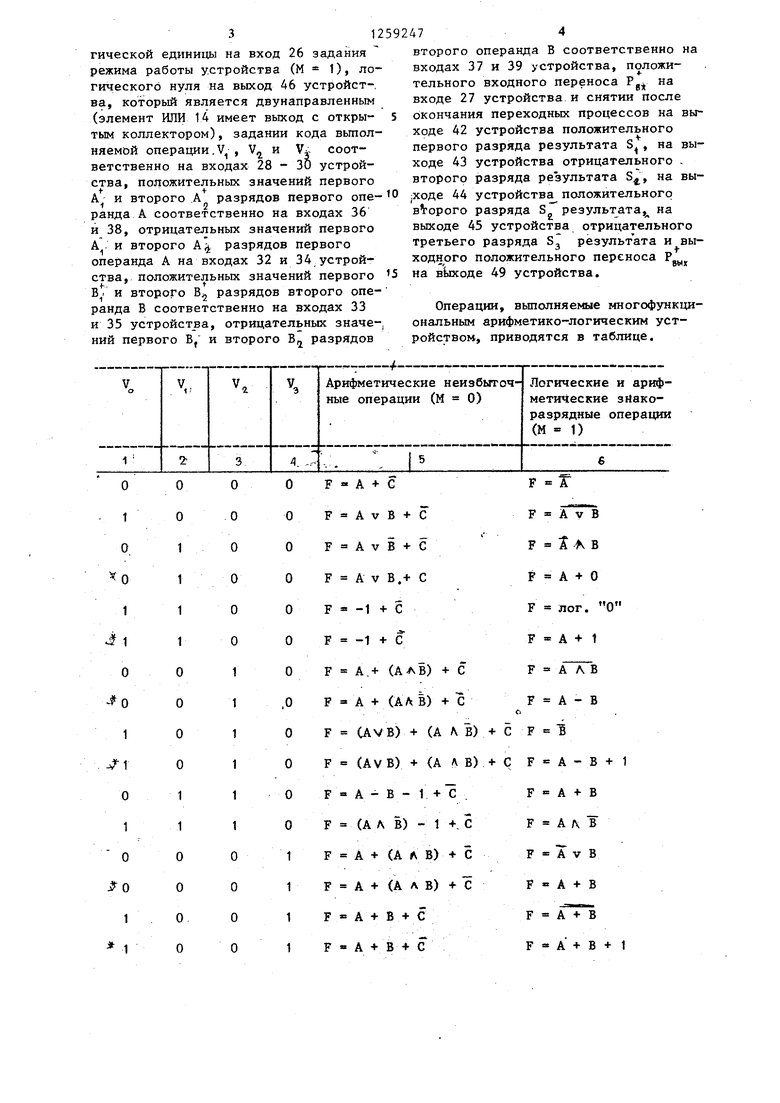

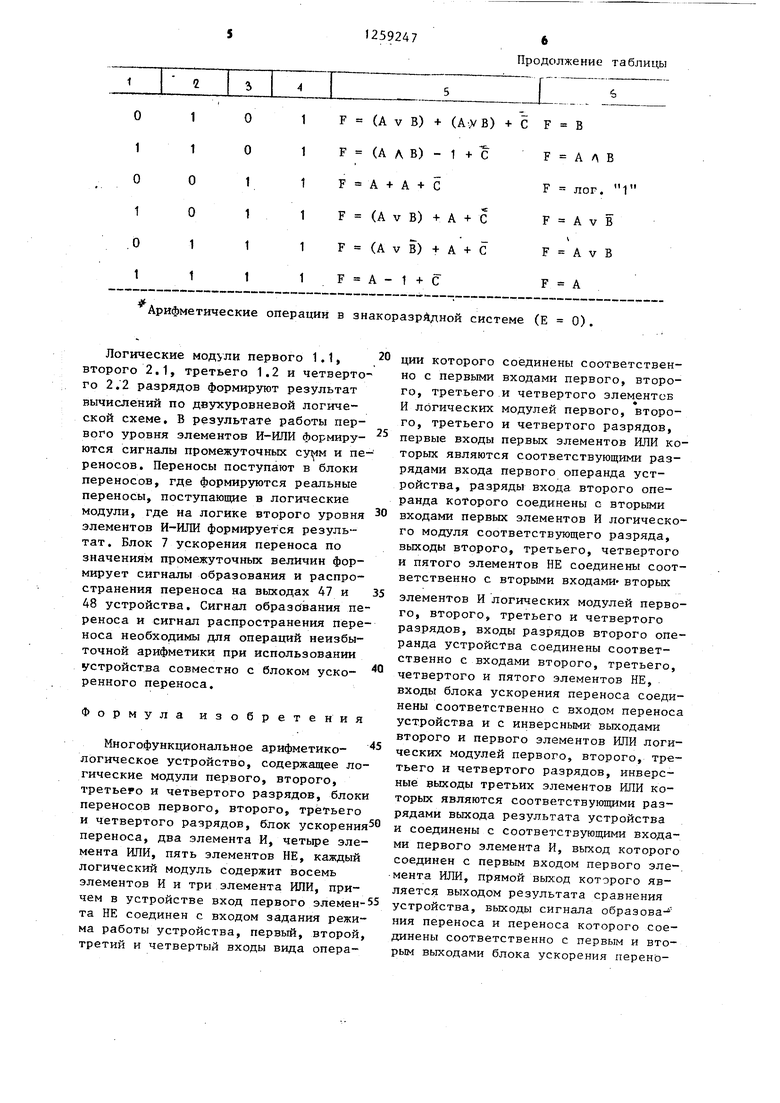

На фиг.1 изображена блоктсхема многофункционального арифметико-логического устройства; на фиг,2 - бл схема логического модуля нечетного разряда многофункционального арифметико-логического устройства; на фиг,3 - блок-схема логического модуля четного разряда многофункционального арифметико-логического устройства.

Многофункциональное арифметико- логическое устройство (фиг.1) содержит два логических модуля 1 нечетны разрядов (первого 1,1 и третьего 1. ), два логических модуля 2 четны разрядов (второго 2,1 и четвертого 2.2), блоки 3-6 переносов первого второго, третьего и четвертого разрдов, блок 7 ускорения переноса, шес элементов И 8 - 13, пять злементов ИЛИ 14 - 18, шесть злементов НЕ 19 2А, элемент И-НЕ 25, вход 26 задани режима работы устройства, входы 27вида операции устройства, управляющ шину 31 устройства, разряды 32-35 входа первого операнда устройства, разряды 36-39 входа второго операнд устройства, информационную шину 40 устройства, вход 41 переноса устройства, разряды 42-45 выхода результа устройства, выход 46 результата сра нения устройства, выход 47 сигнала образования переноса устройства, выход 48 переноса устройства и выход 49 сигнала распространения переноса устройства.

Логический модуль 1 нечетного раряда (фиг.2) содержит тринадцать злментов И 50-62, и три элемента ИЛИ 63-65.

Логический модуль 2 четного разрда (фиг.З) содержит пятнадцать эле- ментов И 66-80 и три элемента ИЛИ 81-83.

Многофункциональное арифметико- логическое устройство является комбинационным и выполняет логические операции и операции неизбыточной дв.оич- ной арифметики над четьфехразрядными двоичными операндами, а также операции двоичной арифметики над двумя двухразрядными операндами в избыточной знакоразрядной системе с цифрами

i О

Работа устройства при выполнении логических операций заключается в подаче логической единицы на вход 26 задания режима работы.(М-1), задании кода вьшолняемой операции сигналами V.

о

1

V, И з

соответственно на

А

входах 27 30 устройства, разрядов А, А-, AJ и А сооответственно на входах 3235 первого операнда устройства, В , Bj, ВдИ В соответст-с венно на входах 36 - 39 второго операнда устройства и снятии результатов логической обработки одноименный разрядов операндов соответственно на первом, втором, третьем и четвертом, выходах 42 - 45 после окончания переходных процессов.

Работа устройства при вьтолнении

операций неизбыточной арифметики заключается в Подаче нулевого потенциала на вход 26 выбора режима (М 0), задании кода выполняемой операции VQ, V, V и V, соответственно на входах 27 30 устройства, разрядов

й А, и А, соответственно навхо3 4

дах 32 - 35 первого операнда устрой5

0

5

ства, В. , В

2

В и В

соответственно

на входах 36 -.39 второго операнда устройства, переноса G с предьщущего разряда на входе 41 переноса и снятии результатов операции на выходах устройства после окончания переходных процессов, причем на выходах 42 - 45 устройства формируются непосредственF,

но соответствующие разряды г,

4, Fi

и F.. результата операции над двумя четырехразрядными словами, на выходе 46 - результат сравнения чисел А и В (Е 1, когда А В), на выходе 47 - сигнал образования переноса G, на выходе 48 устройства - выходной перенос устройства С4, на выходе 49 устройства - сигнал распространения переноса Р ..

Работа устройства при выполнении арифметических операций в избыточной знакоразрядной системе с цифрами {-1, О, 1} заключается в подаче ло3 1

гической единицы на вход 26 задания режима работы устройства (М 1), логического нуля на выход 46 устройства, который является двунаправленным (элемент ИЛИ 14 имеет выход с открытым коллектором), задании кода выполняемой операции.V, V и Vj- соответственно на входах 28 - 30 устройства, положительных значений первого А и второго А разрядов первого операнда А соответственно на входах 36 и 38, отрицательных значений первого А и второго А разрядов первого операнда А на входах 32 и 34 устройства, положительных значений первого и второго Bij разрядов второго операнда В соответственно на входах 33 и 35 устройства, отрицательных значений первого Bj и второго В, разрядов

592474

второго операнда В соответственно на входах 37 и 39 устройства, положительного входного переноса Р, на входе 27 устройства и снятии после 5 окончания переходных процессов на выходе 42 устройства положительного первого разряда результата S, на выходе 43 устройства отрицательного . второго разряда результата S, на вы 0 :ходе 44 устройства положительного второго разряда S результата, на выходе 45 устройства отрицательного третьего разряда S результата и выходного положительного переноса Р.„

.pWX

15 на выходе 49 устройства.

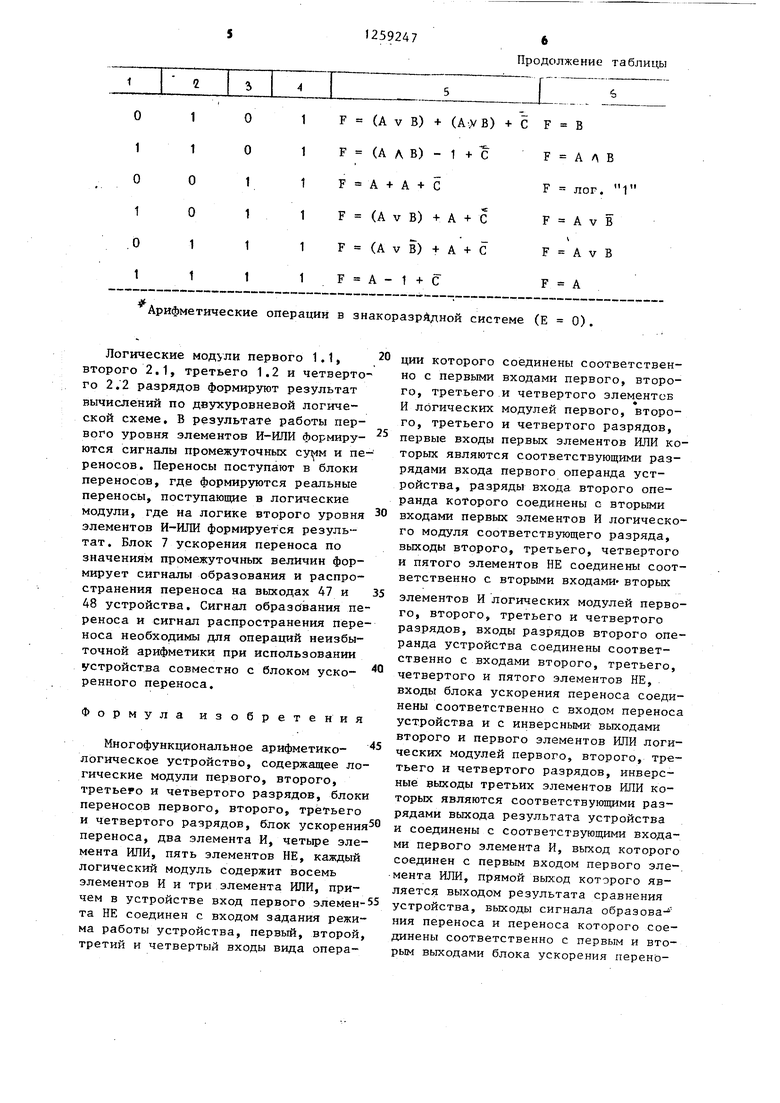

Операции, вьшолняемые многофункциональным арифметико-логическим устройством, приводятся в таблице.

л

Арифметические операции в энакоразрАдной системе (Е 0).

Логические модули первого 1.1, второго 2,1, третьего 1.2 и четвертого 2.2 разрядов формируют результат вычислений по двухуровневой логической схеме, В результате работы первого уровня элементов И-Ш1И формируются сигналы промежуточных и переносов. Переносы поступают в блоки переносов, где формируются реальные переносы, поступающие в логические модули, где на логике второго уровня элементов И-ИЛИ формируется результат . Блок 7 ускорения переноса по значениям промежуточных величин формирует сигналы образования и распространения переноса на выходах 47 и 48 устройства. Сигнал образбвания переноса и сигнал распространения переноса необходимы для операций неизбыточной арифметики при использовании устройства совместно с блоком уско- ренного переноса.

Формула изобретения

Многофункциональное арифметико- логическое устройство, содержащее логические модули первого, второго, третьего и четвертого разрядов, блоки переносов первого, второго, третьего и четвертого разрядов, блок ускорения переноса, два элемента И, четьфе элемента ИЛИ, пять элементов НЕ, каждый логический модуль содержит восемь элементов И и три элемента ИЛИ, причем в устройстве вход первого элемента НЕ соединен с входом задания режима работы устройства, первый, второй третий и четвертый входы вида операПродолжение таблицы

ции которого соединены соответственно с первыми входами первого, второго, третьего и четвертого элементов И логических модулей первого, второго, третьего и четвертого разрядов, первые входы первых элементов ИЛИ которых являются соответствующими разрядами входа первого операнда устройства, разряды входа второго операнда которого соединены с вторыми входами первых элементов И логического модуля соответствующего разряда, выходы второго, третьего, четвертого и пятого элементов НЕ соединены соответственно с вторыми входами вторых

элементов И логических модулей первого, второго, третьего и четвертого разрядов, входы разрядов второго операнда устройства соединены соответственно с входами второго, третьего, четвертого и пятого элементов НЕ, входы блока ускорения переноса соединены соответственно с входом переноса устройства и с инверсными выходами второго и первого элементов ИЛИ логических модулей первого, второго, третьего и четвертого разрядов, инверсные выходы третьих элементов ИЛИ которых являются соответствующими разрядами выхода результата устройства и соединены с соответствующими входами первого элемента И, выход которого соединен с первым входом первого эле-, мента ИЛИ, прямой выход которого является выходом результата сравнения устройства, выходы сигнала образова- ния переноса и переноса которого соединены соответственно с первым и вторым выходами блока ускорения парено.

са, инверсные выходы вторых элементов ИЛИ логических модулей первого, второго, третьего и четвертого разрядов соединены с соответствующими входами второго элемента И, выход ко торого соединен с первым входом вто- рого элемента ИЛИ, I инверсный выход которого является выходом сигнала распрост ранения переноса устройства, первые входы пятого и шестого элемен тов И логического модуля первого разряда соединены соответственно с прямым и инверсным выходами третьего элемента ИЛИ, первые входы пятого и шестого элементов И логического моду ля третье-го разряда- соединены соответственно с прямым и инверсным выходами четвертого элемента ИЖ, первые входы третьего и четвертого элементов ИЛИ соединены соответственно с выходами блоков переносов первого и третьего разрядов , первые входы пятого и шестого элементов И логического модуля второго разряда соед1 нены соответственно с прямым и ийверсным выходом блока переносов второго разряда, первые входы пятого и шестого элементов И логического модуля четвертого разряда соединены соответственно с прямым и инверсным выходами блока переноса четвертого разряда, первый и второй входы блоков переносов первого, второго, третьего и четвертого разрядов соединены с выходом первого элемента НЕ и с входом пере- носа устройства, третий и четвертый входы блока переноса первого, второего, третьего и четвертого разрядов .соединены соответственно с инверсными выходами второго и первого элементов ИЛИ логического модуля соответствующего разряда, причем в каждом логическом модуле первый вход первого элемента ИЛИ соединен с вторыми входами третьего и четвертого элементов И, второй вход первого элемента И соединен с третьим входом четвертого элемента И, второй вход второго элемента И соединен с третьим входом третьего элемента И, выходы первого и второго элементов И соединены соответственно с вторым и третьим входами первого элемента ИЛИ, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами.второго элемента ИЛИ, инверсный выход которого соединен с вторыми входами пятого и шестого элемен О

20

25

5 - 303540 45 50 55

тов И, инверсный выход первого элемента ИЛИ соединен с третьим входом пятого и с первым входом седьмого элементов И, прямой выход первого элемента ИЛИ соединен с первым входом восьмого и третьим входом шестого элементов И, прямой выход второго элемента ИЛИ соединен с вторыми входами седьмого и восьмого элементов И, первые входы пятого и шестого элементов И соединены соответственно с третьими входами восьмого и седьмого эпементов И, выходы пятого, шестого седьмого и восьмого элементов И соединены соответственно с первым, вторым, третьим, и четвертым входами третьего элемента ИЛИ, отличающееся тем,, что, с целью расширения области применения за счет обеспечения возможности обработки операндов как при двоичном, так и знакрразрядном кодировании, оно содержит пятый элемент ИЛИ, шестой элемент НЕ, третий, четвертый, пятый и шестой элементы И и элемент И-НЕ, каждый логический модуль разрядов дополнительно содержит девятый, десятый, одиннадцатый, двенадцатый, тринадцатый элементы И, а каждый логический модуль четных разрядов дополнительно содержит девятьш, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый и пятнадцатый элементы И, причем в устройстве первый вход пятого элемента ИЛИ соединен с вторым входом вида операции устройства, прямой выход первого элемента ИЛИ через шестой элемент НЕ соединен с первыми входами третьего элемента И и элемента И-НЕ, вторые входы которых соединены с вторым входом первого элемента ИЛИ и входом задания режима работы устройства, выход элемента И-НЕ соединен с пятым входом второго элемента И, с вторым входом

1ПЯТОГО элемента ИЛИ и с третьими вхо- I

дами первых элементов И логических модулей первого, второго, третьего и четвертого разрядов, первые входы девятых элементов И которых соединены с первыми входами четвертого, пятого и шестого элементов И и с выходом третьего элемента И, вторые входы четвертого и пятого элементов И соединены соответственно с прямьп и выхо- дами вторых элементов ИЛИ логических модулей второго и четвертого разрядов, выход четвертого элемента И - с

вторым входом четвертого элемента ИЛИ, выход пятого элемента И - с вторым входом второго элемента ИЛИ, второй вход третьего элемента ИЛИ - с .. выходом шестого элемента И, второй вход которого соединен с первым входом вида операции устройства, инв€;рс- ный выход пятого элемента ИЛИ соединен с первыми входами десятых элементов И логических модулей первого и третьего разрядов, первые входы одиннадцатых элементов И которьпс соединены- соответственно с первыми входами первых элементов ИЛИ логических модулей второго и четвертого разрядов, вторые входы десятых элементов И логических модулей первого и третьего разрядов - Соответст}зенно с вторыми входами первых элементов И логических модулей второго и четвертого разря- дов, вторые входЬг одиннадцатых элементов И логических модулей первого и третьего разрядов - соответственно с вторыми входами вторых элементов И логических модулей второго и четвер- того разрядов, третьи входы десятых элементов И логических модулей первого и третьего разрядов - соответственно с инверсными выходами первых элементов-ИЛИ логических модулей вто ррго и четвертого разрядов соответственно, вторые входы девятых элементов И логических модулей второго и четвертого разрядов соединены соответственно с вторыми входами вторых элементов И логических модулей первого и третьего разрядов, первые входы .тринадцатых элементов И логических модулей второго .и четвертого разрядов - соответственно с прямыми выхо- дами вторых элементов ИЛИ логических модулей первого и третьего разрядов, вторы(е входы тринадцатых элементов И логических модулей второго и четвертого разрядов - соотв етственно с пер выми входами пятых элементов И логических модулей первого и третьего разрядов, первые входы четырнадцатых элементов И логических модулей второго и четвертого разрядов - с инверс иымн выходами первых элементов ИЛИ логических модулей первого и третьег )азрядов соответственно, причем в каждом логическом модуле нечетных разрядов третьи входы первого и вто рого элементов И соединены с четвертыми входами третьего и четвертого элементов И, первый вход девятого

элемента И - с первыми входами две- надцатого и тринадцатого элементов и , первый вход десятого элемента И - с третьим входом одиннадцатого элемента И, первый вход которого соединен с вторым входом двенадцатого элемента И,, второй вход десятого элемента И - с третьим входом двенадцатого элемента И, второй вход одиннадцатого элемента И - с вторьпч входом тринадцатого элемента И, третий вход десятого элемента И - с третьим входом тринадцатого элемента И, четвертые входы десятого и одиннадцатого элементов И соединены с вторым входом первого элемента И, второй вход второго элемента И соединен с вторым входом девятого и четвертыми входами двенадцатого и тринадцатого элементов И, ВЫХОДЫ девятого, десятого, одиннацатого, двенадцатого и тринадцатого элементов И соединены соответственно с третьим, четвертым, пятым, шестым и седьмым входами второго элемента ИЛИ, причем в каждом логическом модуле четного разряда третий вход первого элемента И соединен с третьим входом второго элемента И и с четвертыми входами четвертого, пятого, шестого, седьмого и восьмого элементов И, первый вход девятого элемента И - с первыми входами десятого, одиннадцатого, двенадцатого, пятнадцатого элементов И, с вторым входом четырнадцатого,элемента И и с третьим входом: тринадцатого элемента И, второй вход девятого элемента И - с вторыми входами десятого и одиннад- цатого элементов И, первый вход тринадцатого элемента И - с вторым входом пятнадцатого элемента И, второй вход тринадцатого элемента И - с третьим входом четырнадцатого элемента И, первый вход четырнадцатого элемента И - с третьим входом пятнадцатого элемента И, инверсный выход первого элемента ШШ - с третьим входом десятого и вторым входом двенадцатого- злементов И, третий вход одиннадцатого элемента И - с первым входом первого элемента :ШШ, третий .вход двенадцатого элемента И - с первым входом четвертого элемента И, четвертые одиннадцатого и двенадцатого элементов И соединены с вторым входом первого элемента И, четвертьй вход десятого элемента И - с вТорым входом второго элемента И, выходы девятого.

ресятого, одиннадцатого и двенадцатого элементов И соединены соответственно с третьим, четвертым, пятым и шестьм входами второго элемента ИЛИ, выходы тринадцатого, четьфнадцатого и пятнадцатого элементов И - с пятым.

шестым и седьмым входами третьего элемента ИЛИ соответственно, третий вход девятого элемента И логического модуля каждого из разрядов соединен с первым входом второго элемента И . этого же разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в двоичном избыточном коде | 1987 |

|

SU1413623A1 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| Устройство для умножения | 1987 |

|

SU1411733A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Устройство для сложения в избыточной системе счисления | 1986 |

|

SU1365077A1 |

| Четверичный сумматор | 1983 |

|

SU1124290A1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах и устройствах, работающих как в традиционной двоичной системе сч-исления, так и в знакоразрядной избыточной системе счисления с числами -Г, О, ll Целью изобретения является расширение области применения за счет возможности обработки операндов как при двоичном, так и знакоразрядном кодировании. Сущность изобретения заключается в том, что в устройство, содержащее логические модули первого, второго, третьего и четвертого разрядов, блоки переносов первого, второго, третьего и четвертого разрядов, блок ускорения переноса, пять элементов НЕ, два элемента И и четыре элемента ИЛИ, дополнительно вводятся элемент ИЛИ, элемент НЕ, четыре элемента И и элемент .И-НЕ, а также по семь элементов И в каждый модуль четных разрядов и по пять элементов И в каждый модуль нечетных разрядов с -соответствующими связями. 3 ил. с & (Л С

35

«

sn

2(2}

s

V

34

31

%

1(2}

g

2(1}

9ад

НИ

С

4fl

1(1)

Л

«

e lIHlh

гв ft

О.Юрковецкая

fj,; (. V

fiw (zw гаг;

уг.З

Составитель А.Клюев Техред И.Попович

Заказ 5122/46 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

По делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Е.Рошко

| Арифметико-логическое устройство | 1976 |

|

SU648979A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многофункциональное устройство | 1982 |

|

SU1100618A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электронная промьппленность, 1979, вып | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1986-09-23—Публикация

1985-04-08—Подача