1

(21)3989271/24-24

(22)10.12.85

(46) 15.02.90. Бил, № 6

(72) Ю.П. Зубков

(53) 621.398(088.8)

(56) Авторское свидетельство СССР

№ 1078613, кл. Н 03 М 7/02, 1982.

Авторское свидетельство СССР № 797069, кл. Н 03 М 7/02, 1979. (54)(57; УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО РАВНОВЕСНОГО КОДА В ПОЛНЫЙ ДВОИЧНЫЙ КОД, содержащее элемент задержки и счетчики, вход первого счетчика является входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены пороговый блок, ключ, блок памяти, сумматор и хронизатор, объединенные входы порогового блока, хронизатора и счетный вход второго счетчика подключены к входу устройства, выход порогового блока соединен непосредственно со счетным входом третьего счетчика и через элемент задержки с управляющим входом ключа, выходы второго и третьего счетчиков соединены соответственно с первыми и вторыми адресными входами блока памяти, выход которого соединен с информационным входом ключа, выход ключа соединен с информационным входом сумматора, первый - четвертый выходы хронизатора соединены с управляющими входами соответственно второго, третьего счетчиков, блока памяти и сумматора, выход первого счетчика соединен с входами установки в О второго, третьего .счетчиков и сумматора, выход сумматора является выходом устройства.

i

IB

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и преобразования двоичного равновесного кода | 1985 |

|

SU1317661A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для преобразования двоичного равновесного кода в полный двоичный код | 1985 |

|

SU1596463A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Устройство для приема избыточной информации | 1984 |

|

SU1167638A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

Устройство для преобразования двоичного равновесного кода в полный двоичный код, содержащее элемент задержки и счетчики, вход первого счетчика является входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены пороговый блок, ключ, блок памяти, сумматор и хронизатор, объединенные входы порогового блока, хронизатора и счетный вход второго счетчика подключены к входу устройства, выход порогового блока соединен непосредственно со счетным входом третьего счетчика и через элемент задержки с управляющим входом ключа, выходы второго и третьего счетчиков соединены соответственно с первыми и вторыми адресными входами блока памяти, выход которого соединен с информационным входом ключа, выход ключа соединен с информационным входом сумматора, первый - четвертый выходы хронизатора соединены с управляющими входами соответственно второго, третьего счетчиков, блока памяти и сумматора, выход первого счетчика соединен с входами установки в "0" второго, третьего счетчиков и сумматора, выход сумматора является выходом устройства.

Изобретение относится к электросвязи и может быть использовано в системах передачи информации и вычислительной технике.

Цель изобретения - повышение быстродействия устройства.

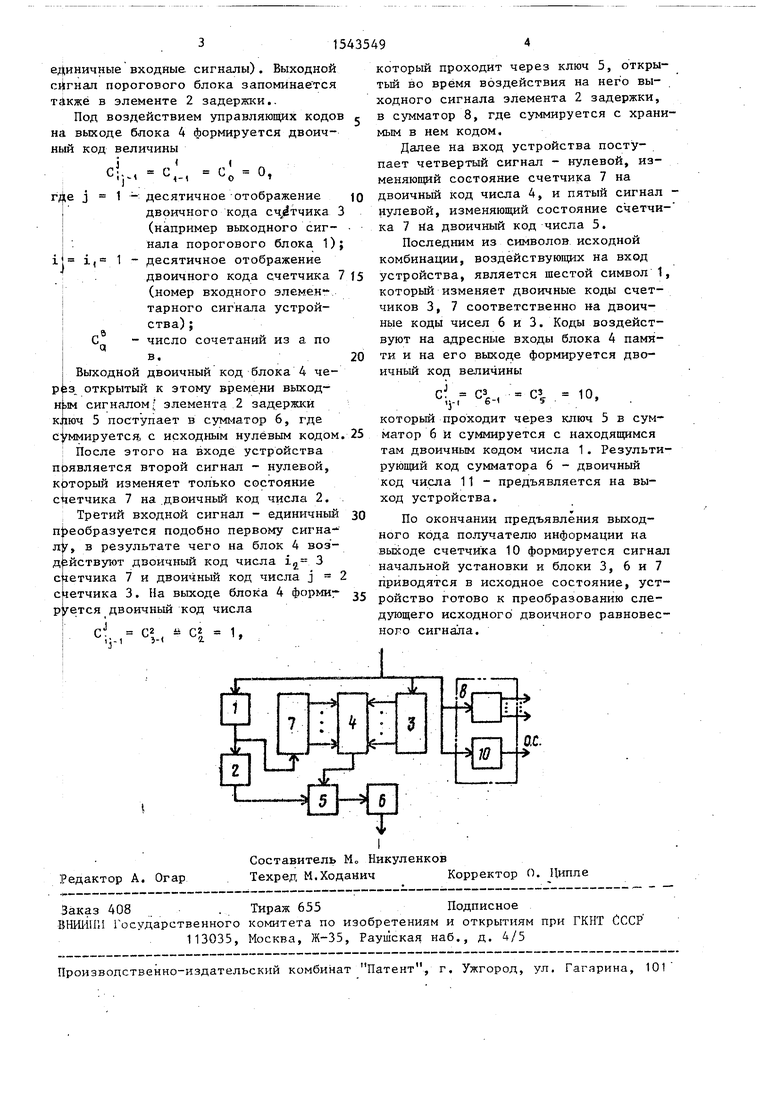

На чертеже показана структурная схема устройства.

Устройство содержит пороговый блок 1 элемент 2 задержки, третий счетчик 3, блок 4 памяти, ключ 5, сумматор 6, второй счетчик 7 и блок 8 управления, выполненный на хрониза- торе 9 и первом счетчике 10.

Устройство работает следующим образом.

Пусть, для определенности, на вход устройства последовательно поступают символы (сигналы) комбинации 100101 двоичного Н-6-значного кода с постоянным весом К-3.

Первый (нумерация разрядов и еди- ниц в комбинации осуществляется справа налево) символ 1 запускает блок 8 управления, запоминается в счетчике 7 и в виде двоичного кода воздействует на блок 4 памяти. На другие входы блока 4 воздействует двоичный код счетчика 3, в котором запоминается входной единичный сигнал после прохождения им порогового блока 1 (на выход порогового блока 1 проходят только У1

Ј DO СП Ј

CO

единичные входные сигналы). Выходной сигнал порогового блока запоминается также в элементе 2 задержки.

Под воздействием управляющих кодов с на выходе блока 4 формируется двоичный код величины

CV С, - cl - о,

j 1 - десятичное отображение ю i двоичного кода счетчика 3

(например выходного сиг- нала порогового блока 1); , 1 - десятичное отображение

LJ

который проходит через ключ 5, открытый во время воздействия на него выходного сигнала элемента 2 задержки, в сумматор 8, где суммируется с хранимым в нем кодом.

Далее на вход устройства поступает четвертый сигнал - нулевой, изменяющий состояние счетчика 7 на двоичный код числа 4, и пятый сигнал - нулевой, изменяющий состояние счетчи- ка 7 На двоичный код числа 5.

Последним из символов исходной комбинации, воздействующих на вход

двоичного кода счетчика 7 15 устройства, является шестой символ 1,

(номер входного элементарного сигнала устройства) ; С - число сочетаний из а по

в.20

Выходной двоичный код блока 4 че- pfes открытый к этому времени выход- HiiM сигналом, элемента 2 задержки ключ 5 поступает в сумматор 6, где суммируется, с исходным нулевым кодом. 25

После этого на входе устройства появляется второй сигнал - нулевой, который изменяет только состояние счетчика 7 на двоичный код числа 2.

Третий входной сигнал - единичный 30 преобразуется подобно первому сигналу, в результате чего на блок 4 воздействуют двоичный код числа i 3 счетчика 7 и двоичный код числа j 2

который изменяет двоичные коды счетчиков 3, 7 соответственно на двоичные коды чисел 6 и 3. Коды воздействуют на адресные входы блока 4 памяти и на его выходе формируется двоичный код величины

Cij.,- Ce- С 10 который проходит через ключ 5 в сумматор б и суммируется с находящимся там двоичным кодом числа 1. Результирующий код сумматора 6 - двоичный код числа 11 - предъявляется на выход устройства.

По окончании предъявления выходного кода получателю информации на выходе счетчика 10 формируется сигнал начальной установки и блоки 3, 6 и 7

„ „ , ,приводятся в исходное состояние, устсчетчика 3. На выходе блока 4 форми-эс м35 роиство готово к преобразованию сле- руется двоичный код числа

дующего исходного двоичного равновесГ Г2 & rt 1 L,;., S- Ч

ного сигнала.

который проходит через ключ 5, открытый во время воздействия на него выходного сигнала элемента 2 задержки, в сумматор 8, где суммируется с хранимым в нем кодом.

Далее на вход устройства поступает четвертый сигнал - нулевой, изменяющий состояние счетчика 7 на двоичный код числа 4, и пятый сигнал - нулевой, изменяющий состояние счетчи- ка 7 На двоичный код числа 5.

Последним из символов исходной комбинации, воздействующих на вход

который изменяет двоичные коды счетчиков 3, 7 соответственно на двоичные коды чисел 6 и 3. Коды воздействуют на адресные входы блока 4 памяти и на его выходе формируется двоичный код величины

Cij.,- Ce- С 10 который проходит через ключ 5 в сумматор б и суммируется с находящимся там двоичным кодом числа 1. Результирующий код сумматора 6 - двоичный код числа 11 - предъявляется на выход устройства.

По окончании предъявления выходного кода получателю информации на выходе счетчика 10 формируется сигнал начальной установки и блоки 3, 6 и 7

ного сигнала.

Авторы

Даты

1990-02-15—Публикация

1985-12-10—Подача