Фиг, г

Изобретение относится к вычислитель-, мой технике и может быть использовано в системах обработки информации.

Цель изобретения - расширение области применения путем обеспеченя возможности одновременной записи и считывания.

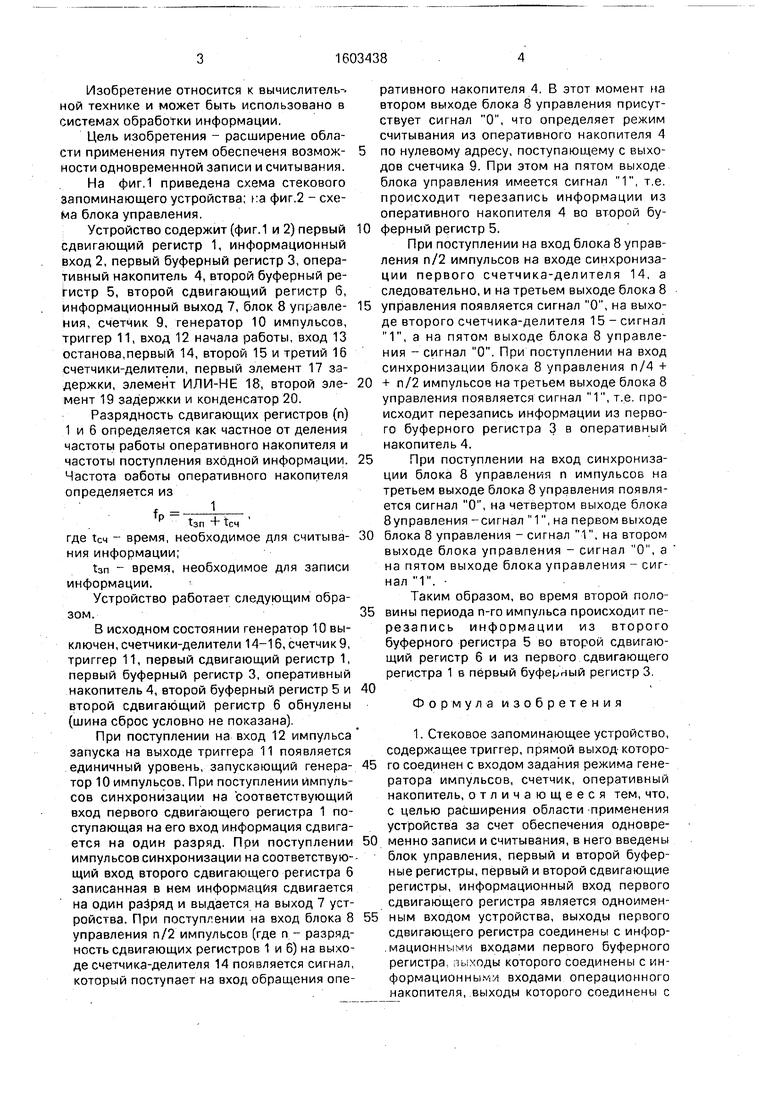

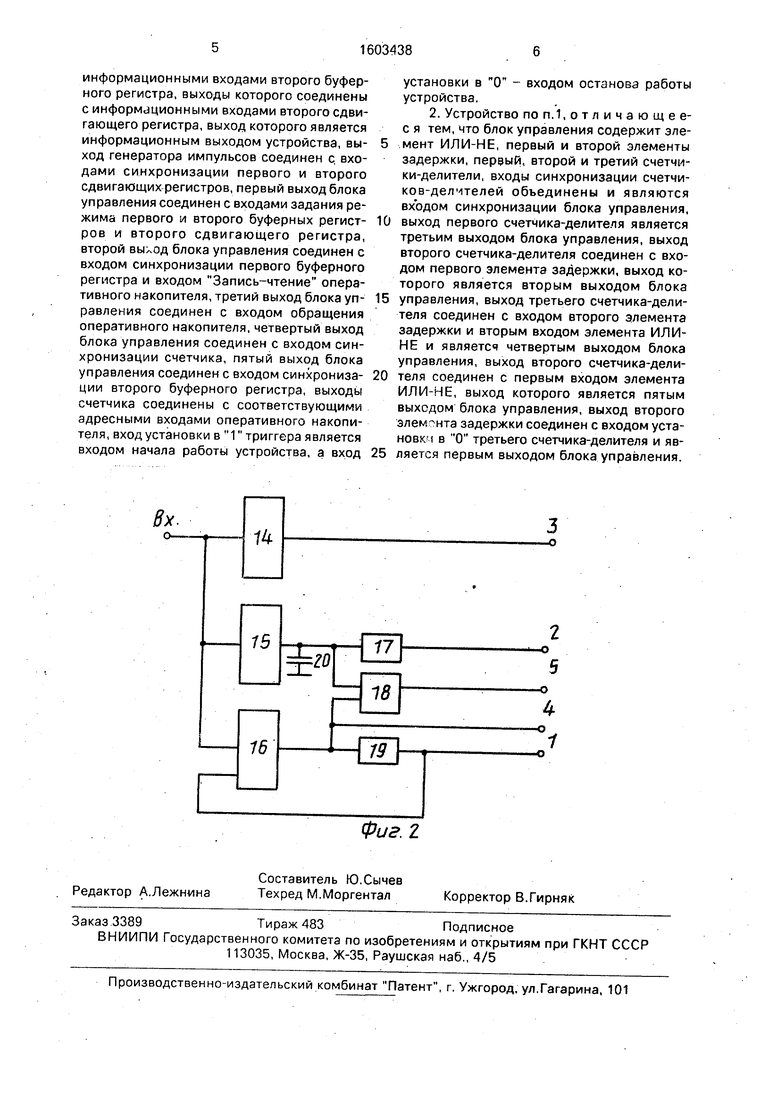

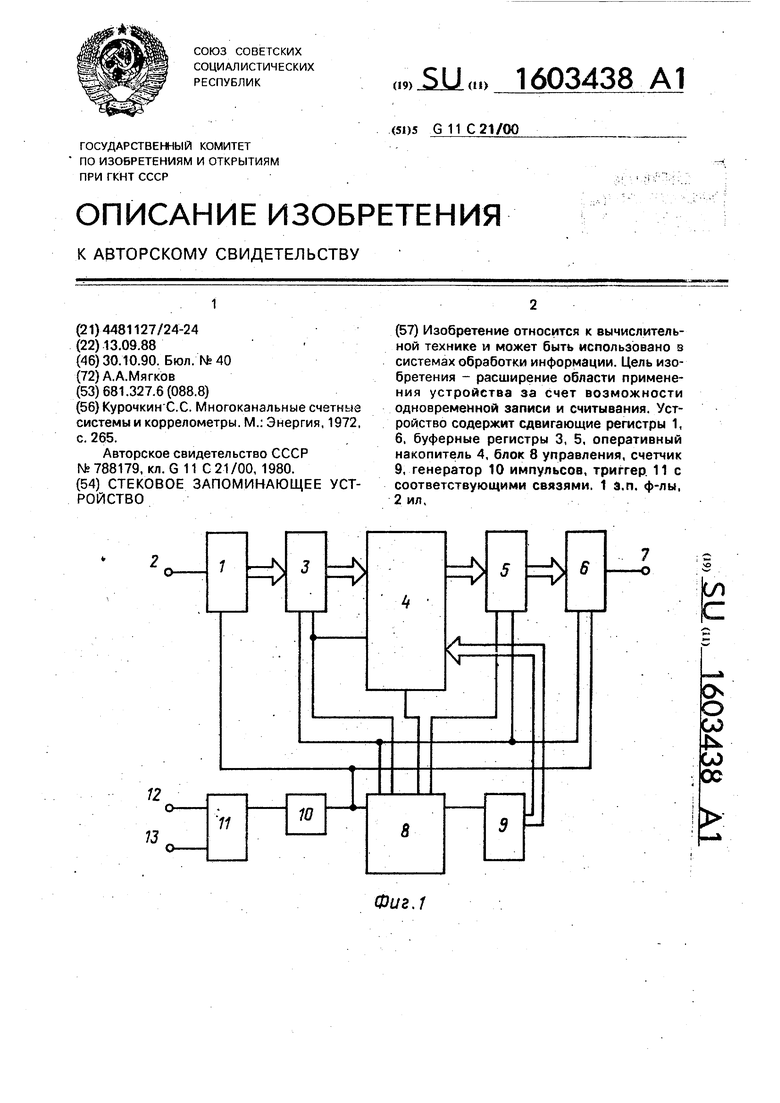

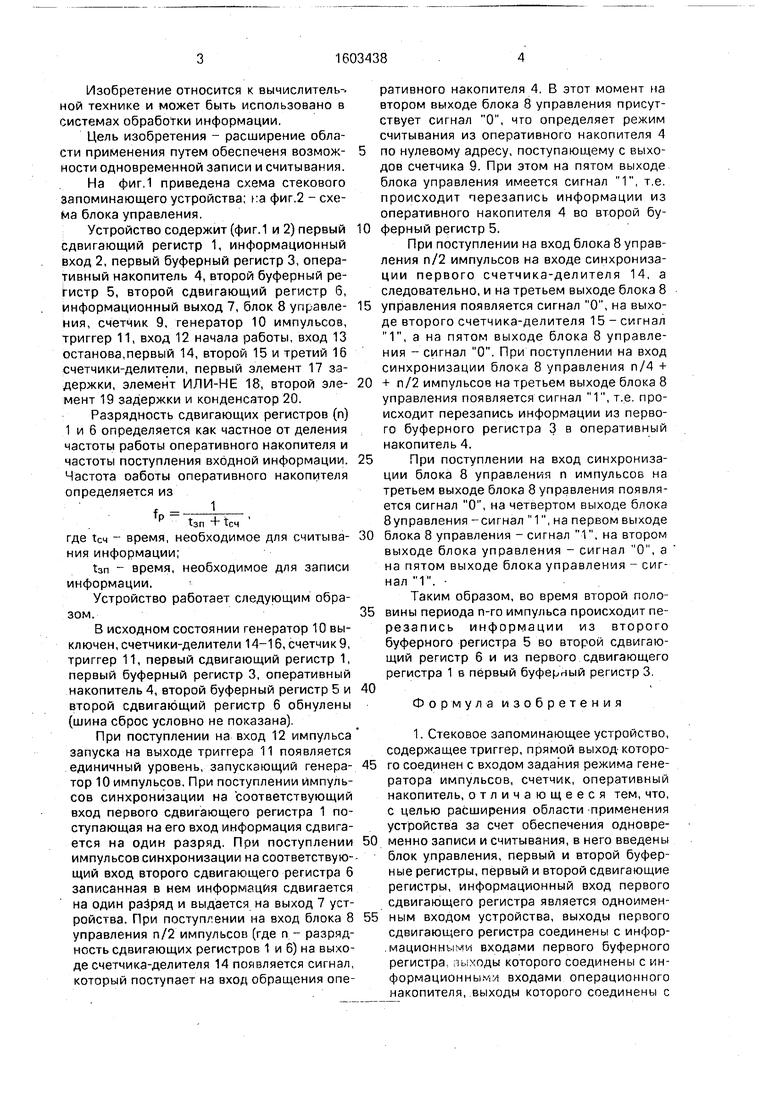

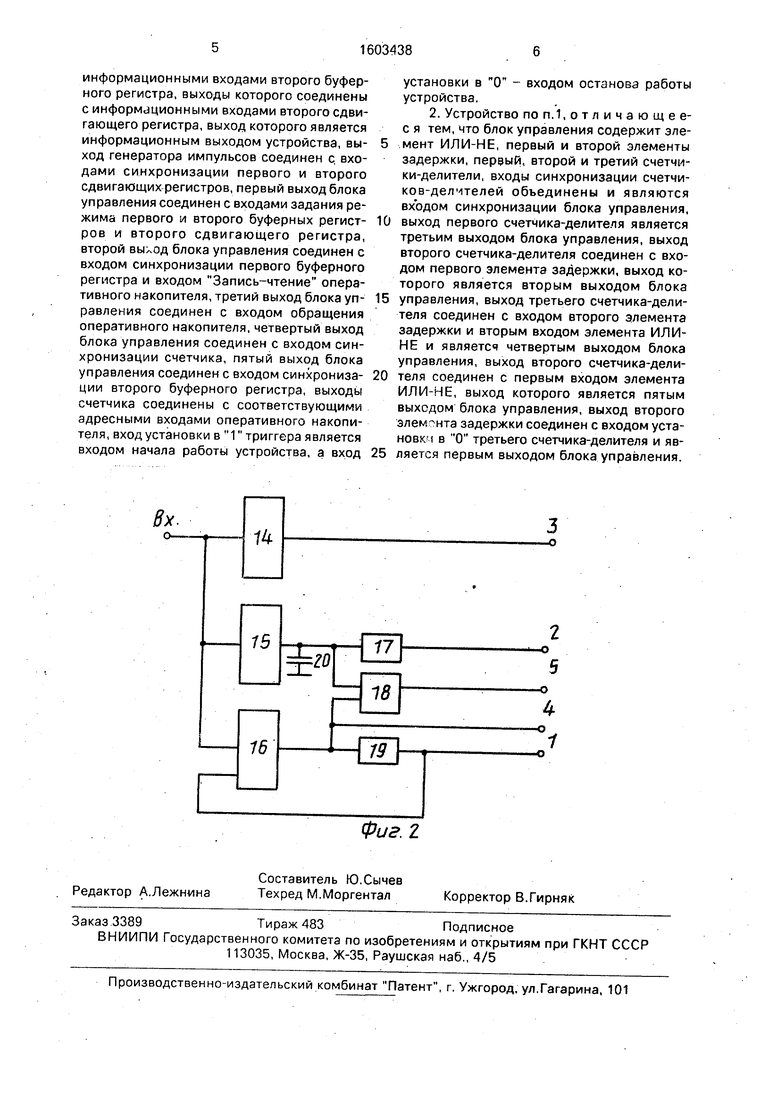

На фиг,1 приведена схема стекового запоминающего устройства; ка фиг.2 - схема блока управления.

Устройство содержит (фиг.1 и 2) первый сдвигающий регистр 1, информационный вход 2, первый буферный регистр 3, оперативный накопитель 4, второй буферный ре- Гистр 5, второй сдвигающий регистр 6, информационный выход 7, блок 8 управления, счетчик 9, генератор 10 импульсов, триггер 11, вход 12 начала работы, вход 13 останова,первый 14, второй 15 и третий 16 счетчики-делители, первый элемент 17 задержки, элемент ИЛИ-НЕ 18, второй элемент 19 задержки и конденсатор 20.

Разрядность сдвигающих регистров (п) 1 и 6 определяется как частное от деления частоты работы оперативного накопителя и частоты поступления входной информации. Частота оаботы оперативного накопителя определяется из

f j.

Р tan +tc4

где tc4 - время, необходимое для считывания информации;

tan время, необходимое для записи информации.

Устройство работает следующим образом.

В исходном состоянии генератор 10 выключен, счетчики-делители 14-16, счетчик 9, триггер 11, первый сдвигающий регистр 1, первый буферный регистр 3, оперативный накопитель 4, второй буферный регистр 5 и второй сдвигающий регистр 6 обнулены (шина сброс условно не показана).

При поступлении на вход 12 импульса запуска на выходе триггера 11 появляется единичный уровень, запускающий генератор 10 импульсов. При поступлении Импульсов синхронизации на соответствующий вход первого сдвигающего регистра 1 поступающая на его вход информация сдвигается на один разряд. При поступлении импульсов синхронизации на соответствующий вход второго сдвигающего регистра 6 записанная в нем информация сдвигается на один разряд и выдается на выход 7 устройства. При поступлении на вход блока 8 управления п/2 импульсо (где п - разрядность сдвигающих регистров 1 и 6) на выходе счетчика-делителя 14 появляется сигнал который поступает на вход обращения опеативного накопителя 4. В этот момент на втором выходе блока 8 управления присуттвует сигнал О, что определяет режим читывания из оперативного накопителя 4 по нулевому адресу, поступающему с выхоов счетчика 9. При этом на пятом выходе блока управления имеется сигнал 1, т.е. происходит перезапись информации из оперативного накопителя 4 во второй бу- ферный регистр 5.

При поступлении на вход блока 8 управления п/2 импульсов на входе синхронизации первого счетчика-делителя 14, а следовательно, и на третьем выходе блока 8 управления появляется сигнал О, на выходе второго счетчика-делителя 15 - сигнал 1, а на пятом выходе блока 8 управления -сигнал О. При поступлении на вход синхронизации блока 8 управления п/4 + + л/2 импульсов на третьем выходе блока 8 управления появляется сигнал 1, т.е. происходит перезапись информации из первого буферного регистра 3 в оперативный накопитель 4.

При поступлении на вход синхронизации блока 8 управления п импульсов на третьем выходе блока 8 управления появляется сигнал О, на четвертом выходе блока 8управления -сигнал 1, на первом выходе блока 8 управления - сигнал 1, на втором выходе блока управления - сигнал О, а на пятом выходе блока управления - сигнал 1.

Таким образом, во время второй поло- вины периода п-го импульса происходит пе- резапись информации из второго буферного регистра 5 во второй сдвигающий регистр 6 и из первого сдвигающего регистра 1 в первый буферный регистр 3.

Формула изобретения

1. Стековое запоминающее устройство, содержащее триггер, прямой выход которого соединен с входом задания режима генератора импульсов, счетчик, оперативный накопитель, отличающееся тем, что, с целью расширения области -применения устройства за счет обеспечения одновременно записи и считывания, в него введены блок управления, первый и второй буферные регистры, первый и второй сдвигающие регистры, информационный вход первого сдвигающего регистра является одноименным входом устройства, выходы первого сдвигающего регистра соединены с инфор- .мационными входами первого буферного регистра, пыходы которого соединены с информационными входами операционного накопителя, выходы которого соединены с

информационными входами второго буферного регистра, выходы которого соединены с информационными входами второго сдвигающего регистра, выход которого является информационным выходом устройства, вы- ход генератора импульсов соединен с, входами синхронизации первого и второго сдвигающих регистров, первый выход блока управления соединен с входами задания режима первого и второго буферных регист- ров и второго сдвигающего регистра, второй выход блока управления соединен с входом синхронизации первого буферного регистра и входом Запись-чтение оперативного накопителя, третий выход блока уп- равления соединен с входом обращения оперативного накопителя, четвертый выход блока управления соединен с входом синхронизации счетчика, пятый выход блока управления соединен с входом синхрониза- ции второго буферного регистра, выходы счетчика соединены с соответствующими адресными входами оперативного накопителя, вход установки в 1 триггера является входом начала работы устройства, а вход

установки в О - входом останова работы устройства,

2. Устройство поп.1,отличающее- с я тем, что блок управления содержит элемент ИЛИ-НЕ, первый и второй элементы задержки, перзый, второй и третий счетчики-делители, входы синхронизации счетчи- ко в-делмтелей объединены и являются входом синхронизации блока управления, выход первого счетчика-делителя является третьим выходом блока управления, выход второго счетчика-делителя соединен с входом первого элемента задержки, выход которого является вторым выходом блока управления, выход третьего счетчика-делителя соединен с входом второго элемента задержки и вторым входом элемента ИЛИ- НЕ и является четвертым выходом блока управления, выход второго счетчика-делителя соединен с первым входом элемента ИЛИ-НЕ, выход которого является пятым выходом блока управления, выход второго элемента задержки соединен с входом установки в О третьего счетчика-делителя и является первым выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Буферное запоминающее устройство | 1979 |

|

SU822287A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство для ввода информации | 1979 |

|

SU855649A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Формирователь импульсов | 1986 |

|

SU1383468A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации. Цель изобретения - расширение области применения устройства за счет возможности одновременной записи и считывания. Устройство содержит сдвигающие регистры 1, 6, буферные регистры 3, 5, оперативный накопитель 4, блок 8 управления, счетчик 9, генератор 10 импульсов, триггер 11 с соответствующими связями. 1 з.п. ф-лы, 2 ил.

Вх.

о-

t4

15

20

-о

17

| Курочкин С.С | |||

| Многоканальные счетные системы и коррелометры | |||

| М.: Энергия, 1972, с | |||

| САННЫЙ ВЕЛОСИПЕД С ВЕДУЩИМ КОЛЕСОМ, СНАБЖЕННЫМ ШИПАМИ | 1921 |

|

SU265A1 |

| Накопитель | 1978 |

|

SU788179A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-10-30—Публикация

1988-09-13—Подача