Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля и диаг- ностики.

Цель изобретения - расширение функциональных возможностей за счет ; фиксации перемежающихся сбоев и их локализации в цепях с замкнутым контуром воздействий (с обратными связями) .

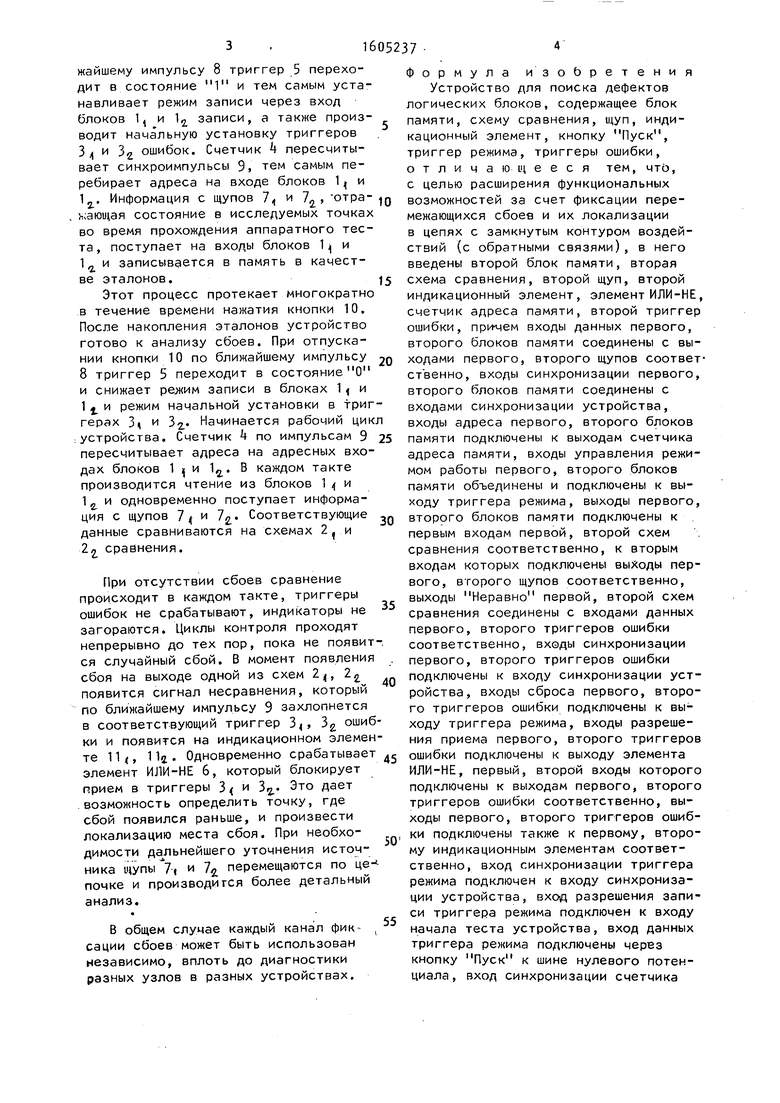

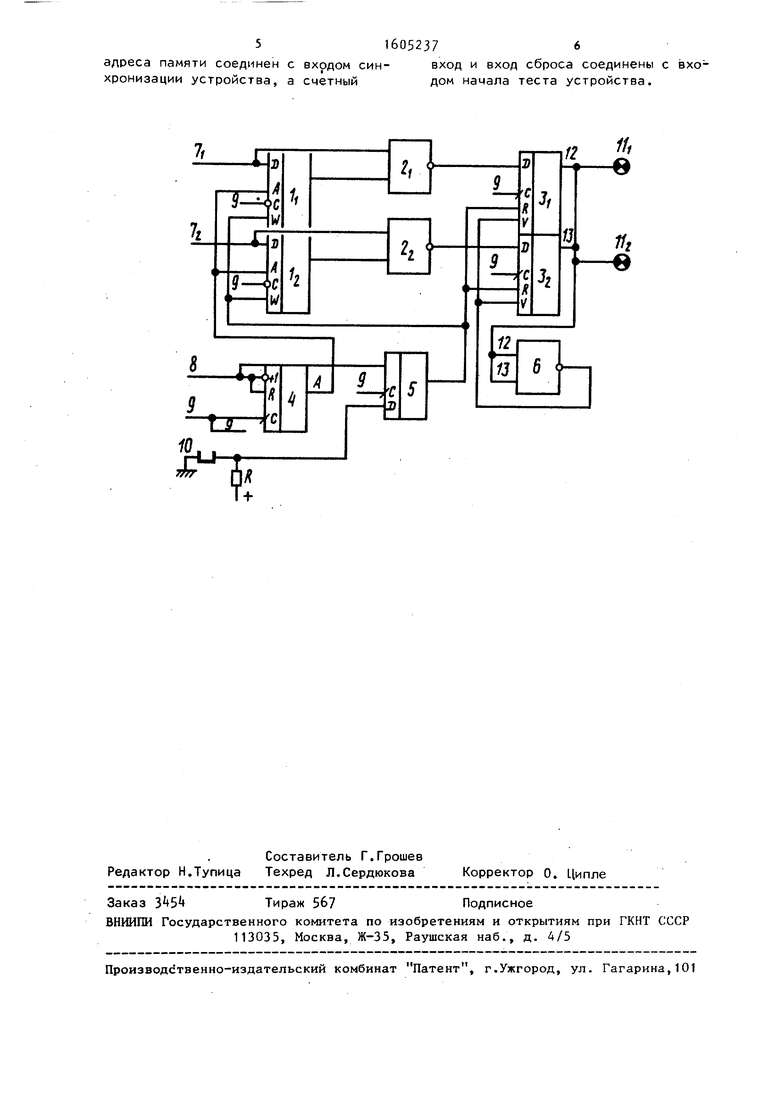

На чертеже показана схема устройства.

Устройство для поиска дефектов логических блоков содержит первый 1 и второй l блоки памяти, схемы 2 и 22. сравнения, триггеры 3 и З ошибок, счетчик адреса памяти, триггер 5 режима, элемент ИЛИ-НЕ 6, первый и второй 7ч щупы, выход 8 начала места, вход 9 синхронизации устройства, кнопку Пуск 10, индикационные элементы 11, и llj.

Предполагается, что ди агностируе- мая аппаратура охвачена тестовым контролем. При этом длина теста (в тактах) не должна превышать объема памяти (в адресах).

Устройство работает следующим образом.

В исходном состоянии на вход Э поступают импульсы синхронизации, на вход 8 - импульсы начала теста, кнопка 10 обеспечивает низкий уровень на входе триггера 3. Щупы 7 и 7j: присоединены к исследуемым точкам. В проверяемой аппаратуре циклически выполняется тестовый контроль.

Счетчик каждым импульсом 8 сбрасывается в исходное (нулевое) состояние, а затем пересчитывает синхроимпульсы 9. Триггер 5 находится в состоянии О, тем самым запрещая запись в блоки 1( и 1 памяти. Состояние ос-: тельных узлов произвольно.

Работа устройства начинается с нажатия кнопки 10. При этом потенциал на D-входе триггера 5 переключается с низкого уровня на высокий. По бли(Л

жайшему импульсу 8 триггер 5 переходит в состояние 1 и тем самым устанавливает режим записи через вход блоков Ц и Ij записи, а также производит начальную установку триггеров 3 J, и 3 ошибок. Счетчик k пересчитывает синхроимпульсы 9, тем самым перебирает адреса на входе блоков 1 и

IИнформация с щупов 7 и 7, -отра- каюи4ая состояние в исследуемых точках во время прохождения аппаратного теста , поступает на входы блоков 1 и 1 и записывается в память в качестве эталонов.

Этот процесс протекает многократно в течение времени нажатия кнопки 10. После накопления эталонов устройство готово к анализу сбоев. При отпускании кнопки 10 по ближайшему импульсу 8 триггер 5 переходит в состояние О и снижает режим записи в блоках 1 и 1 j и режим начальной установки в триггерах 3 и 32. Начинается рабочий цик устройства. Счетчик k по импульсам 9 пересчитывает адреса на адресных входах блоков 1 и f. В каждом такте производится чтение из блоков 1 и 1„ и одновременно поступает информа

е. ция

с щупов 7 и 7. Соответствующие

данные сравниваются на схемах 2 2 сравнения.

и

При отсутствии сбоев сравнение происходит в каждом такте, триггеры ошибок не срабатывают, индикаторы не загораются. Циклы контроля проходят непрерывно до тех пор, пока не появит-. ся случайный сбой. В момент появления сбоя на выходе одной из схем 2, 2j, появится сигнал несравнения, который по ближайшему импульсу 9 захлопнется в соответствуюи1ий триггер 3, 3 ошибки и появится на индикационном элемен35

40

Устройство для поиска дефектов логических блоков, содержащее блок памяти, схему сравнения, щуп, индикационный элемент, кнопку Пуск, триггер режима, триггеры ошибки, отличающееся тем, чтО, с целью расширения функциональных возможностей за счет фиксации перемежающихся сбоев и их локализации в цепях с замкнутым контуром воздействий (с обратными связями), в него введены второй блок памяти, вторая схема сравнения, второй щуп, второй индикационный элемент, элемент ИЛИ-Н счетчик адреса памяти, второй тригге ошибки, примем входы данных первого, второго блоков памяти соединены с вы ходами первого, второго щупов соотве ственно, входы синхронизации первого второго блоков памяти соединены с входами синхронизации устройства, входы адреса первого, второго блоков памяти подключены к выходам счетчика адреса памяти, входы управления режи мом работы первого, второго блоков памяти объединены и подключены к выходу триггера режима, выходы первого второго блоков памяти подключены к первым входам первой, второй схем сравнения соответственно, к вторым входам которых подключены выходы пер вого, второго щупов соответственно, выходы Неравно первой, второй схем сравнения соединены с входами данных первого, второго триггеров ошибки соответственно, входы синхронизации первого, второго триггеров ошибки подключены к входу синхронизации уст ройства, входы сброса первого, второ го триггеров ошибки подключены к выходу триггера режима, входы разрешения приема первого, второго триггеро

те 11, 1 la . Одновременно срабатывает ошибки подключены к выходу элемента элемент ИЛИ-НЕ 6, который блокирует прием в триггеры 3 и З.- Это дает .возможность определить точку, где сбой появился раньше, и произвести локализацию места сбоя. При необходимости дальнейшего уточнения источника щупы, и 7, перемещаются по це- производигся более детальный

50

почке и анализ.

ИЛИ-НЕ, первый, второй входы которог подключены к выходам первого, второг триггеров ошибки соответственно, выходы первого, второго триггеров ошиб ки подключены также к первому, второ му индикационным элементам соответственно, вход синхронизации триггера режима подключен к входу синхронизации устройства, вход разрешения запи си триггера режима подключен к входу начала теста устройства, вход данных триггера режима подключены через кнопку Пуск к шине нулевого потенциала, вход синхронизации счетчика

В общем случае каждый канал фиксации сбоев может быть использован независимо, вплоть до диагностики разных узлов в разных устройствах.

Q 5

5

0

0

5

0

Формула изобретения

Устройство для поиска дефектов логических блоков, содержащее блок памяти, схему сравнения, щуп, индикационный элемент, кнопку Пуск, триггер режима, триггеры ошибки, отличающееся тем, чтО, с целью расширения функциональных возможностей за счет фиксации перемежающихся сбоев и их локализации в цепях с замкнутым контуром воздействий (с обратными связями), в него введены второй блок памяти, вторая схема сравнения, второй щуп, второй индикационный элемент, элемент ИЛИ-НЕ, счетчик адреса памяти, второй триггер ошибки, примем входы данных первого, второго блоков памяти соединены с выходами первого, второго щупов соответственно, входы синхронизации первого, второго блоков памяти соединены с входами синхронизации устройства, входы адреса первого, второго блоков памяти подключены к выходам счетчика адреса памяти, входы управления режимом работы первого, второго блоков памяти объединены и подключены к выходу триггера режима, выходы первого, второго блоков памяти подключены к первым входам первой, второй схем сравнения соответственно, к вторым входам которых подключены выходы первого, второго щупов соответственно, выходы Неравно первой, второй схем сравнения соединены с входами данных первого, второго триггеров ошибки соответственно, входы синхронизации первого, второго триггеров ошибки подключены к входу синхронизации устройства, входы сброса первого, второго триггеров ошибки подключены к выходу триггера режима, входы разрешения приема первого, второго триггеров

ошибки подключены к выходу элемента

ИЛИ-НЕ, первый, второй входы которого подключены к выходам первого, второго триггеров ошибки соответственно, выходы первого, второго триггеров ошибки подключены также к первому, второму индикационным элементам соответственно, вход синхронизации триггера режима подключен к входу синхронизации устройства, вход разрешения записи триггера режима подключен к входу начала теста устройства, вход данных триггера режима подключены через кнопку Пуск к шине нулевого потенциала, вход синхронизации счетчика

516052376

адреса памяти соединен с входом син- вход и вход сброса соединены с вхо- хронизации устройства, а счетный дом начала теста устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1456996A1 |

| Устройство для отладки и контроля хода программ | 1989 |

|

SU1691843A2 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля и диагностики. Цель изобретения - расширение функциональных возможностей за счет фиксации перемежающихся сбоев и их локализации в цепях с замкнутым контуром воздействий (с обратными связями). Устройство содержит два блока памяти, две схемы сравнения, два триггера ошибок, два щупа, два индикационных элемента, счетчик адреса памяти, триггер режима, кнопку "ПУСК", элемент ИЛИ-НЕ. 1 ил.

S

I

тзг С

т

с

12

ill

2, t

21 Иг

С

-I

Фл1

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1277117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ подключения аккумуляторной батареи для ее заряда на электрическом подвижном составе | 1955 |

|

SU122165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1988-12-21—Подача