Изобретение относится к вычисли - тельной .технике и может быть исполь- зовано в постоянном запоминающем устройстве.

Целью .изобретения является повьше- ние выхода годных матричного накопи- . теля.

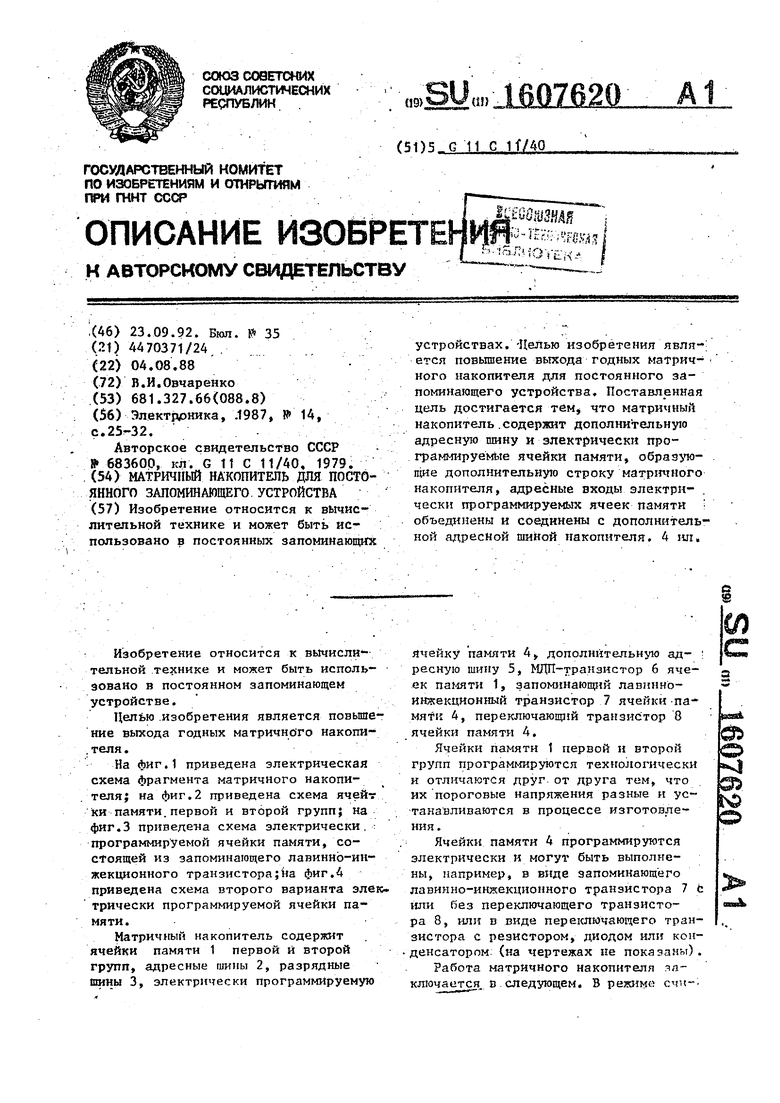

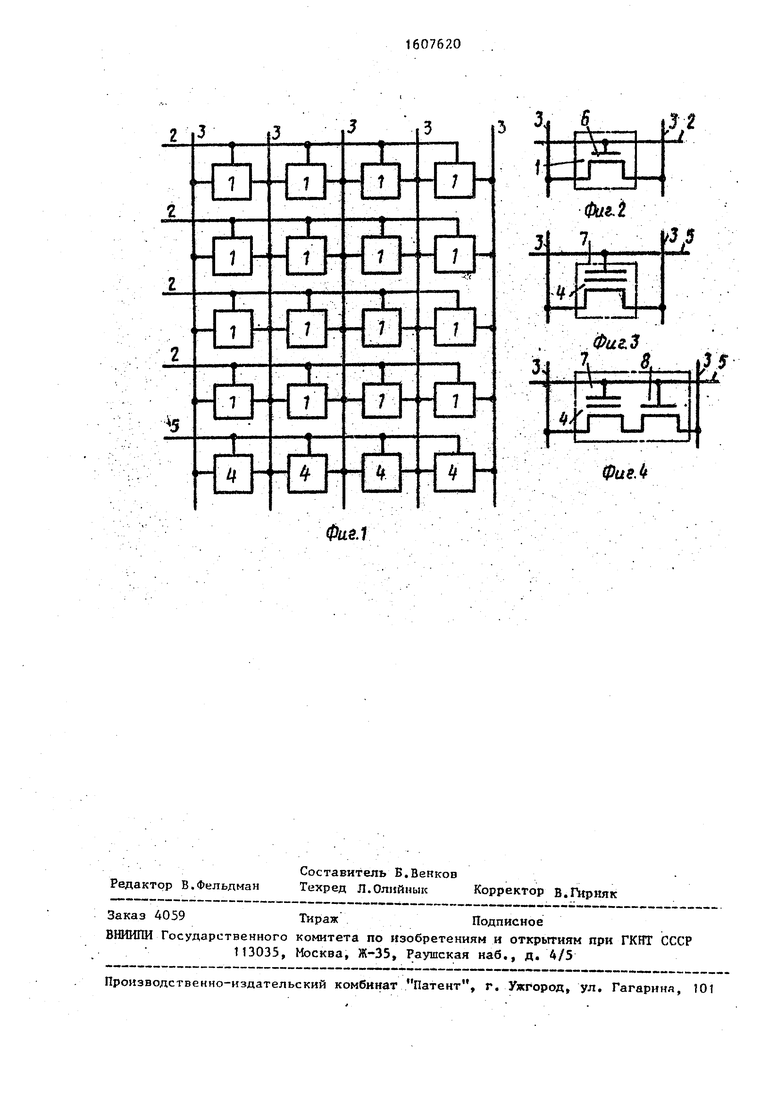

На фиг.1 приведена электрическая схема фрагмента матричного накопителя; на фиг.2 приведена схема ячейт ки памяти.первой и второй групп; на фиг.З приведена схема электрически. : программируемой ячейки памяти, состоящей из запоминающего лавинно-ин- жекционного транзистора;йа фиг.4 приведена схема второго варианта элев трически программируемой ячейки памяти.

Матричный накопитель содерлсит ячейки памяти 1 первой И второй групп, адресные шины 2, разрядные шины 3, электрически программируемую

Ячейку памяти 4, дополнительную ад- ; ресную шину 5, МДП-транзистор 6 ячеек памяти 1, запоминающий лавинно- инзкекционный транзистор 7 ячейки памяти 4, переключающий транзистор 8 ячейки памяти 4.

Ячейки памяти 1 первой и второй групп программируются технологически и отличаются друг, от друга тем, что их пороговые напряжения разные и устанавливаются в процессе изготовления.

Ячейки памяти 4 программ1фуются электрически и могут быть выполнены, итпример, в виде запоминающего лавинно-инжекционного транзистора 7 с или без переключающего транзистора 8, или в виде пере1шючающего транзистора с резистором, диодом или кон- денсатором. (на чертежах не показаны).

Работа матричного накопителя яа- ключается, в. следующем. В режиме

Ю

ri- Bntit-in и формации на адресную шину . подлюг низкое псхпожит льмое напряжение, на остальные шипы 2 ну- петзое иатфяжение. На выбра П1Ые разрядные ршны 3 подают низкое Положн- тельное напряжение, а на соседние выбранные птны 3 - пулевое напряже- ime, на остальные разрядные шшы 3 низкое положительное нгзпряжение. Ёс ли пороговое напряжение транзистора 6 ячейки памяти 1 низкое, то через него протекает ток что эквивалентно еднннчкому состоянию. Если пороговое напря-жение транзистора 6 выс.о- KOBf то через него не протекает ток, что эквяйалентло нулево гу состоянию,

Если при проверке работоспособности матричного накопителя будет установлено Нйличие дефектной строки ячеек памяти I, то оНа заменяется строкой из ячеек памяти 4 программя- pyet-ibix электрически, исходные состо™ яния которых эквипалентны единично™. му

Лпя этого rta дополнительную адресную гшну 5 подают высокое положительное напряжение, на остальные адресные шины . подают нулевое на- пряжение. Для перевода в нулевое co стояние ячеек памяти А на выбранну}о разрядную пшну 3 подают высокое на- пряжение, на соседнюю выбранную шину 3 нулевое напряжение а па ос- тальнг те шины 3 низкое положительное напряжение. Под дейстншем высокого напряжения на стоке выбранного запоминающего транзистора 7 через него протекает канальный ток, вызываю- пц-1й инжекцию электронов из канала и захват их плавающим затвором. Это приводит с высокому пороговому напряжению выбранного запоминающего транзистора 7, что эквивалентно ну-

левому состоянию в режиме считывания.

Введение дополнительной адресной пмны и строки электрически програм- 1-1Ируемых ячеек памяти позволяет при незначительном увеличении площади накопителя повысить выход годйых накопителя.

L

Формула изобретения,

Матричный накопитель для постоянного зйпокинаюгцего устройства, содержавдй адресные и разрядные шинм, в перекрестиях которых расположены ячейки памяти первой и второй групп, адресные входы ячеек памяти первой и второй групп, образующие .; .

матричного Накопителя, объединены и соединены с адресной тиной накопите- ля, первые и вторые информациоиньге выводы ячеек памяти первой и нто - рой групп, образующие .нечетйый ctdJtбец матричного накопителя объединены и Соединены соответствеино с нечетной и четной Jpaзpядными шИнамИ первые и вторые информационные вЫ1ао- ды ячеек памяти первой и второй :

групп, образуюп(Ие четный столбец трИчного накопителя, объединены и со единены соответственно с четной и-не, четной разрядными шинами матричного накопителя, от л и ч а ю щи и с я

тем, что, с целью повьйления выхода годных матричного накопителя, он содержит дополнительную адреску Шину и электрически программируемые . ячейки памяти, образугошдедополнительную строку матричного накопите- лп, адресные входы электрически про граммируемых ячеек памяти объединены и соединены с дополнительной адресной шиной матричного накопителя.

Изобретение относится к вычислительной технике и может быть использовано в постоянных запоминающих устройствах. Целью изобретения явля-; ется повышение выхода годных матричного накопителя для постоянного запоминающего устройства. Поставленная цель достигается тем что матри щый накопитель .содержит дополнительную адресную шину и электрически про- граммируемьте ячейки памяти, образ то- щие дополнительную строку матрштного накопителя, адресные входы электрически программируемых ячеек памяти объединены и соединены с дополнительной адресной шиной накопителя. 4 шх.

ФиёЛ

Фа1.г

ФиеЛ

| Электроника, .1987, № 14, С.25Г-32. | |||

| Авторское свидетельство СССР 683600, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1992-09-23—Публикация

1988-08-04—Подача