05

о

00

ГС

00

Изобретение относится к технике об рг ботки и передачи информации и может быть использовано в измерительной технике, автоматике и телеметрии для сжатия данных.

Цель изобретения - повышение точности устройства путем аппроксимации входного сигнала полиномом второго порядка.

Указанная цель достигается тем, что в устройство, содержащее счетчик аналого-цифровой преобразователь, арифметический блок, два накапливающих сумматора, регистр, блок сравне- ния| введены блок управления, блок ключей, комбинационный сумматор.

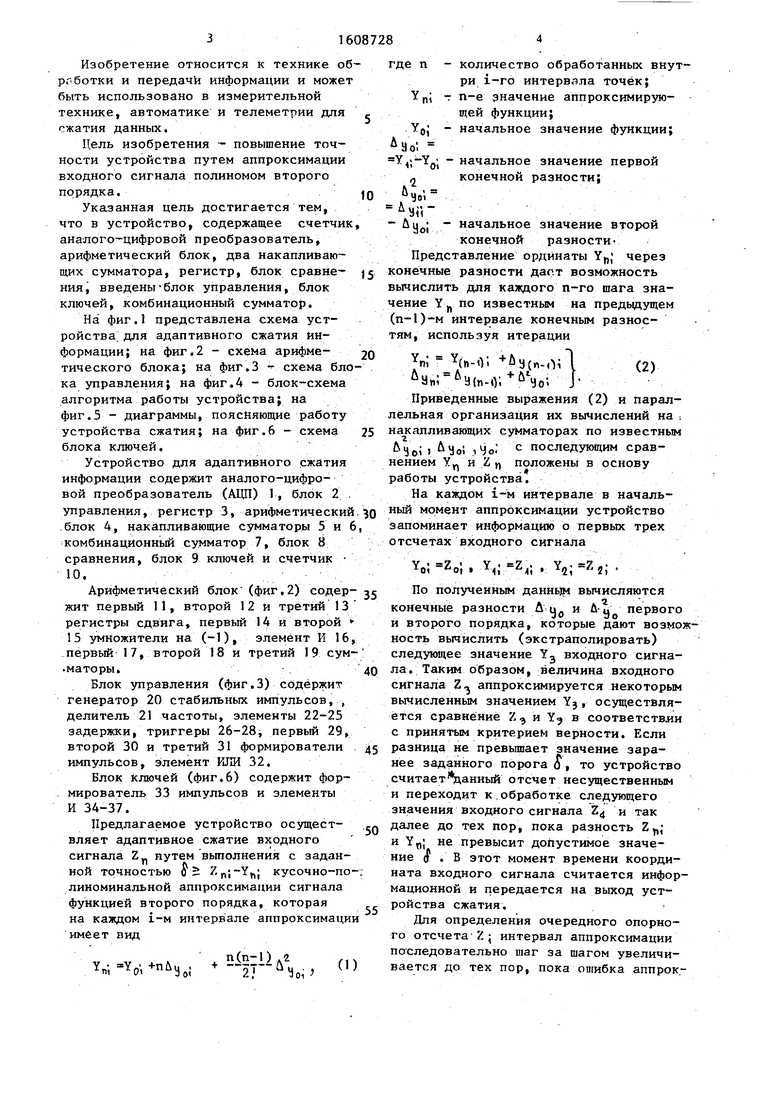

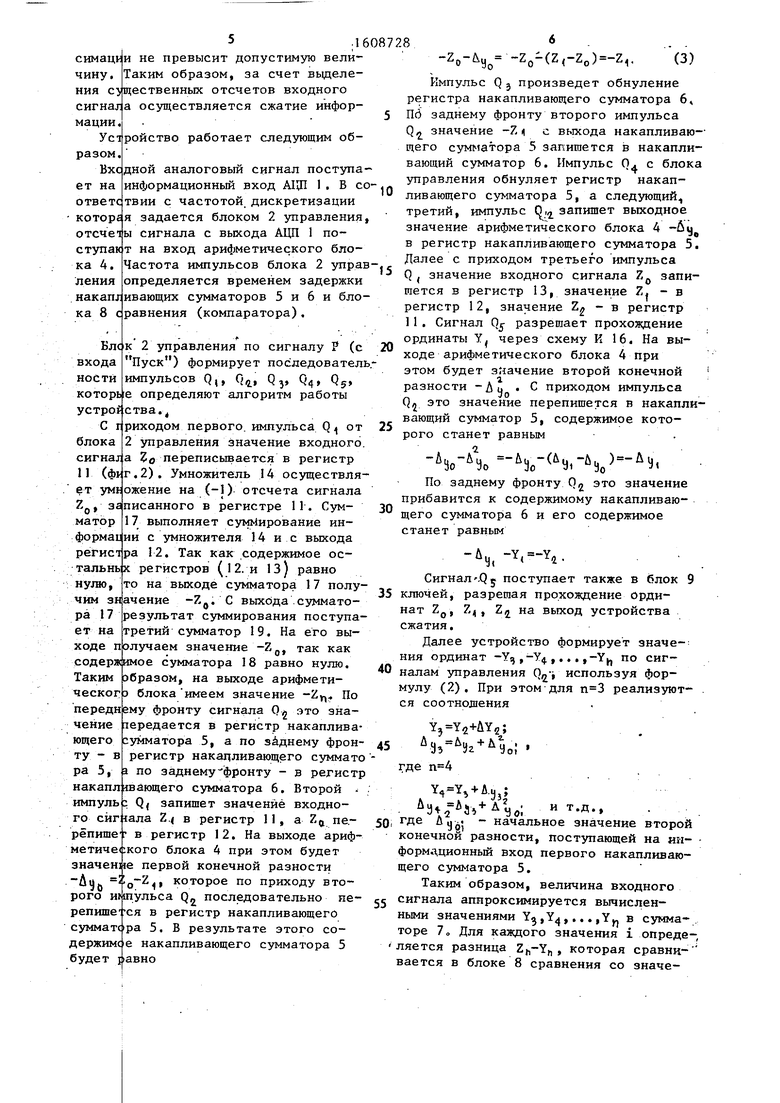

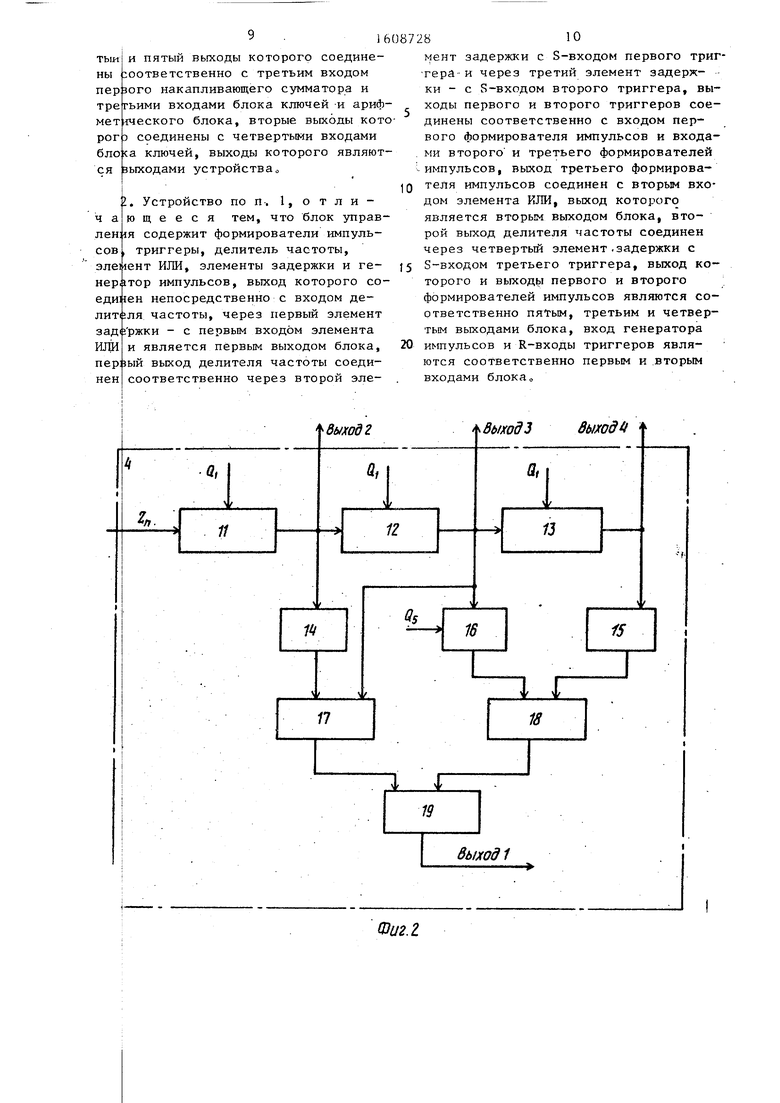

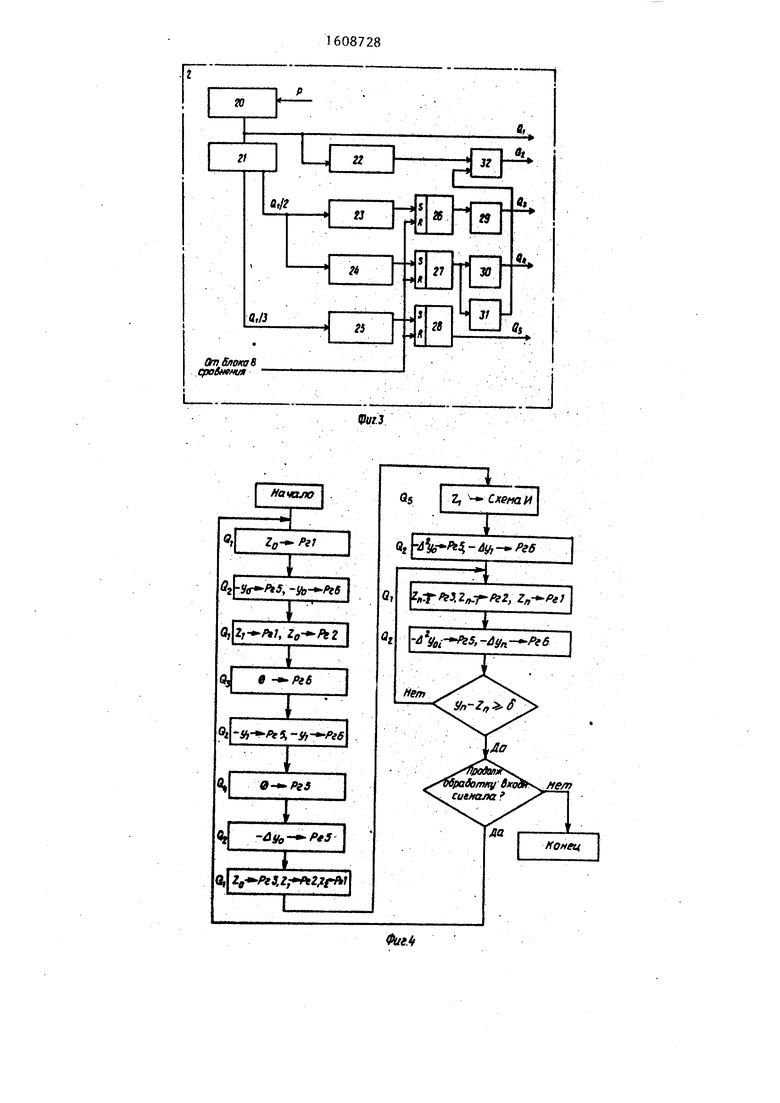

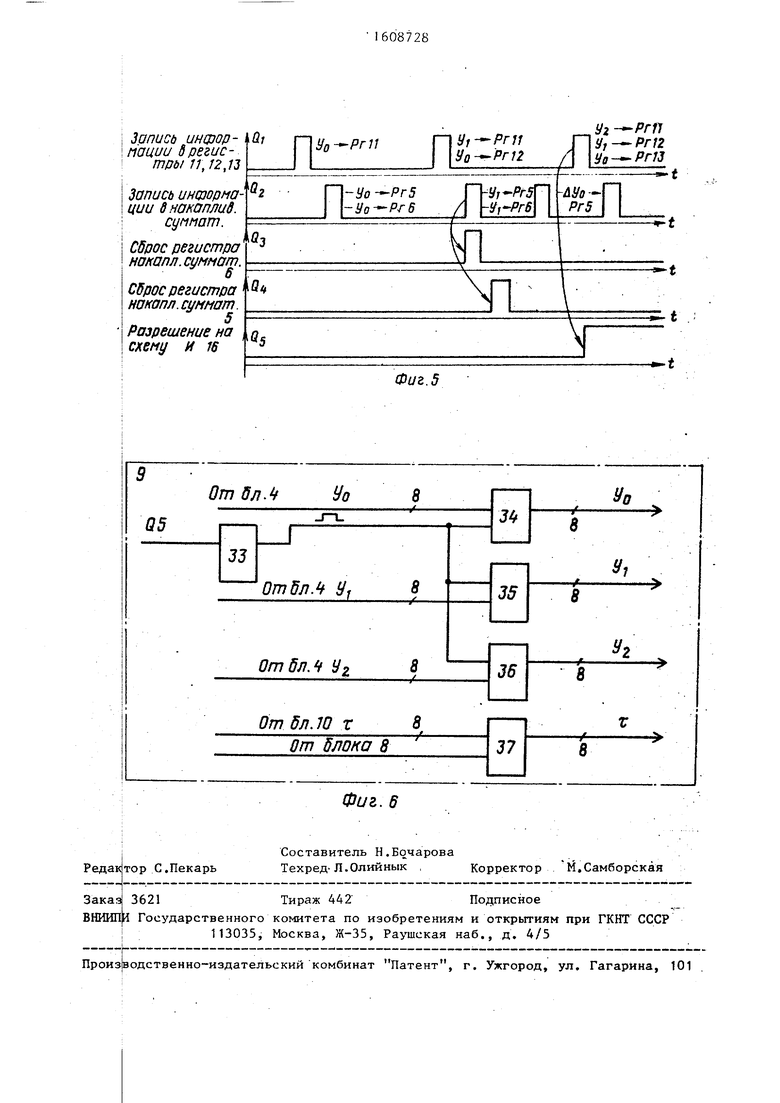

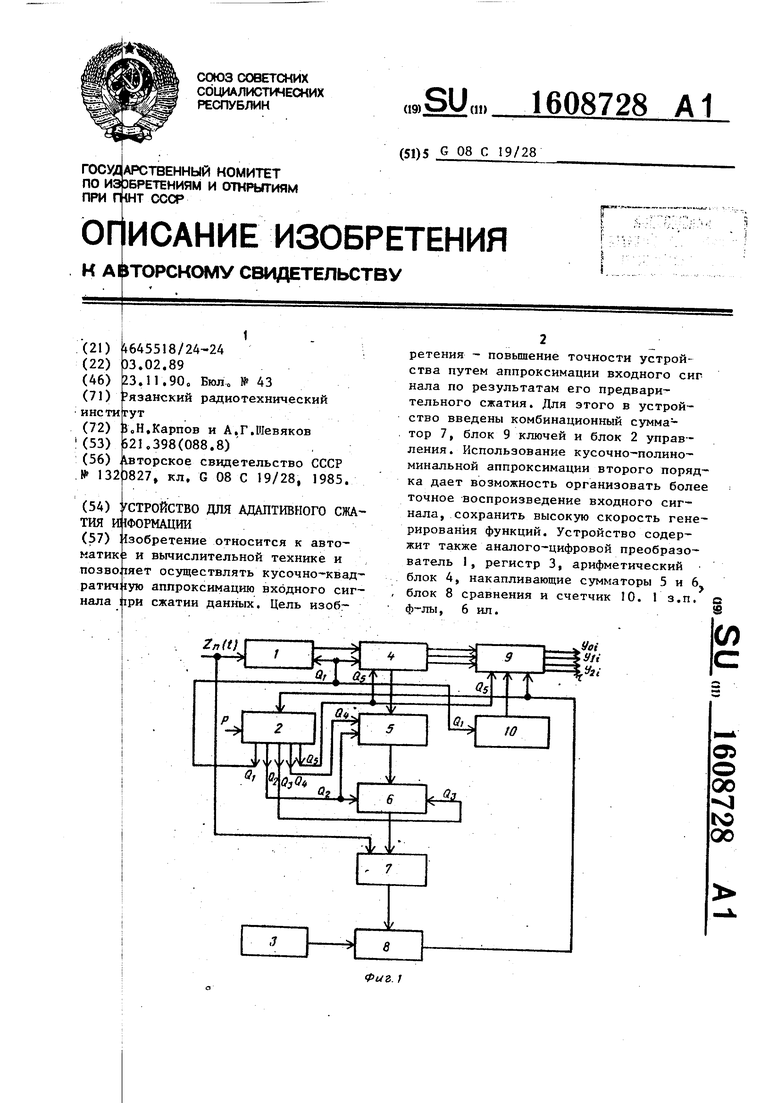

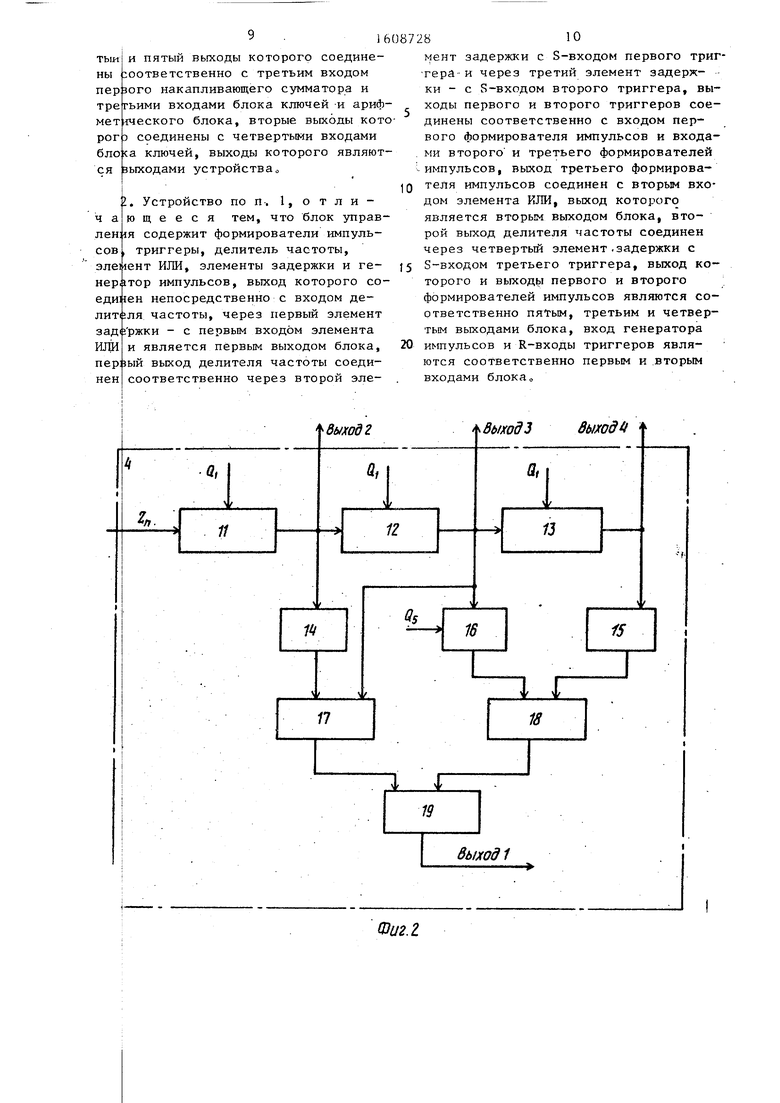

На фиг.1 представлена схема устройства, для адаптивного сжатия информации; на фиг.2 - схема арифме- тического блока; на фиг.З - схема бло ка управления; на фиг.4 - блок-схема алгоритма работы устройства; на фиг.5 - диаграммы, поясняющие работу устройства сжатия; на фиг.6 - схема блока ключей.

Устройство для адаптивного сжатия информации содержит аналого-цифровой преобразователь (АЦП) 1, блок 2 . управления, регистр 3, арифметический блок 4, накапливающие сумматоры 5 и 6 комбинационный сумматор 7, блок 8 сравнения, блок 9 ключей и счетчик 10.

Арифметический блок (фиг.2) содер- жит первый 11, второй 12 и третий 13 регистры сдвига, первый 14 и второй 15 умножители на (-1), элемент И 16, первый 17, второй 1В и третий 19 сум.маторы.

Блок управления (фиг.3) содержит генератор 20 стабильных импульсов, , делитель 21 частоты, элементы 22-25 задержки, триггеры 26-28 первый 29, второй 30 и третий 31 формирователи импульсов, элемент ИЛИ 32.

Блок ключей (фиг.6) содержит фор- . мирователь 33 импульсов и элементы И 34-37.

Предлагаемое устройство осущест- вляет адаптивное сжатие входного сигнала Z путем выполнения с заданной точностью 0 7. кусочно-полиноминальной аппроксимации сигнала функцией второго порядка, которая на каждом i-м интервале аппроксимации имбет вид

, п(п-1) .2

,;-bn,

21

(1)

где п - количество обработанных внури i-ro интервала точек;

Yp; т п-е значение аппроксимирующей функции;

Yjj - начальное значение функции;

А 9 о -

Y,;-Yg; - начальное значение первой л конечной разности;

4i

Ау--

Уо начальное значение второй

конечной разности- Представление ординаты Yf,; через конечные разности даст возможность вычислить для каждого п-го шага значение Y по известным на предьщущем (n-l)-M интервале конечным разностям, используя итерации

П)

()-О

асп-оД -.) )

Приведенные выражения (2) и параллельная организация их вычислений на ; накапливающих сумматорах по известным Чо1 I Чо; i4o; с последующим сравнением Yy и Z Y положены в основу работы устройства.

На каждом i-м интервале в начальный момент аппроксимации устройство запоминает информацию о первых трех отсчетах входного сигнала

, Y,,;, .

По полученным данным вычисляются конечные разности Л ц и Л-ц первого и второго порядка, которые дают возмоность вычислить (экстраполировать) следующее значение Y.J входного сигнала. Таким образом, величина входного сигнала Z аппроксимируется некоторым вычисленным знач;ением Yj , осуществляется сравнение Z и Y в соответствии с принятым критерием верности. Если разница не превьшает значение заранее заданного порога о, то устройство считает цанный отсчет несущественным и переходит к.обработке следующего значения входного сигнала Z4 и так далее до тех пор, пока разность и Y,; не превысит допустимое значение о . В этот Момент времени координата входного сигнала считается информационной и передается на выход устройства сжатия.

Для определения очередного опорного отсчета Z; интервал аппроксимации по следовательно шаг за шагом увеличивается до тех пор, пока ошибка аппрок5.160

симацйи не превысит допустимую величину. Таким образом, за счет выделения существенных отсчетов входного сигнала осуществляется сжатие информации

YcilpoftcTBO работает следующим образом

Вхс1дной аналоговый сигнал поступает на информационный вход А1Щ 1. В со- ответствии с частотой, дискретизации которая задается блоком 2 управления, отсчеты сигнала с выхода АЦП 1 по- ступакт на вход арифметического бло

ка 4. Частота импульсов блока 2 управления определяется временем задержки накапливающих сумматоров 5 и 6 и блока 8 сравнения (компаратора).

к 2 управления по сигналу Р (с Пуск) формирует последовател импульсов Q,, Q, Qj, Q, Q, e определяют алгоритм работы

QI от

Блс входа ностй которь ycTpof ства.

С гриходом первого, импульса блока 2 управления значение входного сигнала Zo переписывается в регистр 11 (ф1- г. 2) . Умножитель 14 осуществля ет умножение на (-1) отсчета сигнала Zp, записанного в регистре 11. Сумматор 17 выполняет суммирование ин- формаиии с умножителя 14 и с выхода регистра 12. Так как содержимое остальных регистров ( 1 2. и 13) равно HyjBo, то на выходе сумматора 17 получим значение -Z. С выхода сумматора 17 результат суммирования поступает на третий сумматор 19. На его выходе получаем значение -Z.., так как

о

содержимое сумматора 18 равно нулю.

Таким

образом, на выходе арифметическогэ блока имеем значение -Zy,, По

ему фронту сигнала Q это зна- ередается в регистр накаплива

вающего сумматора 6, Второй

сумматора 5, а по заднему фрон- 45

Далее устр ния ординат налам управле мулу (2). При ся соотношени

Y5 Y2+UY2

регистр накапливающего суммато - 1 по заднему фронту - в регистр

Эз- Уг- где

; Q( запишет значение входно1ала Z. в регистр 11, а Z пе- fd

в регистр 12. На выходе арифкого блока 4 при этом будет е первой конечной разности

+ A.

а

а

b . + Л

5.

4oi

- н

которое по приходу втопульса р„ последовательно пеконечной разн формд,ционный щего сумматор

Таким обра 55 сигнала аппро ными значения торе 7„ Для к ляется разниц вается в блок

репише сумматс держимс будет I

ся в регистр накапливающего ра 5. В результате этого со- е накапливающего сумматора 5 авно

-Zp-uy -Zo-(Z,,.

(3)

0

Импульс Q J произведет обнуление регистра накапливающего сумматора 6, П6 заднему фронту второго импульса Q значение -Z ц с выхода накапливающего сумматора 5 запишется в накапливающий сумматор 6. Импульс Од с блока управления обнуляет регистр накапливающего сумматора 5, а следующий, третий, импульс Ог. запишет выходное значение арифметического блока 4 -йу

5

0

5

в регистр накапливающего сз мматора 5. Далее с приходом третьего импульса Q , значение входного сигнала 7. запишется в регистр 13, значение Z. - в регистр 12, значение Zj - в регистр 11. Сигнал QJ разрешает проховдение ординаты Y через схему К 16. На выходе арифметического блока 4 при этом будет з: ачение второй конечной разности Ль .С приходом импульса Qj это значение перепишется в накапливающий сумматор 5, содержимое которого станет равным

- yo- Ni-So

30

По заднему фронту Og это значение прибавится к содержимому накапливающего сумматора 6 и его содержимое станет равным

-Лу, -Y,Сигнал .Q 5 поступает также в блок 35 ключей, разрешая прохождение ординат ZQ, Z, Zj на выход устройства

сжатия.

40

45

Далее устройство формирует значе-: ния ординат Y, ,-Y4.,... ,-Yj, по сигналам управления используя формулу (2). При этом для реализуются соотношения

Y5 Y2+UY2;.

Эз- Уг- чс,;

где

d

+ A.

а

аз|

b . + Л V

5.

4oi

и т.д., - начальное значение второй

конечной разности, поступающей на ии- формд,ционный вход первого накапливающего сумматора 5.

Таким образом, величина входного 5 сигнала аппроксимируется вычисленными значениями Y5,Y4,...,Y в сумматоре 7„ Для каждого значения i опреде-, ляется разница Zh-Yft , которая сравни- вается в блоке 8 сравнения со значе

нием заранее заданного выполняется условие отсчет считается не и происходит обработка значения входного сигна делее до тех пор, пока

Ч-v.bS.

при выполнении этого условия в блоке 8 сравнения вырабатьгоается сигнал сравнения. На выход устройства сжатия передается информация об интервале времени между двумя участками аппроксимации Ъ , и текзпцая ордината входного сигнала считается существенной , Схема блока 2 зшравления при этом приводится в исходное состоя- ние и работа устройства сжатия повторяется по описанному алгоритму.

Серии импульсов Q,,...,Q5 выраба- ьшаются в блоке 2 управления.

По сигналу Р (Пуск) схема блока 2 управления приводится в исходное состояние. Последовательность импульсов Q с выхода генератора 20 служит для записи информации в регистры 11-13, Эти же импульсы Q/ являются исходными для получения серии Qj, которая управляет записью в регистры накапливающих сумматоров 5 и 6. Серия О 2 снимается с выхода элемента ШШ 32. Выходные сигналы с делителя 21 частоты поступают на элементы 23-25 задержки импульсов, причем на элементы 22 и 23 поступает серия Qj, поделенная на два, а на элемент 24 - серия Q, поделенная на три. Импульсы с элементов 23-25 задержки поступают на установочные входы триггеров 26-28, изменяя их состояние на противоположное. С выхода третьего триггера 28 получаем потенциальный сигнал Q J., который служит для стробирова- ния элемента И 16. С выхода первого и второго триггеров 26 и 27 потенциалы поступают на формирователи импульсов 29 и 30, с выхода которых имеен последовательности импульсоо Q J и О., следующие для сброса регистров накапли-- вающих сумматоров 3 и 6. Сброс триггеров 26-28 в исходное состояние происходит по сигналу с выхода блока 8 сравнения, который завершает аппроксимацию очередного участка. На новом участке аппроксимации работа блока управления повторяется в соответствии с алгоритмом фиг.А),

8728

0

5

5

0

5

0

5

0

5

8

Выходы блока 9 ключей одновременно являются выходами устройства ежа-, тия. Из. четырех выходов три служат для передачи информации о первых трех отсчетах , , Y2; каждого интервала аппроксимащ1и, а один - для передачи информации о текущем интервале времени между двумя последовательными интервалами аппроксимации с .

Количество элементов И блока ключей будет зависеть от разрядности входной информации (в данном случае поступает восьмиразрядный код).

Счетчик 10 (фиг.1) представляет собой обычный суммирующий счетчик, который служит для выдачи информации об интервале времени между двумя последовательными участками аппроксима- ции - .

Формула изобрете ни я

1. Устройство для адаптивного сжатия информации, содержащее аналого- цифровой преобразователь, первый вход которого является информационным входом устройства, выход соединен с первым входом арифметического блока, первый рыход которого соединен с первым входом первого накапливающего сумматора, выход которого соединен с первым входом второго накапливающего сз мматора, регистр, выход которого соединен с первым входом блока сравнения, и счетчик, о т ли чающее- с я тем, что, с целью повьппения точности устройства, в него введены комбинационный сумматор, блок ключей и блок управления, первый вход которого является входом Пуск устройства, первый выход блока управления соединен с вторыми входами аналого-цифрового преобразователя и арифметического блока и входом счетчика, выход которого соединен с первым входом блока кАючей, второй и третий выходы блока управления соединены-соответственно с вторыми входами первого и второго накапливающих сз маторов и с третьим входом второго накапливающего сумматора, выход которого соединен с первым входом комбинационного сумматора, второй вход которого подключен к информационному входу устройства, выход соединен с вторым входом блока сравнения, выход блока Сравнения соединен с вторыми входами бло- ка ключей и блока управления, четверТЬ1И

ны пер

и пятый выходы которого соедине- :оответственно с третьим входом зого накапливающего сумматора и

мет рог

третьими входами блока ключей-и ариф- етеского блока, вторые выходы котоэ соединены с четвертыми входами

блоча ключей, выходы которого являются

зыходами устройства.

ч а лен: сов

I. Устройство по п. 1, ю щ е е с я тем, что

о т л и - блок управ1Я содержит формирователи импультриггеры, делитель частоты, элемент ИЛИ, элементы задержки и генератор импульсов, выход которого соединен непосредственно с входом де- лит(шя частоты, через первый элемент зад«фжки - с первым входом элемента ШШ и является первым выходом блока, пер:}ый выход делителя частоты соединен соответственно через второй элемент задержки с S-входом первого триг- гера и через третий элемент задержки - с S-входом второго триггера, выходы первого и второго триггеров соединены соответственно с входом первого формирователя импульсов и входами второго и третьего формирователей импульсов, выход третьего формирователя импульсов соединен с вторым входом элемента ИЛИ, выход которого является вторым выходом блока, второй выход делителя частоты соединен через четвертый элемент.задержки с

S-входом третьего триггера, выход которого и выходы первого и второго формирователей импульсов являются соответственно пятым, третьим и четвертым вькодами блока, вход генератора

импульсов и R-входы триггеров явля- ются соответственно первым и вторым входами блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1388896A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1709355A1 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Устройство для вычисления тригонометрических и гиперболических функций | 1983 |

|

SU1113798A1 |

| Устройство для определения производной структурной функции | 1986 |

|

SU1355978A1 |

| Коррелометр | 1983 |

|

SU1091173A1 |

Изобретение относится к автоматике и вычислительной технике и позволяет осуществлять кусочно-квадратичную аппроксимацию входного сигнала при сжатии данных. Цель изобретения - повышение точности устройства путем аппроксимации входного сигнала по результатам его предварительного сжатия. Для этого в устройство введены комбинационный сумматор 7, блок 9 ключей и блок 2 управления. Использование кусочно-полиноминальной аппроксимации второго порядка дает возможность организовать более точное воспроизведение входного сигнала, сохранить высокую скорость генерирования функций. Устройство содержит также аналого-цифровой преобразователь 1, регистр 3, арифметический блок 4, накапливающие сумматоры 5 и 6, блок 8 сравнения и счетчик 10. 1 з.п. ф-лы, 6 ил.

выход 2

л.

11

14

17

ВыходЗ

Bbixodfi

fl,

1

12

/J

/5

18

3

19

Выход 1

(Ои2.г

Фиг.. 6

PeflaidTop С.Пекарь

3

Составитель Н.Бочарова

Техред-Л.Олийнык , Корректор М.Самборская

Заказ

3621

Тираж 442

ВНИИПЯ Государственного комитета по изобретениям и открытиям при ГКНТ СССР I 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Способ получения нерастворимых лаков основных красителей в субстанции и на волокнах | 1923 |

|

SU132A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-11-23—Публикация

1989-02-03—Подача