Изобретение относится к технике автоматического управления и может быть использовано для управления технологическим процессом переработки пластмасс методом литья под давлением в химической промышленности, машиностроении и является усовершенствованием известного устройства, описанного в авт. св. № 1164056

Устройство содержит датчик осевого положения червяка, датчик давления, установленные на корпусе литьевой машины, блок ввода и индикации, блок обработки входных сигналов и блоки управления исполнительными механизмами, причем оно включает также датчик давления материала в форме, датчик частоты вращения

червяка, вычислитель с энергонезависимой памятью для хранения программ и данных, блоки аналого-цифрового преобразования, формирования временных выдержек, сопряжения с центральной ЭВМ, объединенных между собой, а также с блоками ввода и индикации, обработки входных сигналов и управления исполнительными механизмами программно-управляемым интерфейсом, причем выходы датчиков давления и частоты вращения соединены с блоком аналого- цифрового преобразования, выход датчика осевого положения червяка соединен со входом блока обработки входных сигналов, а выходы блоков управления - с исполнительными механизмами.

О5

о со о: со |

ГЧ)

Регулирование температуры зон обогрева материального цилиндра в данном устройстве осуществляется с помощью автономных одноканальных регуляторов. Это не позволяет осуществить многопараметровое управление процессом литья, так как устройство управления не имеет доступа к информации о температурном режиме материального цилиндра. Невозможна также полная установка параметров процесса с

мого интерфейса, счетные -входы - с выходом генератора прямоугольных импульсов, выходы - со входами установки в «О выходных триггеров, а информационные входы и стробирующий вход дешифратора номера канала связаны соответственно с шинами адреса и управления памятью второго программно-управляемого интерфейса, выходы - со входами установки широтно-импульсных модуляторов и

цёнтральшй ЭВМ, так как для установкиЮ входами установки в «1 выходных тригтемпературы зон обогрева материальногогеров, выходы которых связаны с соответцилиндра требуются дополнительные мани-ствующими входами блока тиристорных

пуляции с задатчиками на регуляторахключей.

температуры в каждой зоне. Кроме того,Блок межпроцессорной связи содержит

отсутствие информации о температурном ре-15 дешифратор доступа, триггер управления

жиме при автоматической работе литьевой- ,„.,„

машины может привести к бракованным изделиям, а также к поломкам червяка

и материального цилиндра во время выполнения операций по набору дозы и впрысдоступом, программно-доступные первому вычислителю триггер запроса захвата и регистр ввода, расширитель шины адреса, двунаправленный расширитель шины данных,

.. -,п расширитель шины управления памятью

ку при непредвиденном снижении темпера- |.,рдрра„м„о-доступный второму вычислите- туры материального цилиндра.j, регистр ввода, первый и второй эле

Целью изобретения яЕ Ляется расширение функциональных возможностей устройства по управлению процессом литья под давлением изделий из пластмасс.

Поставленная цель достигается тем, что устройство управления литьевой машиной дополнительно содержит связанный посредством блока межпроцессорной связи многоканальный регулятор температуры зон обогрева материального цилиндра, включающий датчики температуры, блок тиристорных ключей и нагревательные элементы, а также объединенные вторым программ-, по-управляемым интерфейсом второй вычислитель, второй блок аналого-цифрового преобразования, входы которого связаны с выходами датчиков температуры и блок управления обогревом, выходы которого через блок тиристорных ключей связаны с нагревательными элементами. Первые информенты И, причем информационные входы дешифратора доступа и расширителя шины адреса, первые информационные входы - 25 выходы расширителя шины данных, триггер запроса захвата и регистр ввода, информационные входы расширителя шины управления памятью связаны соответственно с шинами адреса, данных и управления памятью первого программно-управляемого интерфейса первого вычислителя, информационные входы расширителя шины адреса, вторые информационные входы - выходы расширителя шины данных и регистр ввода, информационные выходы расшири30

второй бло7 на;о,Гцифров ого 35 -- ь, управления памятью связаны

ьтрип vv-.ijn-тг JO „..„„..„...„.„„....г г П1ННЯМИ ЯЛПРГЯ. ШННЫХ

соответственно с шинами адреса, данных и управления памятью второго программно- управляемого интерфейса второго вычислителя, управляющие входы расширителей шины адреса и шины данных связаны с вынагревательными элементами, иерьые HHipup- - -«,.. - -- -,,оппя«

мационные входы - выходы блока меж- 40 ходом дешифратора доступа, вход направiVl 3 un ппи1 ил лл.и„,o.-io,r.j ттгчытс: па ni ы U1-.I ;i я М процессорной связи соединены с первым программно-управляемым интерфейсом первого вычислителя, вторые - со вторым программно-управляемым интерфейсом втоления передачи расширителя шины данных - с первым информационным входом расширителя шины управления памятью, управляющие входы дешифратора доступа

7ь :с;„Г;я Г..Г группа управ- ,, « расшир ™, ™,.ь, ,пра.,„,,„ ,ьк,

„,-, „.r.n/M i прпвые входы КОТОРОГО первою элемент

ляющих сигналов - с первой группой управляющих входов -- выходов первого вычислителя, вторая - со второй группой управляюпхих входов - выходов второго вычислителя.

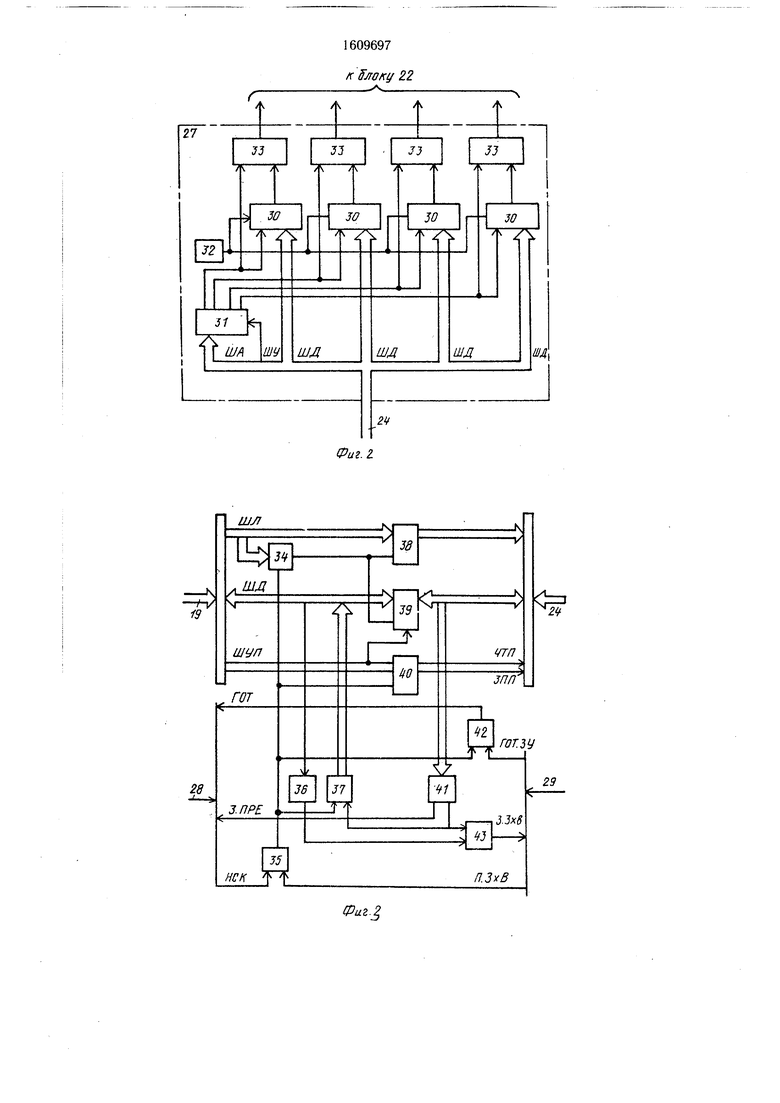

Блок управления обогревом содержит по крайней мере четыре широтно-импульсных модулятора, дешифратор номера канала, генератор прямоугольных импульсов п выходные триггеры, количество которых равно количеству широтно-импульсных модуляторов, причем информационные входы пирот- но-импульсных модуляторов связаны с шиной данных второго программно-управляепервые входы которого первого элемента И и регистра ввода - с выходом триггера управления доступом, первый вход второго элемента И и второй вход регистра ввода - со вторым выходом реCQ гистра вывода, второй вход второго элемента И - с выходом триггера запроса захвата, выход первого элемента И, первый выход регистра вывода и установочный вход триггера управления доступом - с первой группой управляющих

55 входов - выходов первого вычислителя, второй вход первого элемента И, выход второго элемента И и информационный вход триггера управления доступом -- со

мого интерфейса, счетные -входы - с выходом генератора прямоугольных импульсов, выходы - со входами установки в «О выходных триггеров, а информационные входы и стробирующий вход дешифратора номера канала связаны соответственно с шинами адреса и управления памятью второго программно-управляемого интерфейса, выходы - со входами установки широтно-импульсных модуляторов и

входами установки в «1 выходных тригдешифратор доступа, триггер управления

- ,„.,„

доступом, программно-доступные первому вычислителю триггер запроса захвата и регистр ввода, расширитель шины адреса, двунаправленный расширитель шины данных,

расширитель шины управления памятью

|.,рдрра„м„о-доступный второму вычислите- j, регистр ввода, первый и второй эле

менты И, причем информационные входы дешифратора доступа и расширителя шины адреса, первые информационные входы - 25 выходы расширителя шины данных, триггер запроса захвата и регистр ввода, информационные входы расширителя шины управления памятью связаны соответственно с шинами адреса, данных и управления памятью первого программно-управляемого интерфейса первого вычислителя, информационные входы расширителя шины адреса, вторые информационные входы - выходы расширителя шины данных и регистр ввода, информационные выходы расшири30

35 -- ь, управления памятью связаны

-- ь, управления памятью связаны

„..„„..„...„.„„....г г П1ННЯМИ ЯЛПРГЯ. ШННЫХ

соответственно с шинами адреса, данных и управления памятью второго программно- управляемого интерфейса второго вычислителя, управляющие входы расширителей шины адреса и шины данных связаны с вы- -«,.. - -- -,,оппя«

ходом дешифратора доступа, вход направходом дешифратора доступа, вход направ„,o.-io,r.j ттгчытс: па ni ы U1-.I ;i я М ления передачи расширителя шины данных - с первым информационным входом расширителя шины управления памятью, управляющие входы дешифратора доступа

« расшир ™, ™,.ь, ,пра.,„,,„ ,ьк,

, « расшир ™, ™,.ь, ,пра.,„,,„ ,ьк,

прпвые входы КОТОРОГО первою элемент

первые входы которого первого элемента И и регистра ввода - с выходом триггера управления доступом, первый вход второго элемента И и второй вход регистра ввода - со вторым выходом реCQ гистра вывода, второй вход второго элемента И - с выходом триггера запроса захвата, выход первого элемента И, первый выход регистра вывода и установочный вход триггера управления доступом - с первой группой управляющих

55 входов - выходов первого вычислителя, второй вход первого элемента И, выход второго элемента И и информационный вход триггера управления доступом -- со

второй группой управляющих входов - вы-сом 24 второго вычислителя 25, первая

ходов второго вычислителя.группа управляющих сигналов - с первой

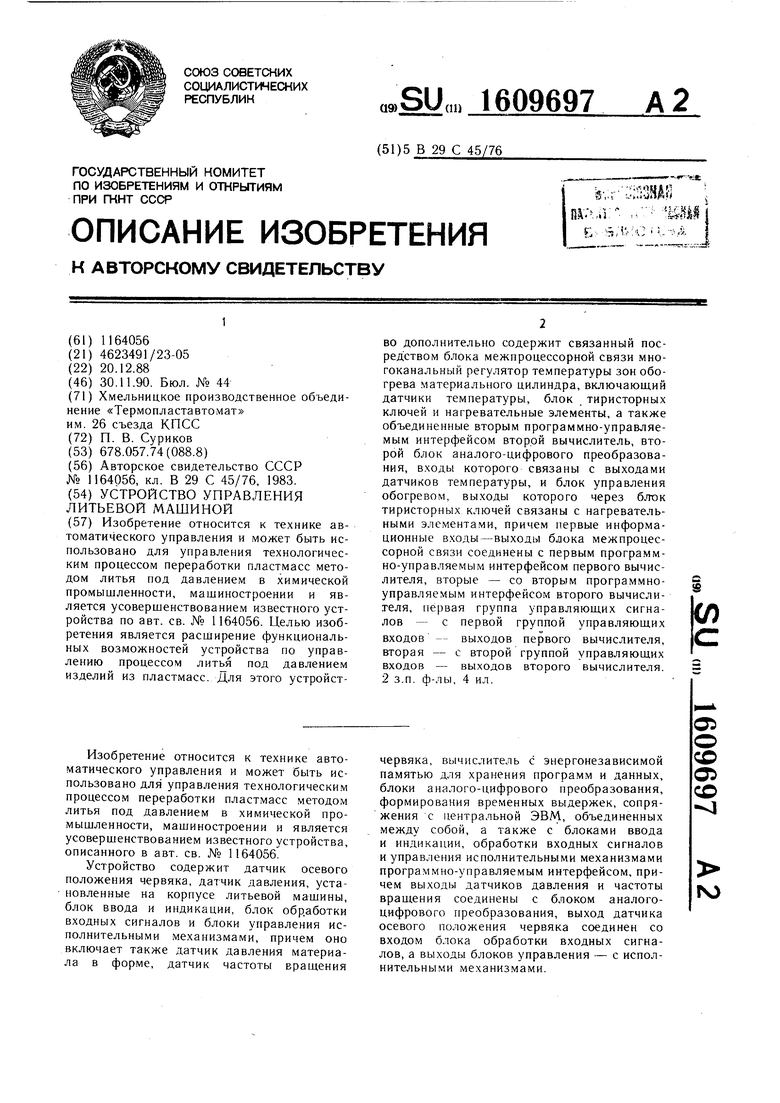

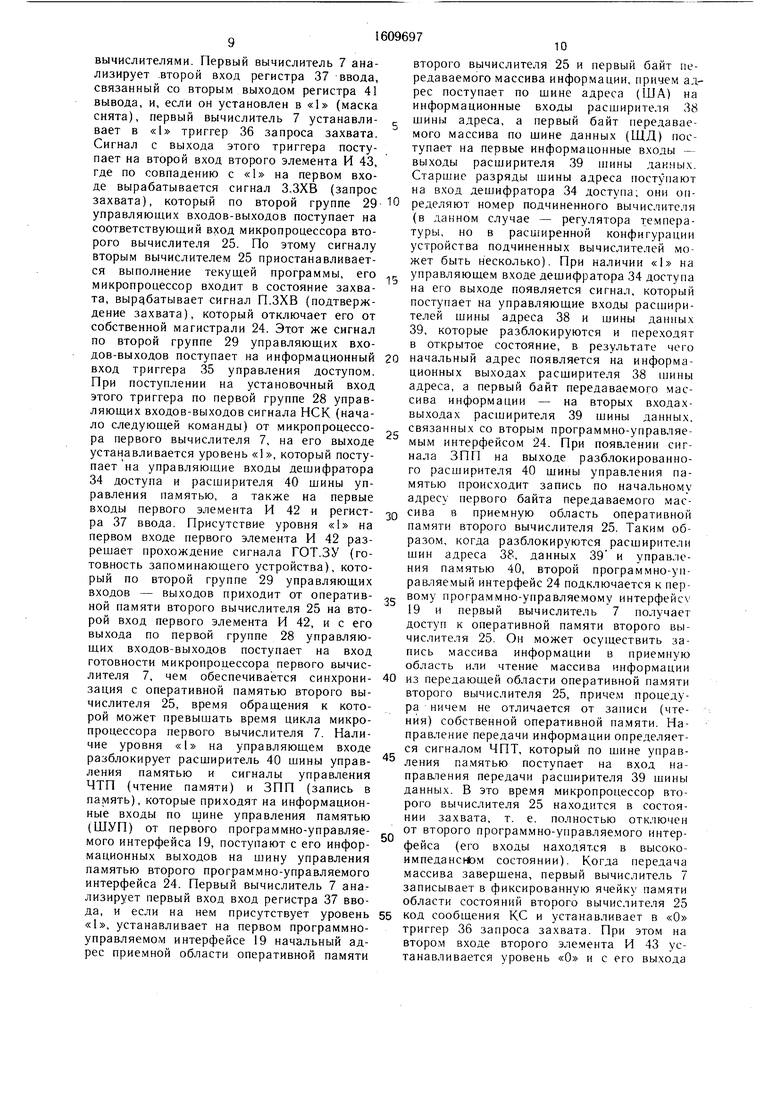

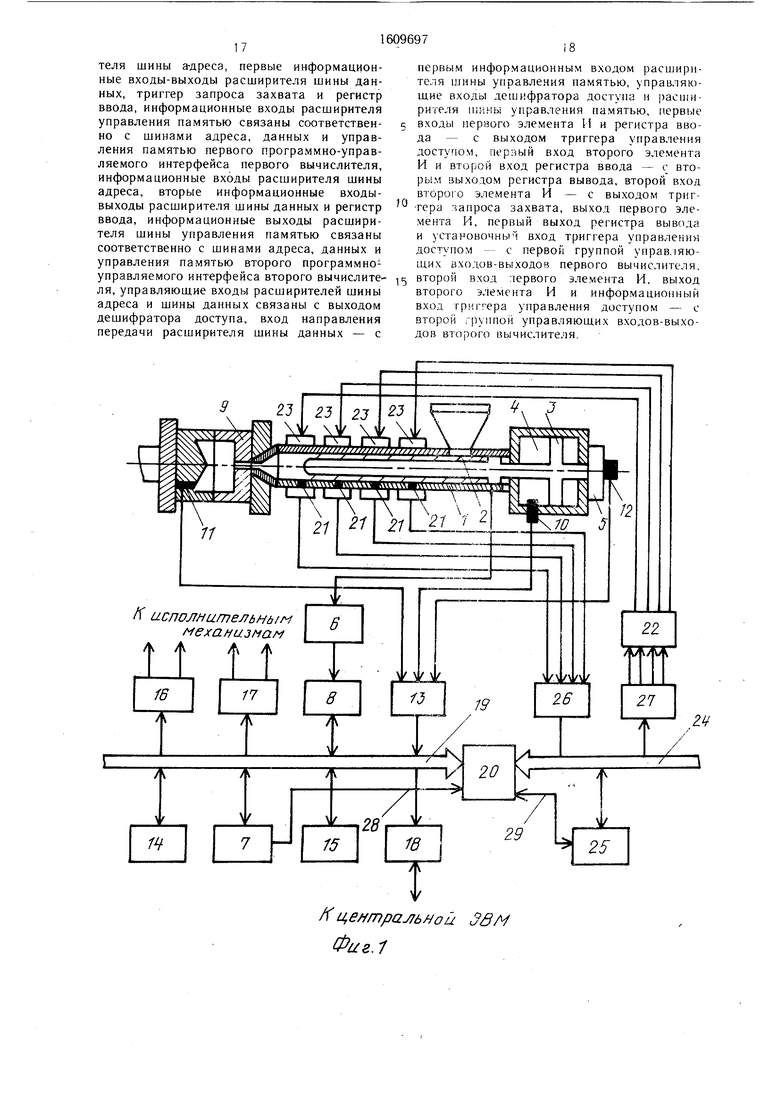

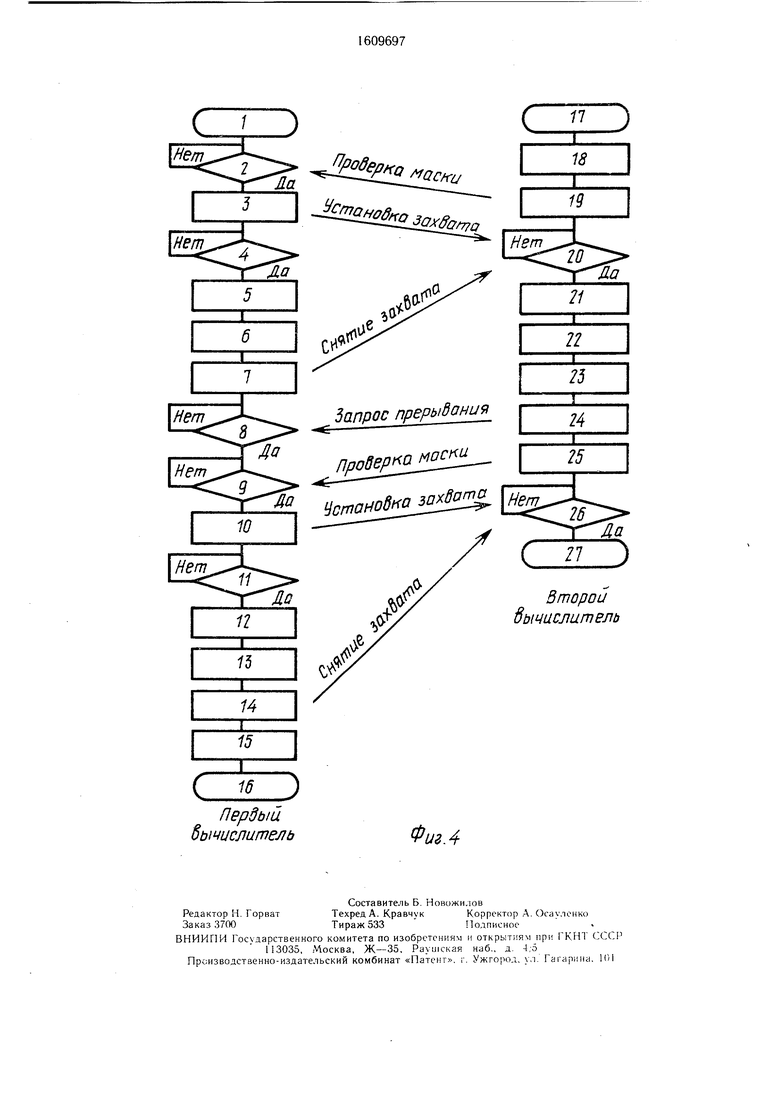

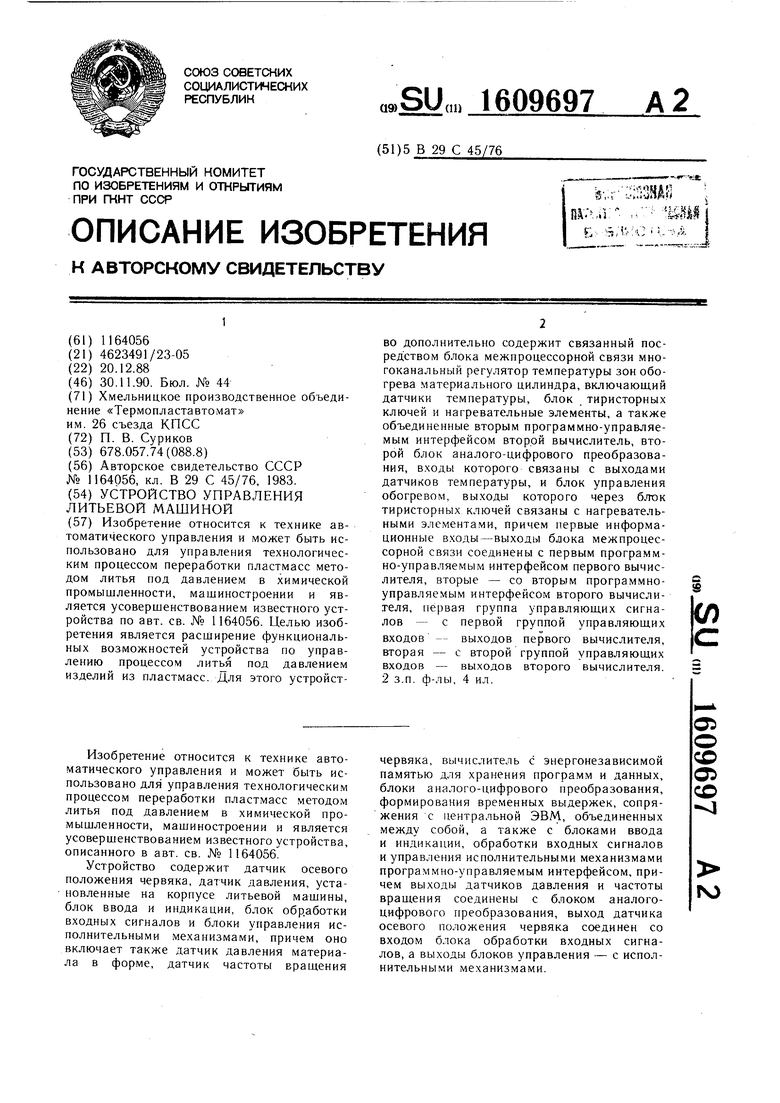

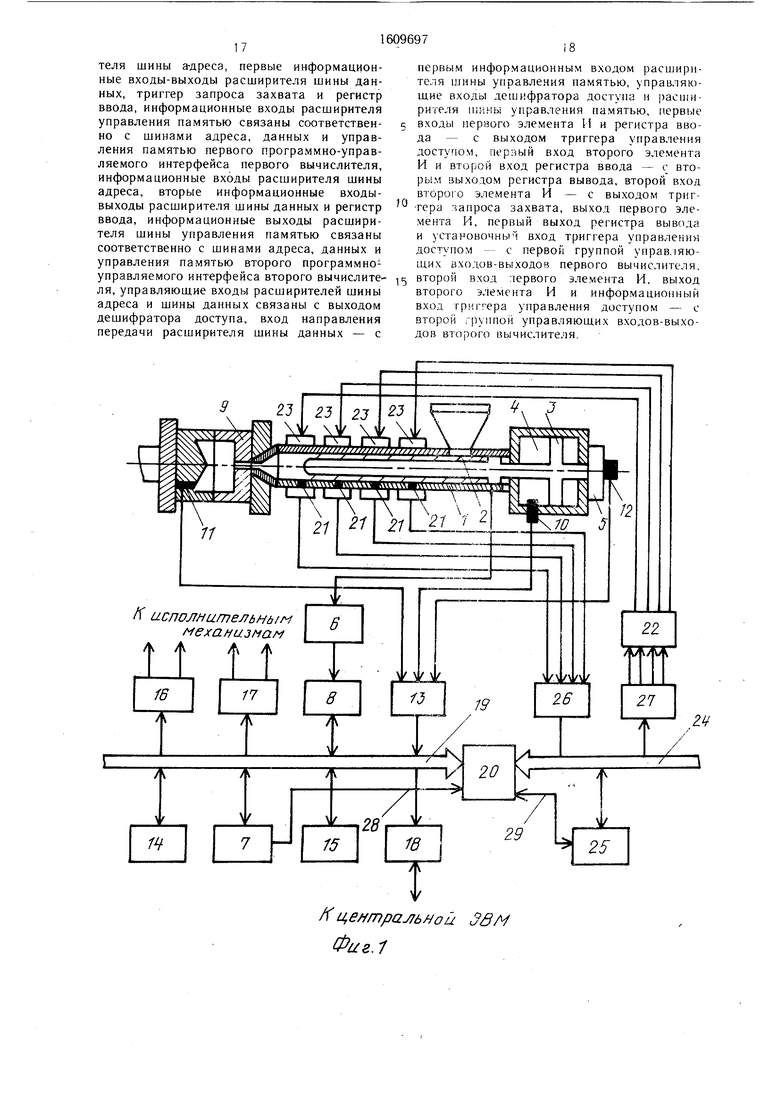

На фиг. 1 приведена структурная схе-группой управляющих входов - выходов

ма устройства управления литьевой ма-23 первого вычислителя 7, вторая - со щиной; на фиг. 2 - структурная схема g второй группой управляющих входов - выблока управления обогревом; на фиг. 3 -ходов 29 второго вычислителя 25. структурная схема блока межпроцессорной связи; на фиг. 4 упрощенный алгоритм теста контроля межпроцессорной связи.

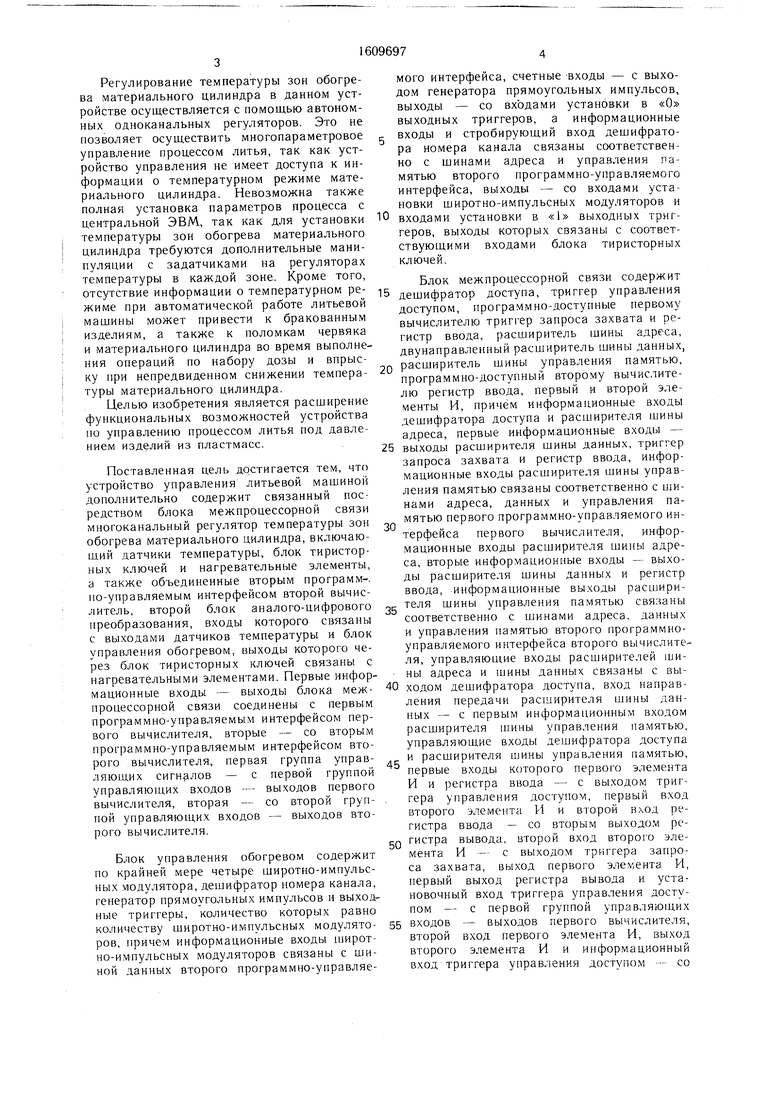

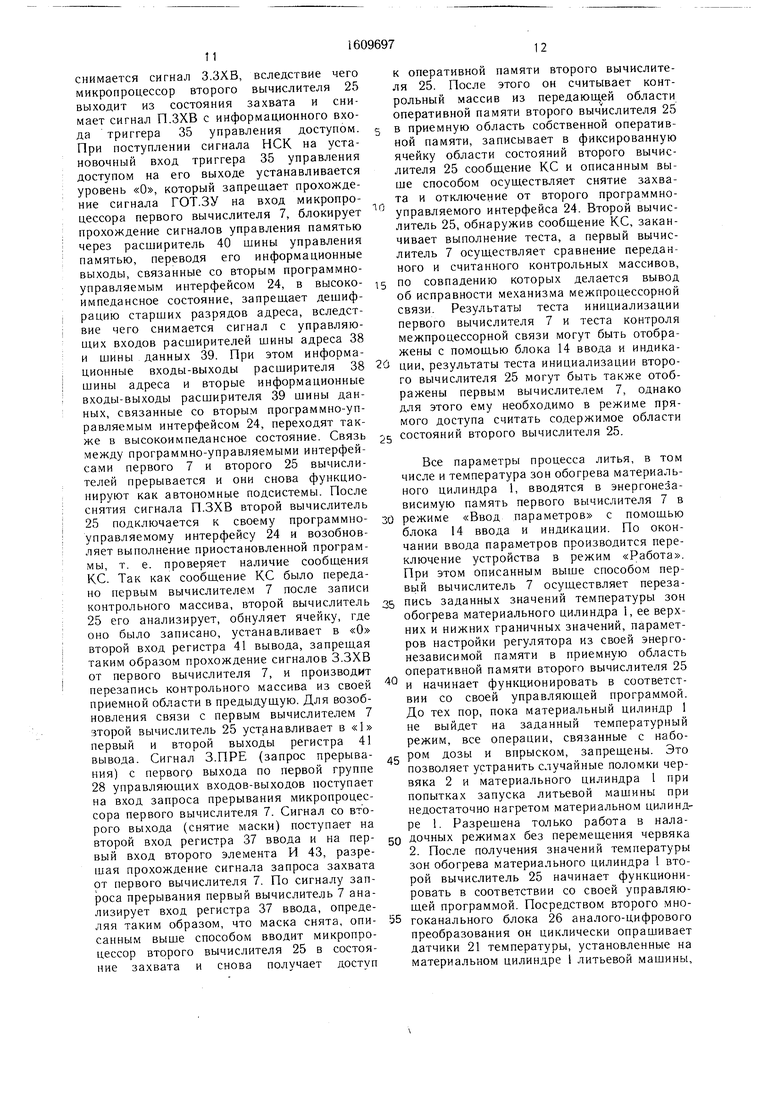

Блок управления обогревом 27 содержит четыре широтно-импульсных модулятора 30, дешифратор 31 номера канала, гене Внутри материального цилиндра 1 литье- Ю ратор 32 прямоугольных импульсов и че- вои машины (фиг. 1) расположен червяк 2, тыре выходных триггера 33. Информацион- которыи может перемещаться поступательно „ые входы щиротно-импульсных модулято- под воздействием поршня 3, находящегося ров 30 связаны с шиной данных второ- в гидроцилиндре 4, и вращаться с по- го программно-управляемого интерфейса 24, мощью гидромотора 5. Текущее положение счетные входы - с выходом генератора червяка 2 при пластикации и впрыске 32 прямоугольных импульсов, выходы - со

входами установки в «О выходных триггеров 32, а информационные входы и стро- бирующий вход дешифратора 31 номера канала связаны соответственно с шинами давление в гидроцилиндре 4 и давление 20 адреса и управления памятью второго расплава полимера в форме 9 опреде- программно-управляемого интерфейса 24,

выходы - со входами установки широтно-импульсных модуляторов 30 и входами установки в «1 выходных триггеров 33,

определяется с помощью датчика осевого положения 6, связанного с первым вычислителем 7 посредством блока 8 обработки входных сигналов, гидравлическое

ляется датчиками давления 10 и 11 соответственно, частота вращения червяка 2 при пластикации определяется датчиком 12, причем датчики 10-12 связаны с вычис25 выходы которых связаны с соответствую- лителем 7 посредством первого многока- щими входами блока тиристорных клю- нального блока 13 аналого-цифрового преоб- чей 22

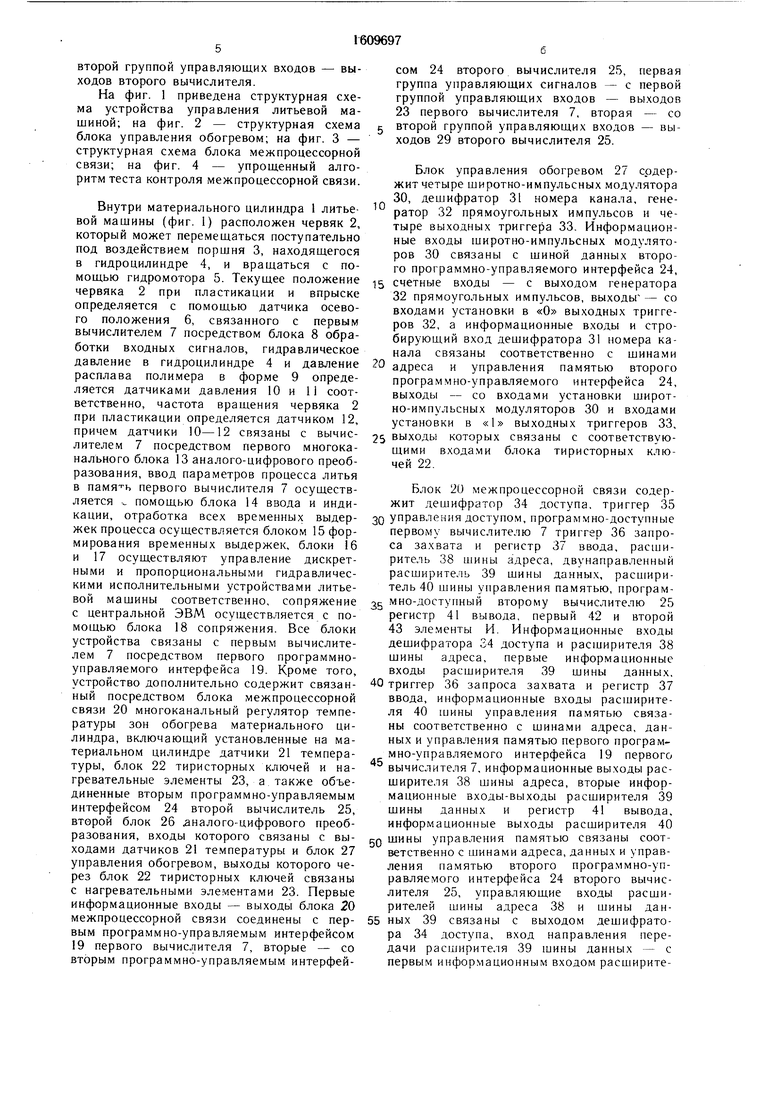

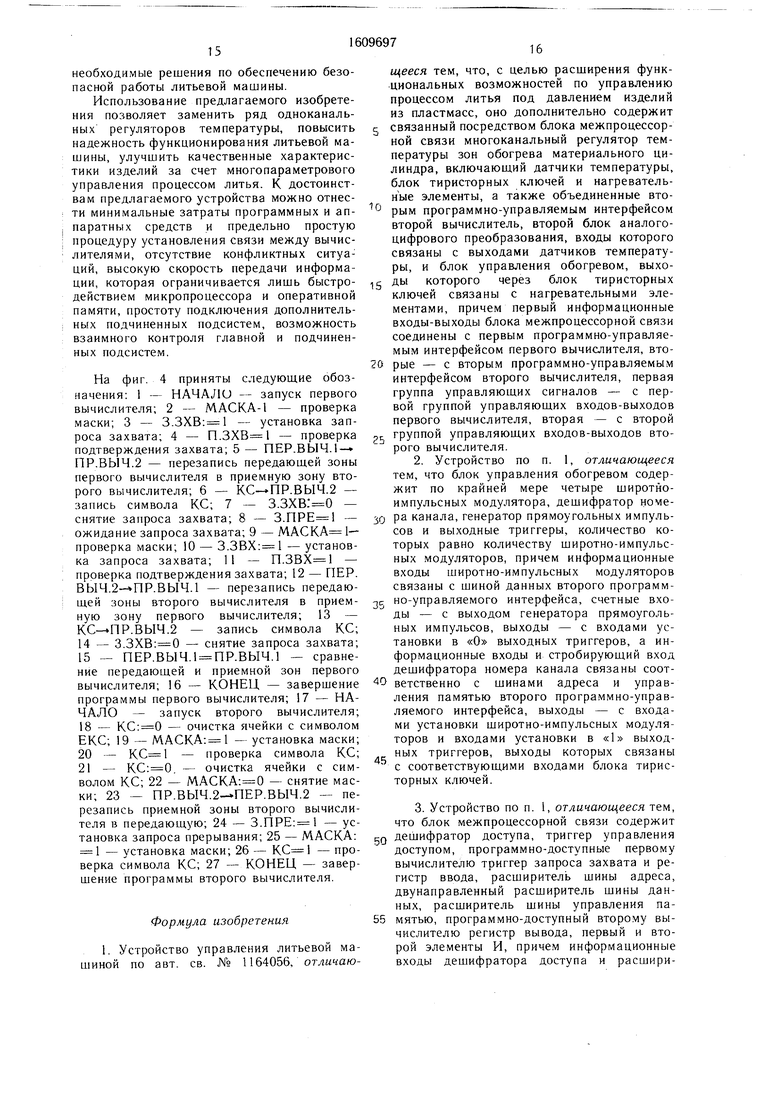

разования, ввод параметров процесса литья в памя- ь первого вычислителя 7 осуществляется . помощью блока 14 ввода и индиБлок 2U межпроцессорной связи содержит дешифратор 34 доступа, триггер 35

кации, отработка всех временных выдер- зо У Р - л ступом, программно-доступные

жек процесса осуществляется блоком 15 фор мирования временных выдержек, блоки 16 и 17 осуществляют управление дискретными и пропорциональными гидравлическими исполнительными устройствами литьепервому вычислителю 7 триггер 36 запроса захвата и регистр 37 ввода, расширитель 38 шины адреса, двунаправленный расширитель 39 шины данных, расширитель 40 шины управления памятью, програм- вой машины соответственно, сопряжение 35 мно-доступный второму вычислителю 25 с центральной ЭВМ осуществляется с по- регистр 41 вывода, первый 42 и второй

43 элементы И. Информационные входы дешифратора 34 доступа и расширителя 38 шины адреса, первые информационные входы расширителя 39 шины данных,

устройство дополнительно содержит связан- 40 триггер 36 запроса захвата и регистр 37 иь1Й посредством блока межпроцессорной ввода, информационные входы расширителя 40 шины управления памятью связаны соответственно с шинами адреса, данных и управления памятью первого программно-управляемого интерфейса 19 первого вычислителя 7, информационные выходы расширителя 38 шины адреса, вторые информационные входы-выходы расширителя 39 шины данных и регистр 41 вывода, информационные выходы расширителя 40 разования, входы которого связаны с вы- щины управления памятью связаны соот- ходами датчиков 21 температуры и блок 27 ветственно с шинами адреса, данных и управ- управления обогревом, выходы которого че- ления памятью второго программно-уп- рез блок 22 тиристорных ключей связаны равляемого интерфейса 24 второго вычис- с нагревательными эле.ментами 23. Первые лителя 25, управляющие входы расши- информационные входы - выходы блока 20 рителей шины адреса 38 и шины дан- межпроцессорной связи соединены с пер- 55 ных 39 связаны с выходом дешифрато- вым программно-управляемым интерфейсом ра 34 доступа, вход направления пере- 19 первого вычислителя 7, вторые -- со дачи расширителя 39 шины данных - с вторым программно-управляемым интерфей-первым информационным входом расширитемощью блока 18 сопряжения. Все блоки устройства связаны с первым вычислителем 7 посредством первого программно- управляемого интерфейса 19. Кроме того,

связи 20 многоканальный регулятор температуры зон обогрева материального цилиндра, включающий установленные на материальном цилиндре датчики 21 температуры, блок 22 тиристорных ключей и на- гревательные элементы 23, а также объединенные вторым программно-управляемым интерфейсом 24 второй вычислитель 25, второй блок 26 аналого-цифрового преобБлок 2U межпроцессорной связи содержит дешифратор 34 доступа, триггер 35

У Р - л ступом, программно-доступные

равления памятью 40 блока 20 межпроцессорной связи настраиваются таким образом, что вторые информационные входы - выходы, связанные со вторым программно- управляемым интерфейсом 24, находятся в высокоймпедансном состоянии. Поэтому оба вычислителя с подключенными посредством -первого и второго программно-управляемых интерфейсов блоками образуют практически автономные подсистемы, функциоля 40 шины управления памятью, управляющие входы дешифратора 34 доступа и расширителя 40 шины управления памятью, первые входы первого элемента И 42 и регистра 37 ввода - с выходом триггера 35 управления доступом, первый вход второго элемента И 43 и второй вход регистра 37 ввода -- со вторым выходом регистра 41 вывода, второй вход

второго элемента И 42 - с выходом... ,.,

триггера 36 запроса захвата, выход перво- Ю нирующие независимо друг от друга по го элемента И 42, первый выход регист- своим программам, хранящимся в постоян- ра 41 вывода и установочный вход триг- ной памяти.

гера 35 управления доступом - с первойВ начальный момент каждый из них

группой 28 управляющих входов - выхо- запускает тест инициализации, который дов первого вычислителя 7, второй вход ,5 производит автоматическую проверку всех первого элемента И 42, выход второго эле- блоков подсистемы. По результатам про- - - верки заполняется область состоянии оперативной памяти каждого вычислителя. Содержимое области состояний первого вычислителя 7 может быть отображено пос- 20 редством блока 14 ввода и индикации. Второй вычислитель 25 такой возможности не имеет, он очищает фиксированную ячейку памяти в области состояний, в котораммни-уираьлисии.и пп.. - PV ВО время процедуры прямого достуми обеспечивает управление циклом рабо- „R первый вь1числитель 7 записывает код ты литьевой машины, задание и регулиро- сообщения КС (конец связи), затем устанавливает в «1 второй выход регистра 41 вывода (снимает маску) и переходит к анализу сообщения КС, ожидая образом связи по инициативе первого вы- 30 числителя 7. Снятие маски означает, что второй вычислитель 25 может приостановить выполнение текущей программы по запросу первого вычислителя 7, т. е. разрешить прямой доступ к своей оперативной памяти. Первый вычислитель 7 по оконрат уры зон обогрева материального ци- 35 чании теста инициализации запускает тест чиндра 1 К первому программно-управ- контроля межпроцессорной связи, hro сущ

- ность заключается в том, что первый

вычислитель 7 .вводит в состояние захвата микропроцессор второго вычислителя 25, получает доступ ко второй магист- рали 24 и в режиме прямого доступа записывает контрольный массив информации в приемную область оперативной памяти второго вычислителя 25. После снятия захвата второй вычислитель 25 произ.ILMCll .- 1 I.J ГI г I i.-/ jnji/ivyi n-i-v-v ii - I.1H j., ..- -r

ЦИИ Значения температуры зон обогрева вод.т перезапись этого массива из прием- задаются втор.ому вычислителю 25 первымной области оперативной памяти в передаю- вычислителем 7 посредством блока 20щую и выставляет сигнал запроса пре- межпроцессорной связи (фиг. 3) с по-рывания первому вычислителю 7. Первый мощью процедуры прямого доступа к опера-вычислитель 7, снова вводит в состояние тивной памяти второго вычислителя 25.захвата второй вычислитель 2о, в режиме Таким же образом осуществляется считы-50 прямого доступа считывает контрольный вание текущих значений температуры зонмассив из передающей области оперативной обогрева и информация о состоянии регу-памяти второго вычислителя 25 в прием- лятора температуры для отображения пер-ную область своей оперативной памяти вым вычислителем 7 посредством блока 14и производит проверку соответствия переввода и индикации. Для этой цели обаданного массива и считанного. Рассмотрим вычислителя имеют обменные области опера-55 более подробно на примере теста конт- тивной памяти- приемную и передающую.роля межпроцессорной связи, упрощенный При подаче питания на устройство фор-алгоритм которого приведен на фиг. 4, мирователи щин адреса 38, данных 39 и уп-способ организации взаимодействия между

мента И 43 и информационный вход триггера 35 управления доступом - со второй группой 29 управляющих входов - выходов второго вычислителя 25.

Устройство работает следующим образом.

Первый вычислитель 7 с подключенными к нему посредством первого программно-управляемого интерфейса 19 блокавание о сновных параметров процесса литья, за исключением регулирования температуры зон обогрева материального цилиндра. В рассматриваемой конфигурации первый вычислитель 7 является главным, второй вычислитель 25 - подчиненным. Второй вычислитель 25 с подключенными к нему посредством второго программно-управляемого интерфейса 24 блоками обеспечивает многоканальное ПИД-регулирование темпеляемому интерфейсу 19 первого вычислителя 7 подключен блок 14 ввода и индикации, посредством которого осуществляется задание режимов работы литьевой ма- щины и запись технологических параметров процесса литья, включая температурный режим материального цилиндра 1, в энергонезависимую память, отображение диагностической и технологической информаравления памятью 40 блока 20 межпроцессорной связи настраиваются таким образом, что вторые информационные входы - выходы, связанные со вторым программно- управляемым интерфейсом 24, находятся в высокоймпедансном состоянии. Поэтому оба вычислителя с подключенными посредством -первого и второго программно-управляемых интерфейсов блоками образуют практически автономные подсистемы, функцио... ,.,

нирующие независимо друг от друга по своим программам, хранящимся в постоян- ной памяти.

n1609697

910

вычислителями. Первый вычислитель 7 ана-второго вычислителя 25 и первый байт пе- лизирует .второй вход регистра 37 ввода,редаваемого массива информации, причем а v связанный со вторым выходом регистра 41рее поступает по шине адреса (ША) на вывода, и, если он установлен в «1 (маскаинформационные входы расширителя 38 снята), первый вычислитель 7 устанавли- шины адреса, а первый байт передавае- вает в «I триггер 36 запроса захвата. мого массива по шине данных (ЩД) пос- Сигнал с выхода этого триггера посту-тупает на первые информацонные входы - пает на второй вход второго элемента И 43, выходы расширителя 39 пшны данных, где по совпадению с «1 на первом вхо-Старшие разряды шины адреса посту пают де вырабатывается сигнал З.ЗХВ (запросна вход дешифратора 34 доступа; он и оп- захвата), который по второй группе 29Ю ределяют номер подчиненного вычислителя управляюших входов-выходов поступает на(в данном случае - регулятора темпера- соответствующий вход микропроцессора вто-туры, но в расширенной конфигурации рого вычислителя 25. По этому сигналуустройства подчиненных вычислителей мо- вторым вычислителем 25 приостанавливает-жет быть несколько). При наличии «1 на ся выполнение текущей программы, его- управляющем входе дешифратора 34 доступа микропроцессор входит в состояние захва- на его выходе появляется сигнал который та, вырабатывает сигнал П.ЗХВ (подтверж-поступает на управляющие входы расщири- дение захвата), который отключает его оттелей шины адреса 38 и шины данных собственной магистрали 24. Этот же сигнал39, которые разблокируются и переходят по второй группе 29 управляющих вхо-в открытое состояние, в результате чего дов-выходов поступает на информационный20 начальный адрес появляется на информа- вход триггера 35 управления доступом.ционных выходах расширителя 38 При поступлении на у становочный входадреса, а первый байт передаваемого мас- этого триггера по первой группе 28 управ-сива информации - на вторых входах- ляющих входов-выходов сигнала ИСК (нача-выходах расширителя 39 шины данных ло следующей команды) от микропроцессо-связанных со вторым программно-управляе- ра первого вычислителя 7, на его выходе мым интерфейсом 24. При появлении сиг- устанавливается уровень «1, который посту-нала ЗПП на выходе разблокированно- пает на управляющие входы дешифратораго расширителя 40 шины управления па- 34 доступа и расширителя 40 шины уп-мятью происходит запись по начальному равления памятью, а также на первыеадресу первого байта передаваемого мас - входы первого элемента И 42 и регист-30 сива в приемную область оперативной ра 37 ввода. Присутствие уровня «1 напа.мяти второго вычислителя 25. Таким об- первом входе первого элемента И 42 раз-разом, когда разблокируются расширитеаи решает прохождение сигнала ГОТ.ЗУ (го-шин адреса 38, данных 39 и управле- тов ность запоминающего устройства), кото-ния памятью 40, второй программно-уп- рый по второй группе 29 управляющихравляемый интерфейс 24 подключается к пер- входов -- выходов приходит от оператив-.,- вому программно-управляемому интерфейсу НОИ памяти второго вычислителя 25 на ВТО-19 и первый вычислитель 7 получает рои вход первого элемента И 42, и с егодоступ к оперативной памяти второго вы- выхода по первой группе 28 управляю-числителя 25. Он может осуществить за- щих входов-выходов поступает на входпись массива информации в приемную готовности микропроцессора первого вычис-область или чтение массива информац ии лителя 7, чем обеспечивается синхрони-40 из передающей области оперативной памяти зация с оперативной памятью второго вы-второго вычислителя 25, причем процеау- числителя 25, время обращения к кото-ра ничем не отличается от записи (чте- рои может превышать время цикла микро-ния) собственной оперативной памяти На- процессора первого вычислителя 7. Нали-правление передачи информации опречеляет- чие уровня «1 на управляющем входеся сигналом ЧПТ, который по шине управ- разблокирует расширитель 40 шины управ- 5 ения памятью поступает на вход на- ления памятью и сигналы управленияправления передачи расширителя 39 шины ЧТП (чтение памяти) и ЗПП (запись вданных. В это время микропроцессор вто- память), которые приходят на информацион-рого вычислителя 25 находится в состоя- т/Д ° ° управления памятьюнии захвата, т. е. полностью отключен (ШУП) от первого программно-управляе- от второго программно-управляемого интер- мого интерфейса 19, поступают с его инфор- фейса (его входы находятся в высоко- мационных выходов на шину управленияимпедансИом состоянии). Когда передача памятью второго программно-управляемогомассива завершена, первый вь |числитель 7 интерфейса 24. Первый вычислитель 7 ана-записывает в фиксированную ячейку памяти лизирует первый вход вход регистра 37 вво-области состояний второго вычислителя 25 да, и если на нем присутствует уровень 55код сообщения КС и устанавливает в «О «1, устанавливает на первом программно-триггер 36 запроса захвата. При этом на управляемом интерфейсе 19 начальный ад-втором входе второго элемента И 43 ус- рес приемной области оперативной памятитанавливается уровень «О и с его выхода

11

1609697

снимается сигнал З.ЗХВ, вследствие чего микропроцессор второго вычислителя 25 выходит из состояния захвата и снимает сигнал П.ЗХВ с информационного входа триггера 35 управления доступом. При поступлении сигнала ИСК на установочный вход триггера 35 управления доступом на его выходе устанавливается уровень «О, который запрещает прохождение сигнала ГОТ.ЗУ на вход микропроцессора первого вычислителя 7, блокирует прохождение сигналов управления памятью через расширитель 40 шины управления памятью, переводя его информационные выходы, связанные со вторым программно- управляемым интерфейсом 24, в высоко- импедансное состояние, запрец ает дешифрацию старших разрядов адреса, вследствие чего снимается сигнал с управляющих входов расширителей шины адреса 38 и шины данных 39. При этом информационные входы-выходы расширителя 38 шины адреса и вторые информационные входы-выходы расширителя 39 шины данных, связанные со вторым программно-управляемым интерфейсом 24, переходят также в высокоимпедансное состояние. Связь между программно-управляемыми интерфейсами первого 7 и второго 25 вычислителей прерывается и они снова функционируют как автономные подсистемы. После снятия сигнала П.ЗХВ второй вычислитель 25 подключается к своему программно- управляемому интерфейсу 24 и возобновляет выполнение приостановленной программы, т. е. проверяет наличие сообщения КС. Так как сообщение КС было передано первым вычислителем 7 после записи контрольного массива, второй вычислитель 25 его анализирует, обнуляет ячейку, где оно было записано, устанавливает в «О второй вход регистра 41 вывода, запрещая таким образом прохождение сигналов З.ЗХВ от первого вычислителя 7, и производит перезапись контрольного массива из своей приемной области в предыдущую. Для возобновления связи с первым вычислителем 7 зторой вычислитель 25 устанавливает в «1 первый и второй выходы регистра 41 вывода. Сигнал З.ПРЕ (запрос прерывания) с первого выхода по первой группе 28 управляющих входов-выходов поступает на вход запроса прерывания микропроцессора первого вычислителя 7. Сигнал со второго выхода (снятие маски) поступает на второй вход регистра 37 ввода и на первый вход второго элемента И 43, разрешая прохождение сигнала запроса захвата от первого вычислителя 7. По сигналу запроса прерывания первый вычислитель 7 анализирует вход регистра 37 ввода, определяя таким образом, что маска снята, описанным выше способом вводит микропроцессор второго вычислителя 25 в состояние захвата и снова получает доступ

12

к оперативной памяти второго вычислителя 25. После этого он считывает контрольный массив из передающей области оперативной памяти второго вычислителя 25 в приемную область собственной оперативной памяти, записывает в фиксированную ячейку области состояний второго вычислителя 25 сообщение КС и описанным выше способом осуществляет снятие захвата и отключение от второго программно- управляемого интерфейса 24. Второй вычислитель 25, обнаружив сообщение КС, заканчивает выполнение теста, а первый вычислитель 7 осуществляет сравнение переданного и считанного контрольных массивов, 5 по совпадению которых делается вывод об исправности механизма межпроцессорной связи. Результаты теста инициализации первого вычислителя 7 и теста контроля межпроцессорной связи могут быть отображены с помощью блока 14 ввода и индика- U ции, результаты теста инициализации второго вычислителя 25 могут быть также отображены первым вычислителем 7, однако для этого ему необходимо в режиме прямого доступа считать содержимое области 25 состояний второго вычислителя 25.

Все параметры процесса литья, в том числе и температура зон обогрева материального цилиндра 1, вводятся в энергонезависимую память первого вычислителя 7 в режиме «Ввод параметров с помощью блока 14 ввода и индикации. По окончании ввода параметров производится переключение устройства в режим «Работа. При этом описанным выше способом первый вычислитель 7 осуществляет переза- 5 пись заданных значений температуры зон обогрева материального цилиндра 1, ее верхних и нижних граничных значений, параметров настройки регулятора из своей энергонезависимой памяти в приемную область оперативной памяти второго вычислителя 25 и начинает функционировать в соответствии со своей управляющей программой. До тех пор, пока материальный цилиндр 1 не выйдет на заданный температурный режим, все операции, связанные с набором дозы и впрыском, запрещены. Это позволяет устранить случайные поломки червяка 2 и материального цилиндра 1 при попытках запуска литьевой машины при недостаточно нагретом материальном цилиндре 1. Разрешена только работа в нала- 50 дочных режимах без перемещения червяка 2. После получения значений температуры зон обогрева материального цилиндра 1 второй вычислитель 25 начинает функционировать в соответствии со своей управляющей программой. Посредством второго мно- 55 гоканального блока 26 аналого-цифрового преобразования он циклически опращивает датчики 21 температуры, установленные на материальном цилиндре 1 литьевой мащины.

производит статистическую обработку результатов преобразования, линеаризацию характеристик датчиков, компенсацию температуры холодных спаев и определяет действительную температуру каждой зоны. Эта информация используется для вычисления рассогласования между заданными и действительными значениями температуры, а также записывается в передающую зону оперативной памяти для контроля со стороны первого вычислителя 7. На основании вычисленного рассогласования для каждой зоны и в соответствии с цифровым ПИД-алгоритмом второй вычислитель 25 определяет величины управляющих воздействий для блока 27 управления обогревом, который преобразует их в управляющие пульсы для блока 22 тиристорных ключей, длительность которых пропорциональна величинам рассогласования между действительными и заданными значениями температуры в каждой зоне.

Для этого второй вычислитель 25 на шине адреса второго программно-управляемого интерфейса 24 устанавливает номер i-ro канала, на шине данных - двоично-десятичный код вычисленного управляющего воздействия. По сигналу ЗПП дешифратор 31 номера канала вырабатывает сигнал установки в «1 соответствующего выходного триггера 33, формируя таким образом передний фронт сигнала управления тиристорным ключом i-ro канала блока 22 тиристорных ключей.

Тиристорный ключ i-ro канала открывается, обеспечивая таким образом прохождение тока от питающей сети на соответствующий нагревательный элемент 23.

Кроме того, сигнал с выхода дешифратора 31 номера канала поступает на вход установки соответствующего щиротно-им- пульсного модулятора 30, по которому код управляющего воздействия записывается с шины данных второго программно-управляемого интерфейса 24 в вычитающие счетчики этого щиротно-импульсного модулятора По приходу на счетный вход широтно- импульсного модулятора 30 переднего фронта первого после записи кода импульса от генератора 32 прямоугольных импульсов начинается обратный счет вычитающих счетчиков. При поступлении на счетный вход количества импульсов, соответствующего записанному двоично-десятичному коду происходит обнуление вычитающих счетчиков, вследствие чего на выходе щиротно- импульсного модулятора 30 появляется сигнал окончания счета, который устанавливает в «О соответствующий выходной триггер 33, формируя таким образом задний фронт сигнала управления тиристорным ключом 1-го канала блока 22 тиристорных ключей.

При этом тиристорный ключ закрывается и прекращается протекание тока от питающей сети на соответствующий нагревательный элемент 23.

Таким образом, на нагревательном элементе 23 в течение промежутка времени,

определяемого величиной управляющего воздействия, выделяется порция энергии, пропорциональная длительности управляющего импульса, величине тока, протекающего через нагревательный элемент 23, и напряжению питающей сети.

О Для снижения уровня электромагнитных помех, возникающих при коммутации больших токов, протекающих через нагревательные элементы 23, генератор 32 прямоугольных импульсов синхронизирован с перехос дом через «О напряжения питающей сети.

Параметры настройки конкретного регулятора (период квантования, коэффициент усиления, постоянные дифференцирования и интегрирования) определяются эксперимен0 тально и зависят от типа материального цилиндра, для которого предназначен регулятор. Они записываются в энергонезависимую память первого вычислителя 7 и передаются в приемную область второго вычис лителя 25 вместе со значениями температуры зон обогрева материального цилиндра 1. Для определения момента выхода материального цилиндра 1 на заданный температурный режим первый вычислитель 7 через равные промежутки времени считы0 вает из передающей зоны оперативной памяти второго вычислителя 25 текущие значения температуры зон обогрева и только при достижении ими заданных значений начинает функционировать в соответствии с описанием основного изобрете5 ния. Считанные текущие значения температуры хранятся в его приемной области и могут быть отображены посредством блока 14 ввода и индикации. В случае отклонений в ходе технологического процесса или при многопараметровом управле0 НИИ процессом температурный режим материального цилиндра 1 может быть откорректирован первым вычислителем 7 путем записи в приемную область оперативной памяти второго вычислителя 25 новых значений температуры зон обогрева и их граничных значений. В случае неисправности схем регулятора или аварийных ситуаций, например, при выходе температуры отдельных зон за допустимые пределы, обрыве датчиков температуры или нагреваQ тельных элементов второй вычислитель 25 записывает соответствующие признаки в массив состояний передающей области оперативной памяти бырабатывает сигнал запроса прерывания микропроцессору первого вычислителя 7. По этому сигналу первый

5 вычислитель 7 в режиме прямого доступа считывает из передающей области второго вычислителя 25 информацию о состоянии регулятора температуры и принимает

необходимые решения по обеспечению безопасной работы литьевой машины.

Использование предлагаемого изобретения позволяет заменить ряд одноканаль- ных регуляторов температуры, повысить надежность функционирования литьевой машины, улучшить качественные характеристики изделий за счет многопараметрового управления процессом литья. К достоинствам предлагаемого устройства можно отнести минимальные затраты программных и аппаратных средств и предельно простую процедуру установления связи между вычислителями, отсутствие конфликтных ситуаций, высокую скорость передачи информации, которая ограничивается лишь быстродействием микропроцессора и оперативной памяти, простоту подключения дополнительных подчиненных подсистем, возможность взаимного контроля главной и подчиненных подсистем.

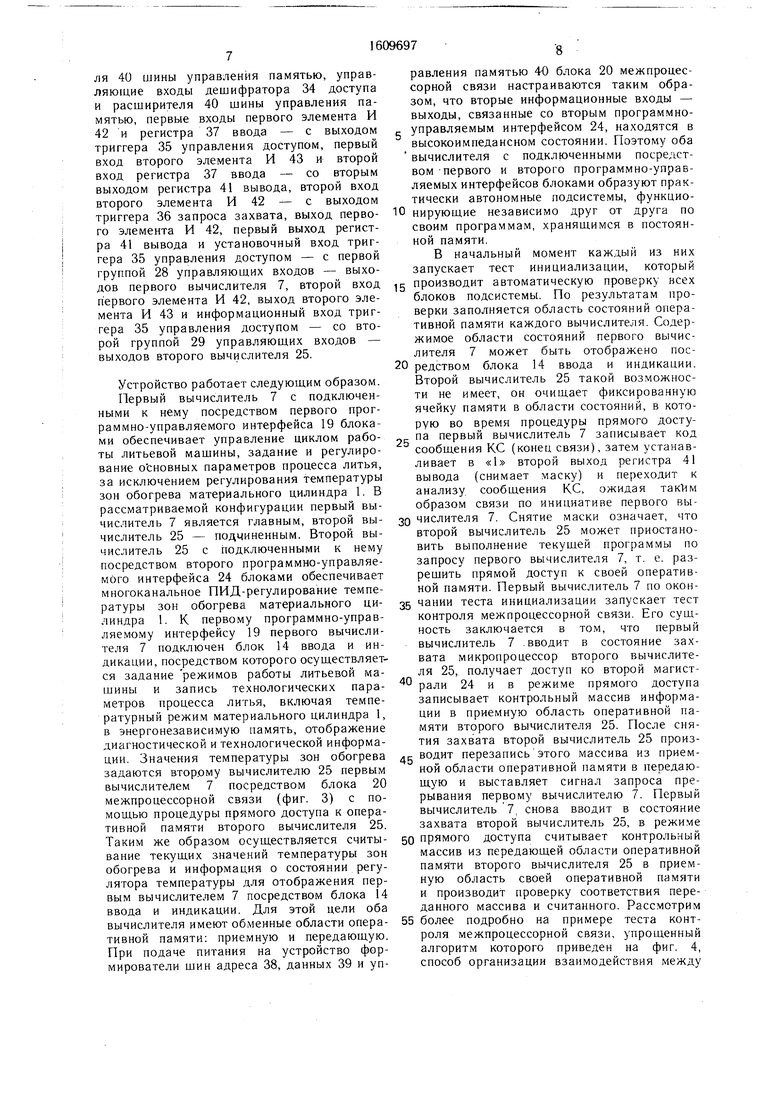

На фиг. 4 приняты следующие обозначения; 1 - НАЧАЛО - запуск первого вычислителя; 2 - МАСКА-1 - проверка маски; 3 -- З. - установка запроса захвата; 4 - П. - проверка подтверждения захвата; 5 - ПЕР.ВЫЧ.1- ПР.ВЫЧ.2 - перезапись передающей зоны первого вычислителя в приемную зону второго вычислителя; 6 - .ВЫЧ.2 - запись символа КС; 7 - З.ЗХВ. - снятие запроса захвата; 8 - З. - ожидание запроса захвата; 9 - МАСКА 1- проверка маски; 10 - З. - установка запроса захвата; 11 - П. - проверка подтверждения захвата; 12 - ПЕР. ВЫЧ..ВЫЧ.1 - перезапись передающей зоны второго вычислителя в приемную зону первого вычислителя; 13 - .ВЫЧ.2 - запись символа КС;

14- З. - снятие запроса захвата;

15- ПЕР.ВЫЧ.1 ПР.ВЫЧ.1 - сравнение передающей и приемной зон первого вычислителя; 16 - КОНЕЦ - завершение программы первого вычислителя; 17 - НАЧАЛО - запуск второго вычислителя; 18 - - очистка ячейки с символом ЕКС; 19 - МАСКА: 1 установка маски;

20-- - проверка символа КС;

21- . - очистка ячейки с символом КС; 22 - МАСКА; 0 - снятие маски; 23 - ПР.ВЫЧ..ВЫЧ.2 - перезапись приемной зоны второго вычислителя в передающую; 24 - З. - ус15

20

щееся тем, что, с целью расширения функциональных возможностей по управлению процессом литья под давлением изделий из пластмасс, оно дополнительно содержит

с связанный посредством блока межпроцессорной связи многоканальный регулятор температуры зон обогрева материального цилиндра, включающий датчики температуры, блок тиристорных ключей и нагреватель- Hbie элементы, а также объединенные рым программно-управляемым интерфейсом второй вычислитель, второй блок аналого- цифрового преобразования, входы которого связаны с выходами датчиков температуры, и блок управления обогревом, выходы которого через блок тиристорных ключей связаны с нагревательными элементами, причем первый информационные входы-выходы блока межпроцессорной связи соединены с первым программно-управляемым интерфейсом первого вычислителя, вторые - с вторым программно-управляемым интерфейсом второго вычислителя, первая группа управляющих сигналов - с первой группой управляющих входов-выходов первого вычислителя, вторая - с второй

рг группой управляющих входов-выходов второго вычислителя.

2.Устройство по п. 1, отличающееся тем, что блок управления обогревом содержит по крайней мере четыре широтно- импульсных модулятора, дешифратор номеyj pa канала, генератор прямоугольных импульсов и выходные триггеры, количество которых равно количеству широтно-импульс- ных модуляторов, причем информационные входы щиротно-импульсных модуляторов связаны с шиной данных второго программ-JC, но-управляемого интерфейса, счетные входы - с выходом генератора прямоугольных импульсов, выходы - с входами установки в «О выходных триггеров, а информационные входы и стробирующий вход дешифратора номера канала связаны соот ветственно с шинами адреса и управления памятью второго программно-управляемого интерфейса, выходы - с входами установки широтно-импульсных модуляторов и входами установки в «1 выходных триггеров, выходы которых связаны с соответствующими входами блока тиристорных ключей.

3.Устройство по п. 1, отличающееся тем, что блок межпроцессорной связи содержит

45

тановка запроса прерывания; 25 - МАСКА: Q дешифратор доступа, триггер управления

1 - установка маски; 26 - - проверка символа КС; 27 - КОНЕЦ - завершение программы второго вычислителя.

доступом, программно-доступные первому вычислителю триггер запроса захвата и регистр ввода, расширитель шины адреса, двунаправленный расширитель шины данных, расширитель шины управления памятью, программно-доступный второму вычислителю регистр вывода, первый и второй элементы И, причем информационные входы дешифратора доступа и расшириФормула изобретения

1. Устройство управления литьевой машиной по авт. св. № 1164056, 07-угичаю5

0

щееся тем, что, с целью расширения функциональных возможностей по управлению процессом литья под давлением изделий из пластмасс, оно дополнительно содержит

связанный посредством блока межпроцессорной связи многоканальный регулятор температуры зон обогрева материального цилиндра, включающий датчики температуры, блок тиристорных ключей и нагреватель- Hbie элементы, а также объединенные вто рым программно-управляемым интерфейсом второй вычислитель, второй блок аналого- цифрового преобразования, входы которого связаны с выходами датчиков температуры, и блок управления обогревом, выходы которого через блок тиристорных ключей связаны с нагревательными элементами, причем первый информационные входы-выходы блока межпроцессорной связи соединены с первым программно-управляемым интерфейсом первого вычислителя, вторые - с вторым программно-управляемым интерфейсом второго вычислителя, первая группа управляющих сигналов - с первой группой управляющих входов-выходов первого вычислителя, вторая - с второй

рг группой управляющих входов-выходов второго вычислителя.

2.Устройство по п. 1, отличающееся тем, что блок управления обогревом содержит по крайней мере четыре широтно- импульсных модулятора, дешифратор номеyj pa канала, генератор прямоугольных импульсов и выходные триггеры, количество которых равно количеству широтно-импульс- ных модуляторов, причем информационные входы щиротно-импульсных модуляторов связаны с шиной данных второго программJC, но-управляемого интерфейса, счетные входы - с выходом генератора прямоугольных импульсов, выходы - с входами установки в «О выходных триггеров, а информационные входы и стробирующий вход дешифратора номера канала связаны соот ветственно с шинами адреса и управления памятью второго программно-управляемого интерфейса, выходы - с входами установки широтно-импульсных модуляторов и входами установки в «1 выходных триггеров, выходы которых связаны с соответствующими входами блока тиристорных ключей.

3.Устройство по п. 1, отличающееся тем, что блок межпроцессорной связи содержит

45

Q дешифратор доступа, триггер управления

дешифратор доступа, триггер управления

доступом, программно-доступные первому вычислителю триггер запроса захвата и регистр ввода, расширитель шины адреса, двунаправленный расширитель шины данных, расширитель шины управления памятью, программно-доступный второму вычислителю регистр вывода, первый и второй элементы И, причем информационные входы дешифратора доступа и расширителя шины а-дреса, первые информационные входы-выходы расширителя шины данных, триггер запроса захвата и регистр ввода, информационные входы расширителя управления памятью связаны соответственно с шинами адреса, данных и управления памятью первого программно-управляемого интерфейса первого вычислителя, информационные входы расширителя шины адреса, вторые информационные входы- выходы расширителя шины данных и регистр ввода, информационные выходы расширителя шины управления памятью связаны соответственно с шинами адреса, данных и управления памятью второго программно- управляемого интерфейса второго вычислителя, управляюшие входы расширителей шины адреса и шины данных связаны с выходом дешифратора доступа, вход направления передачи расширителя шины данных - с

первым информационным входом расширителя шины управления памятью, управляющие входы дешифратора доступа и расширителя uiHb b управления памятью, первые входы первого элемента И и регистра ввода - с выходом триггера управления доступом, перзый вход второго элемента И и второй вход регистра ввода - с вторым выходом регистра вывода, второй вход второго элемента И - с выходом триг- тера запроса захвата, выход первого элемента И, первый выход регистра вывода и установочным вход триггера управления доступом - с первой группой управ,1яю- щих входов-выходов первого вычислителя, второй вход лервого элемента И, выход второго элемента И и информационный вход триггера управления доступом - с второй группой управляющих входов-выходов второго вычислителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для связи процессоров | 1986 |

|

SU1481785A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Многопроцессорная система | 1988 |

|

SU1605247A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| СПОСОБ ФИЛЬТРАЦИИ МЕЖПРОЦЕССОРНЫХ ЗАПРОСОВ В МНОГОПРОЦЕССОРНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМАХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2189630C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

Изобретение относится к технике автоматического управления и может быть использовано для управления технологическим процессом переработки пластмасс методом литья под давлением в химической промышленности, машиностроении и является усовершенствованием известного устройства по N1164056. Целью дополнительного изображения является расширение функциональных возможностей устройства по управлению процессом литья под давлением изделий из пластмасс. Для этого устройство дополнительно содержит связанный посредством блока межпроцессорной связи многоканальный регулятор температуры зон обогрева материального цилиндра, включающий датчики температуры, блок тиристорных ключей и нагревательные элементы, а также объединенные вторым программно-управляемым интерфейсом второй вычислитель, второй блок аналого-цифрового преобразования, входы которого связаны с выходами датчиков температуры, и блок управления обогревом, выходы которого через блок тиристорных ключей связаны с нагревательными элементами, причем первые информационные входы-выходы блока межпроцессорной связи соединены с первым программно-управляемым интерфейсом первого вычислителя, вторые - со вторым программно-управляемым интерфейсом второго вычислителя, первая группа управляющих сигналов - с первой группой управляющих входов-выходов первого вычислителя, вторая - с второй группой управляющих входов-выходов второго вычислителя. 2 з.п. ф-лы, 4 ил, 2 табл.

14емтра ь ой вН .1

/г ffjroKi/ 22

/у.

27

/V/

/

J/ 61

I ШУ

ШМ

i3

28

t-i-п

z.

4

ШД

ШД

ШД

2S

5g/7yOgg прерь18ония npoBep; 2j;

7

iicrriaHo6 ajo E :: fi

12

15

14

С /7 3

Второй вычислитель

| Устройство управления литьевой машиной | 1983 |

|

SU1164056A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1990-11-30—Публикация

1988-12-20—Подача