05

Ф оо со

Изобретение относится к измерительной технике и нредназначено для измерения формы широкополосных электрических сигналов с большим динамическим диапазоном.

Целью изобретения является увеличение дннамического дианазона и повын ение быстродействия.

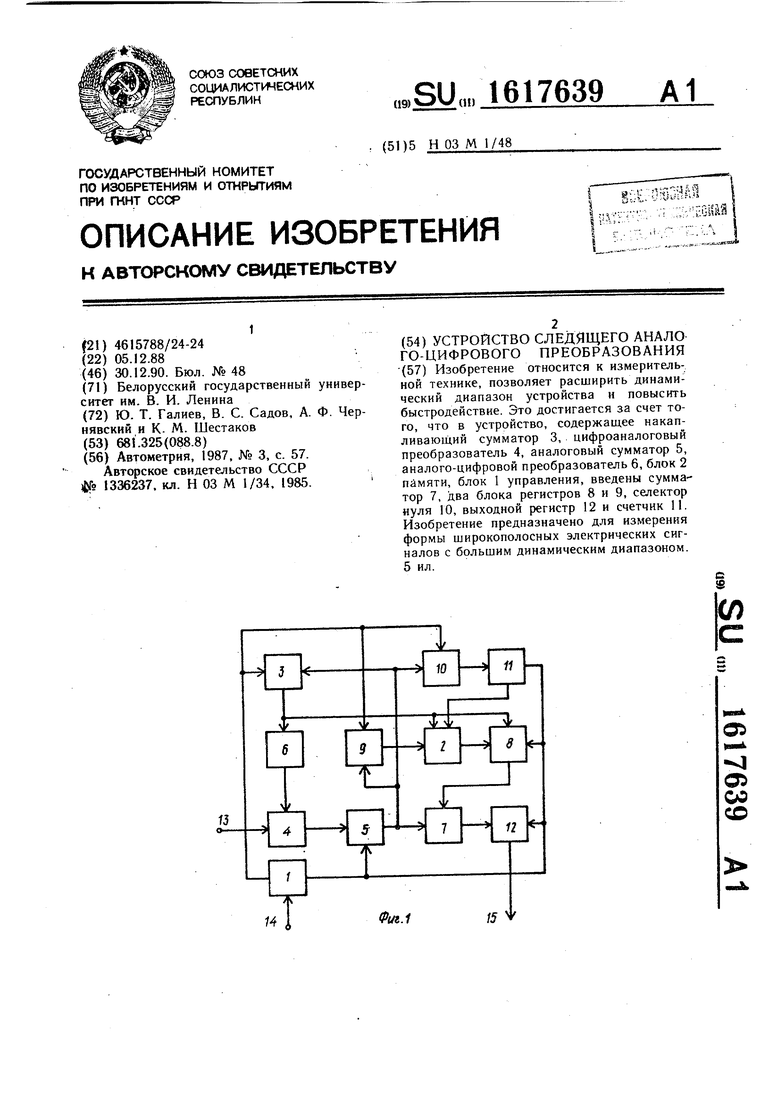

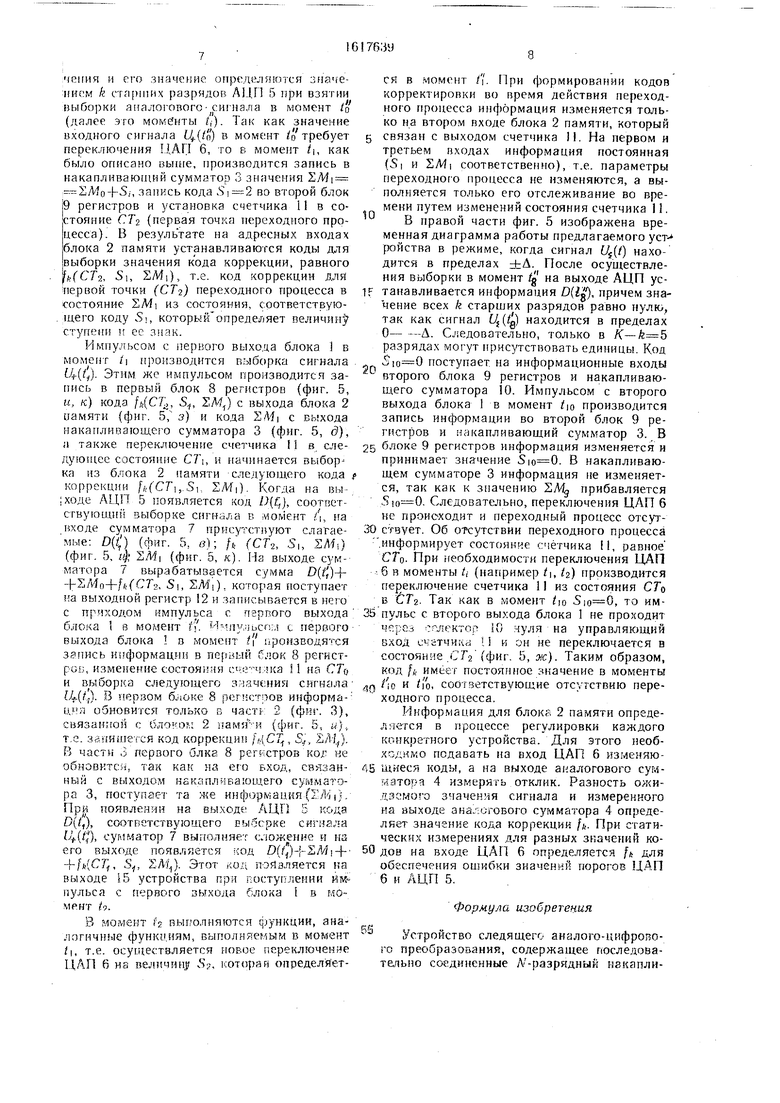

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - схема накапливающего сумматора; на фиг. 3 - схема блока регистров; ка фиг. 4 и 6 - вре- менние диаграммы работы устройства.

Устройство содержит блок 1 управления/ блок 2 памяти, накапливаюа1,ий сумматор 3, аналоговый сумматор 4, аналого-цифровой преобразователь (АЦП) 5, цифроаналого- вый преобразователь (ЦАП) 6, сумматор 7, первый 8 и второй 9 блоки регистров, селектор 0 нуля, счетчик П, выходной регистр 12, выходную шину 13 аналогового сигнала, входную шину 14 запуска и выходную шину 5.

Накапливающий сумматор 3 (фиг. 2) реализован на сумматоре 16 и регистре 17.

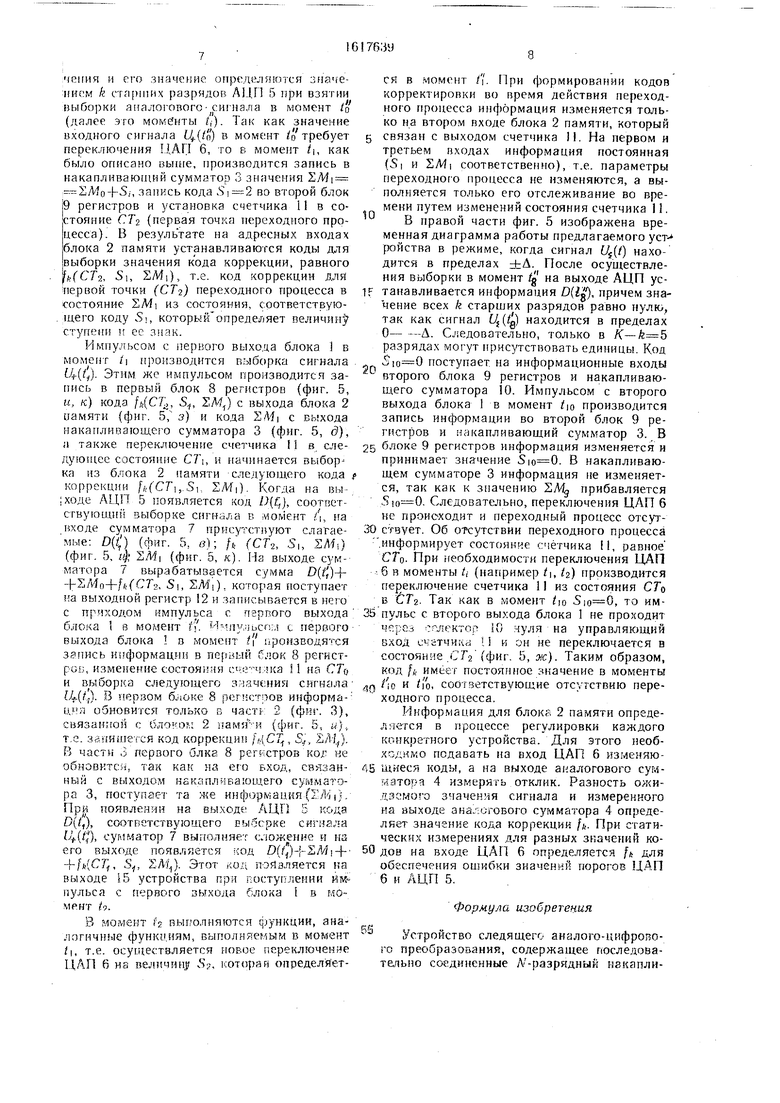

На фиг. 4 обозначены: t (с соответ- ствуюи ей индексацией) - моменты дискретизации входного сигнала; а и б - сиг- налы с первого и второго выходов блока 1 управления; - ) сигнал на шине 13 устройства; ( (/) t4. ()-i-/7(0 - сигнал на входе АЦП 5; LL (t) -- составляющая сигнале (У (I), определенная входным кодом ЦАП 6; А - напряжение, соответ- ствующее шагу квантования Ц.АП 6; п - начальное значение кода на выходе накапливающего сумматора 3; fk(CTi, S,-, ЕЛ4,-) - код коррекции на выходе блока 2 памяти; CTi, Si, SAf/ - составляющие адреса блока 2 памяти от счетчика П, второго блока 9 ре- гистрок н кйкйпливзющего сулгматора соответственно; -Of) --- коды ла выходе АЦП 5; ДО+/А -- откорректированные значения кодов АЦП (составляющая выходного кода).

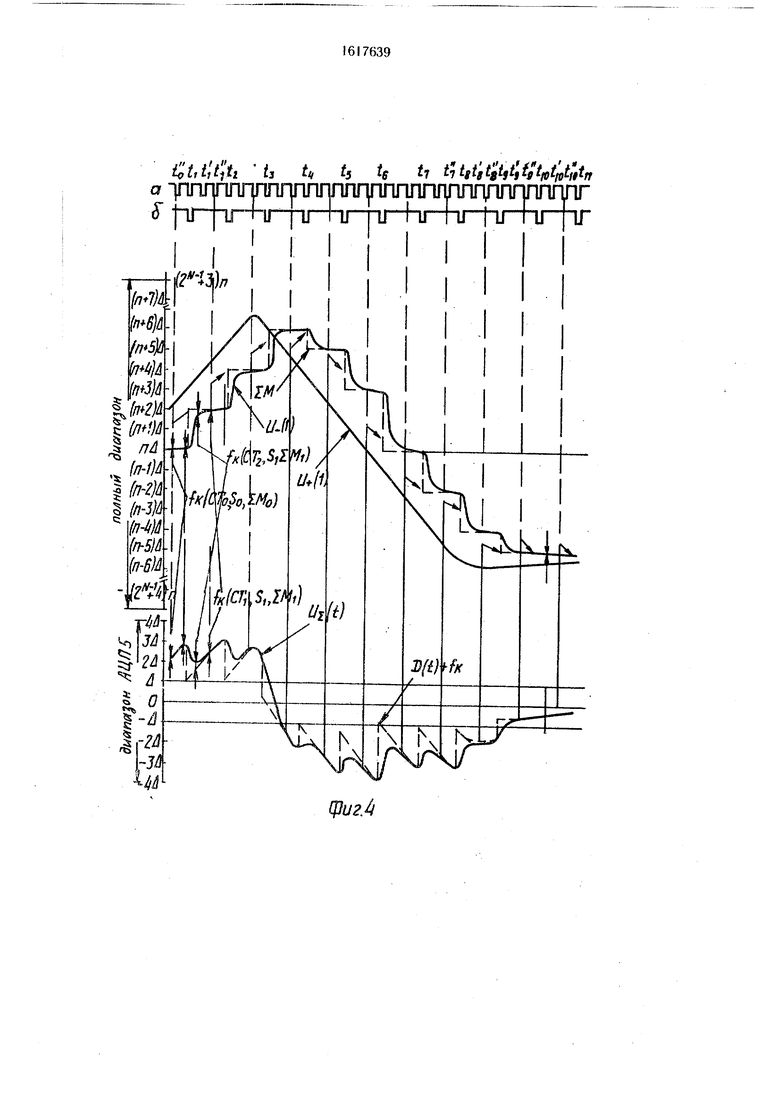

Иа фиг. 5 обозначения а и б соответст- пуют сигналам на первом и втором выхо.цах блока ; обозначение и - части 2 (фиг. 3) ВЫХОДИ первого блока 8 регистров, т.е. информации, передаваемой из блока 2 памяти; обозна1 ение /г - части 3 (фиг. 3) выхода первого блока 8 регистров, т.е. информа- ции, передаваемой из накапливающего сумматора 3; на диаграмме, соответствующей обозначению а, представлено «aMeHeHHe ин- формации ив /( выходах АЦП 5; на диаграм ме, соответствующей обоз1 ачению г, пред-, ставлено изменение информации на /с стар- щих разрядах АЦП 5.

, В предлагаемом устройстве разрядность К АЦП 5 равна 8, разрядность Л/ ЦАП б равна id, причем м.падщий значащий разряд (пераьж) ЦАП 6 соответствует цене шесто Ч ) разряда АЦП 5, а второй разряд - седьмому разряду АЦП 5. Если старший разряд А1.1,Г1 5 (восьмой) является знаковым

j-

Ю

15 20

jg зс 3F

5 0

5

Ш

разрядом, то Oil подключается к знаковому разряду ЦАП 6. Если АЦП 5 не имеет зна- .кового разряда, то восьмой (старший) разряд подключается к третьему значащему разряду 6. В обоих случаях разрядность предлагаемого устройства составляет

N+(K+k),

где k - количество совмещенных разрядов.

В данном примере (б-й, 7-й и 8-й

разряды АЦП), т.е. разрядность устройства

N+()) l5.

Так как k составляет 3 разряда, то диа- пазон АЦП 5 разбивают на 8 поддиапазонов (фиг. 4). Принято, что старший разряд АЦП 5 является знаковым.

; Устройство работает следующим образом.

В пачальном состоянии блоки регистров 8 и 9, выходной регистр 12 и счетчик П установлены в «О (цепи сброса не показаны). В регистре 17 накапливающего сумматора находится код числа п, который устанавливает значение сигнала Uf(t) в диапазон АЦП 5 (цепи записи в регистр 17 начального значения не показаны).

При поступлении сигнала «Запуск на вход 14 устройства блок 1 управления начинает вырабатывать сигналы а к б. По сигналам а производятся.выборки аналогового сигнала АЦП 5. При осуществлении выборки в момент to (. 4 и 5) на вход АЦП 5 поступает сигнал

U(to)--i4(t )-U,(to),

где f.4 (Q - значен ие входного сигнала в момент /о ;

bL(t{)) - аналоговый эквивалент кода SA, установленного на выходе накапливающего сумматора 3 (фиг. 5, д.

Через время задержки на выходе АЦП 5 (фиг 5, в) появляется код D(to), который является цифровым эквивалентом значения сигнала U (fn). Так как входной аналоговый сигнал Uf(t) отличается от значения Ал на величину больше, чем 2Д (фиг 4), то . и на входе АЦП 5 сигнал Uf.(to) отличается от значе1;кя О на величину больше чем 2А. Следовательно, значение трех () старших разрядов АЦП 5 (фиг. 5, 3) отлично от нуля, или в двоичном коде 010. На первый адресный вход блока 2 памяти поступает информация с выхода второго блока 9 регистров. В данном случае блок 9 регистров реализован на одном регистре. Блок 9 регистров установлен в «О, и код на его выходе равен 0. На второй адресный ВХО.Д блока 2 памяти поступает код с выхода счетчика П, причем .этот код имеет значение О, т.е. СТп. Счетчик 11 выполняет функцию счетчика времени переходного процесса. Его количество состояний определяется отношением быстродействия цепи ЦАП 6 - аналоговый сумматор 4 и АЦП 5, т. е. отношением частот на первом и втором выходах блока 1.

Частота на первом выходе блока I превышает частоту на втором выходе в 3 раза, т.е. количество возможных состояний счетчика должно быть не менее 3-х, что обеспечивается двухразрядным двоичным счетчиком. Код СТо на выходе счетчика II информирует о том, что переходный процесс в цепи ЦАП 6 - аналоговый сумматор 4 отсутствует. Код на выходе счетчика соответствует первой точке переходного процесса, код СТ| 1 - второй точке переходного процесса.

Таким образом, в начальном установившемся состоянии переходный процесс отсутствует и на выходе счетчика 11 установлен код СТо (он сброшен). Импульс с первого выхода блока 1, поступаюш,ий в момент о, не изменяет состояния счетчика, так как он уже находится в состоянии «О.

На третий адресный вход блока 2 памяти поступает информация с выхода накапливающего сумматора 3, т.е. код . В итоге на выходе блока 2 памяти присутствует код коррекции, определяемый следующими значениями: SMo, что соответствует состоянию ЦАП 6 в момент /о; СТо, что со- ответс-1;вует отсутствию переходного процесса; , что соответствует отсутствию переключения ЦАП 6, т.е. на выходе блока 2 памяти присутствует код fk(CTo, So,-SMo), который может быть отличным от нуля и в случае отсутствия переходного процесса и представлять собой необходимую коррекцию нелинейности цепи ЦАП 6 - аналоговый сумматор 4, что снижает требования к точности этой цепи. Импульсом в момент /о производится запись кода коррекции fk(CTo, So, I.Mo) и кода с выхода накапливающего сумматора SMo в первый блок ре- .лисгров (фиг. 3), которые вместе с кодом ) поступают на входы сумматора 7, появ-. ляется код суммы D(to)+ EMf,-}-fk(CTQ, So; ), причем каждое слагаемое представлено в дополнительном коде и может быть как положительным, так и отрицательным. Импульсом с первого выхода блока 1 в момент /I производится запись кода с выхода сумматора 7 в выходной регистр 12, и на его выходе появляется цифровой эквивалент входного сигнала, равный D(io) -i-fk(CTo, So, SAJoj- Тем же импульсом в мо-. мент /1, производится следующая выборка аналогового сигнала U(t). В момент t на выходе АЦП 5 еще присутствует инфор-. мдция о прошлой выборке, т.е. на k стар- yjHX разрядах присутствует код Si 2. В момент/1 вырабатывается импульс на втором

выходе блока I, который задним фронтол

() производит запись в регистр 17

кода с выхода сумматора 16, равного I.. S/Mo+Si n+2, и запись кода Si 2 во

второй блок 9 регистров. Так как S отлично от нуля, то импульс с второго выхода блока 1 проходит через селектор 10 нуля и поступает на вход управления счетчика 11. Под воздействием импульсов на входе управления и тактовом входе производится установка счетчика П в состояние СТ- (фиг. 5, ж). Коды S, СГг и SAf 1 поступают на первый, второй и третий входы блока 2 памяти соответственно, который начинает выборку следующего кода коррекции fk(CT2, S, SM).

5 Но в момент t на выходе блока 2 памяти еще присутствует старший код коррекции (фиг. 5, з), который в момент t совместно со старым кодом 2Мо записывается в первый блок 8 регистров (фиг. 5, и, к). Таким образом, после появления на выходе АЦП 5 ко да выборки, соответствующего моменту ti, на выходе сумматора 7 появляется код D(ti)+ LMo+fk(CTo,SQ, I.Mo), т.е. переход- ны процесс еще отсутствует; составляющая Ц(/)пД, что соответствует коду SMo;

5 переключения не происходило fSo. При поступлении на вход ЦАП 6 кода SMi на его выходе начинает изменяться напряжение. . По окончании переходного процесса составляющая tI(/2) равна (л4-2)Д. Во время действия переходного процесса АЦП 5 про0 должает производить выборки входного сигнала в моменты /1 и /2. После импульса в момент t на выходе накапливающего сумматора 3 уже присутствует новое значение суммы SMi, а на вход АЦП 5 поступает сигнал U(t), искаженный переходным процес5 сом цепи ЦАП 6 - аналоговый сумматор 4 (U(t)}. Следовательно, цифровые йоды на выходе АЦП 5 также искажены. Для получения на выходе устройства истинного цифрового эквивалента входного аналогового сигнала необходимо производить коррекцию кодов, поступающих с АЦП 5. Значения кодов fk определяются характером кривой переходного процесса, которая определяется состоянием ЦАП б до переключения и со- . стоянием ЦАП 6 после переключения. Кри45 вая переходного процесса, кроме этого, является функцией времени. Коды коррекции записаны в блоке 2 памяти и однозначно определяются тремя изложенными выше параметрами. Состояние ЦАП 6 после переключения определяется выходом накаплива50 ющего сумматора 3 (в данном случае это код 2Mi); .состояние ЦАП 6 до переключения задается значением k старших выходных разрядов АЦП 5 (в данном случае это код Si). Код Si определяет значение ступени переключения. Этим задается кри- вая переходного процесса. Изменение ее во

времени определяется значением кода на выходе счетчика 11. Необходимость переключекия и его значе ие определяются зпяче- k стлрших разрядов ЛЦП 5 при взятии выборки аналогового- сигнала в момент /о (далее это ,). Так как значение входного сигнала Ц.( в момент Стребует переключения ДАП 6, то в момент t, как было описано выиге, производится запись в накапливающий сумматор 3 значения E/V}i : -2-Л 10-Ь5,-, занксь кода во второй блок 19 регистров и установка счетчика 11 в состояние СТу, (первая точка переходного процесса). В результате на адресных входах блока 2 памяти устанавливаются коды для выборки значения кода коррекции, равного р,(СТ-2, Si, SMi), т.е. код коррекции для тюрвой точки (СТ) пере.ходного процесса в состояние ЕМ из состояния, соответствующего коду S, который определяет величину ступени и ее знак.

Импульсом с iiepBoro выхода блока 1 в MOMetrr ii производится выборка сигнала U(if). Этим же импульсом производится запись в первый блок 8 регистров (фиг. 5, и, к) кода /(С7;,, 5, 1:М) с выхода блока 2 цамяти (фиг. 5, з) и кода SMj с выхода накапливающего сумматора 3 (фиг. 5, д), а также переключение счетчика 11 в следующее состояние C7 i, и начинается выбор ка из блока 2 памяти следующего кода коррекции ftfCTij.Si, SA d). Когда на вы- ;ходе АЦП 5 появляется код /J(f,), соответ- ствующи выборке сигнала в люмент i, на входе сумматора 7 присутетнуют слагаемые: D(/;) (фиг. 5, в); fk (СГг, S,, lAf,) (фиг. 5, 1ф I,MI (фиг. 5, к). На выходе сумматора 7 вырабатывается сумма D(t ,)+ -|-SAio4 ffc(CT2, S|, SvWi). которая поступает на выходной регистр 12 и записывается в него с приходом импульса с первого выхода блока I в момент ь Импу:иьсп;л с первого выхода блока в момент /( производятся ззпись информации в первый блок 8 регист- POD, изменение состояния сч Г:-ч; ка 11 на СТ(, и (а следующего Зг ачения сигнала lL(i,}. В iiepBOM блоке 8 репзстров информац . л обновится только в 2 (фиг. 3), связан го и с блок 2 (фиг. 5, м) т.е. запишется код коррекции /мСТ, 5.,, S/li,). В- части 3 первого блка 8 регистров ког не обновитси. так как на его вход, связанный с выходом НБкаалнБа:ощего сумматора 3, поступает та же инфорл ааия/ГЛ ;). При появлении на выходе АЦП 5 кода D((,), соответствующего Еыбсрке сигнала и.(ф, суг ,1матор 7 выполняет сложение и иа его выходе появляется код D(, ) -{-fi,(CT, S, SAf.,). Зтот код появляется на выходе 15 устройства при поступлении й№ пульса с первого зыхода блока 1 в момент (у.

В момент I j выполняются функции, аналогичные функциям, выполняемым в момент /I, т.е. осуи есталяется новое переключение ЦАП 6 на величин S-j, itOTOpae определяет0

Си в момент t . При формировании кодов корректировки во время действия переходного процесса информация изменяется только на втором входе блока 2 памяти, который

связан с выходом счетчика II. На первом и третьем входах информация постоянная (5| и S/MI соответственно), т.е. параметры переходного процесса не изменяются, а выполняется только его отслеживание во времени путем изменений состояния счетчика 11. В правой части фиг. 5 изображена временная диаграмма работы предлагаемого уст ройства в режиме, когда сигнал Uf(t) нахо- дится Б пределах ±А. После осуществления выборки в момент tg на выходе АЦП устанавливается информация О(ф, причем значение всех k старщих разрядов равно нулю, так как сигнал Ц(д) находится в пределах

ОД. Следовательно, только в

разрядах могут присутствовать единицы. Код

р поступает на информационные входы второго блока 9 регистров и накапливающего сумматора 10. Импульсом с второго выхода блока 1 в момент производится запись информации во второй блок 9 регистров и накапливающий сумматор 3. В

5 блоке 9 регистров инфор.мация изменяется и принимает значение . В накапливающем сумматоре 3 информация не изменяется, так как к значению 2А прибавляется . Следовательно, переключения ЦАП 6 не происходит и переходный процесс отсут0 ствует. Об отсутствии переходного процесса

.информирует состояние счётчика 1, равное

СГо. При необходимости переключения ЦАП

-.6 в моменты /, (например t, iz) производится

переключение счетчика 11 из состояния СГо

Б tTg. Так как в момент tto , то им5 пульс с второго выхода блока 1 не проходит через сгхлектор 10 нуля на управляющий вход счетчика 11 и он не переключается в состояние .СГ2 (фиг. 5, ж}. Таким образом, код fi, имеет постоянное значение в моменты

Q / о и t l o, соответствующие отсутствию переходного процесса.

Информация для блока 2 памяти опреде- ляегся в процессе регулировки каждого конкретного устройства. Для этого необходимо подавать на вход ЦАП 6 изменяю5 щиеся коды, а на выходе аналогового сумматора 4 измерять отклик. Разность ожидаемого значения сигнала и измеренного на выходе аналогового сумматора 4 определяет значение кода коррекции /. При статических измерениях для разных значений ко0 дов иа входе ЦАП 6 определяется f для обеспечения ошибки значений порогов ЦАП 6 и АЦП 5.

Формула изобретения

Устройство следящего аналого-цифрового преобразования, содержащее последовательно соединенные Л -разрядный накапливающий сумматор, /V -разрядный цифроана- логовый преобразователь, аналоговый сумматор, /(-разрядный аналого-цифровой преобразователь, вход синхронизации которого соединён с перрым выходом блока управления, второй выход которого соединен с управляющим входом Л -разрядного накапливающего сумматора, а вход является щиной «Пуск, блок памяти, второй вход аналогового сумматора является входной шиной, отличающееся тем, что, с целью повышения быстродействия и увеличения динамического диапазона, введены сумматор, два блока регистров, селектор нуля, счетчик, выходной регистр, тактовый вход которого объе динен с тактовыми входами счетчика и первого блока регистров и подключен к первому выходу блока управления, второй выход которого соединен с тактовым входом второго блока регистров и селектора нуля, k информационных входов которого объединены, с соответствующими информационными входами накапливающего сумматора и соответствующими информационными входами второго блока регистров и подключены к выходам k старших разрядов К-разряд- ного аналого-цифрового преобразователя, выходы которого соединены с соответствующими первыми ин формационными входами сумматора, вторые информационные входы которого соединены с соответствующими выходами первого блока регистров, первые информационные входы которого соединены с соответствующими выходами блока памя0 ти, nepBbie адресные входы которого соединены с соответствующими выходами второ-. го блока регистров, вторые адресные входы соединены с соответствующими выходами счетчика, вход управления которого соедис нен с выходом селектора нуля, третьи адресные входы блока памяти объединены с соответствующими вторыми информационными входами первого блока регистров и подключены к соответствующим выходам N- разрядного накапливающего сумматора, вы0 ходы сумматора соединены с соответствующими входами выходного регистра, выходы которого являются выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| Синтезатор частот | 1987 |

|

SU1467738A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1562972A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1451856A1 |

| Аналого-цифровое устройство | 1981 |

|

SU1018239A1 |

Изобретение относится к измерительной технике. Изобретение позволяет расширить динамический диапазон устройства и повысить быстродействие. Это достигается за счет того, что в устройство, содержащее накапливающий сумматор 3, цифроаналоговый преобразователь 4, аналоговый сумматор 5, аналого-цифровой преобразователь 6, блок 2 памяти, блок 1 управления, введены сумматор 7, два блока регистров 8 и 9, селектор нуля 10, выходной регистр 12 и счетчик 11. Изобретение предназначено для измерения формы широкополосных электрических сигналов с большим динамическим диапазоном. 5 ил.

Фи.г

Щи.

t, t, ts te ti tittt ,tit,t ,

пгртлллгр шп

J..L.jТi L

u и I u nj ni TU

u

И4: /7 5j/l- ,И |M4

I

I

, 1п-1)Л. 5 {П-2)й

§ (п-т (п-Ш - (п-Ш

.

u

а S

8

г S е ж

3

и

i fc4i±±tt±±±44 - -T -vvv-f лллллл-

j

ZDQ

« Х

w,t

/{П.

.«М}. Фиг. 5

w,t

/{П.

.«М}. Фиг. 5

sft,) Щ МСТо,

.Щ)

| Автометрия, 1987, № з, с | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-12-30—Публикация

1988-12-05—Подача