89

10

Фиг.1

10 и второй 11 информационные выходы (микроопераций). В устройстве первый и второй блоки формирования адреса микрокоманды работают параллельно и синхронно, на первый подается от блока синхронизации частота f, на зтарой - частота f, причем отношение частот - любое число больше 1 о Это увеличивает быст- ро ействие устройства, поскольку снимает с первого блока формирования адреса микрокоманды, отвечающего за общее управление устройством и. имеющего сложную структуру и ограниченное быстродействие., функции оперативного управления и передает его более простому и быстродсйствующему второму блоку формирования адреса микрокоманды. Распределение разрядов микрокоманды между первой и второй памятью микропрограмм, пер- вык и вторым регистрами микрокоманд

позволяет аппаратно разделить логически несовместимые поля микрокоманды и устранить повторные фрагменты микропрограммы, сократить за счет этого память микропрограмм. 2 з.п.

ф-лы, 7 фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1119021A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2020559C1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1667068A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1259262A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1091160A1 |

Изобретение относится к вычислительной технике, а точнее к облас( ти микропрограммного управления цифровыми устройствами, и наиболее эффективно может быть использовано в вычислительных и управляющих сиете™ мах высокого быстродействия, имеющих большой объем микропрограммного обеспечения. Цель изобретения - повышение быстродействия микропрограммного устройства управления и сокращение памяти микропрограмм - достигается за счет распараллеливания управления между двумя модулями микропрограммного управления и их синхронной работы. Устройство содержит первый блок 1 формирования адреса микрокоманды, первый блок 2 памяти микропрограмм, первый регистр 3 микрокоманд, второй блок 4 формирования адреса микрокоманды, второй блок 5 памяти микропрограмм, ВТОРОЙ регистр 6 микрокоманд, блок 7 синхронизации, вход 8 кода операции, вход 9 логических условий, первый (Я

Изобретение относится к вычислительной технике, а точнее к области микропрограммного управления цифровыми устройствами, и наиболее эффективно может быть использовано в вычислительных и управляющих система;: высокого быстродействия, имеющих большой объем микропрограммного обеспечения.

Целью изобретения является повышение быстродействия микропрограммно го устройства управления и сокращение памяти микропрограмм.

В устройстве первый и второй блоки формирования адреса микрокоманды работают параллельно и синхронно, на первый подается от блока синхронизации частота ff, на второй - частота f, причем отношение частот Јд /f - любое число больше 1. Это увеличивает быстродействие устройства, поскольку снимает с первого блока формирования адреса микрокоманды, отвечающей за общее управление устройством и имеющей сложную структуру и ограниченное быстродействие, функции оперативного управления и передает его более простому и быстродействующему второму блоку формиро- , вания адреса микрокоманды. Распределение разрядов микрокоманды между первой и второй памятью микропрограмм, первым и вторым регистром микрокоманд позволяет аппаратно разделить логически несовместимые поля микрокоманды и устранить повторные фрягменты микропрограммы, сократить з счет этого память микропрограмм.

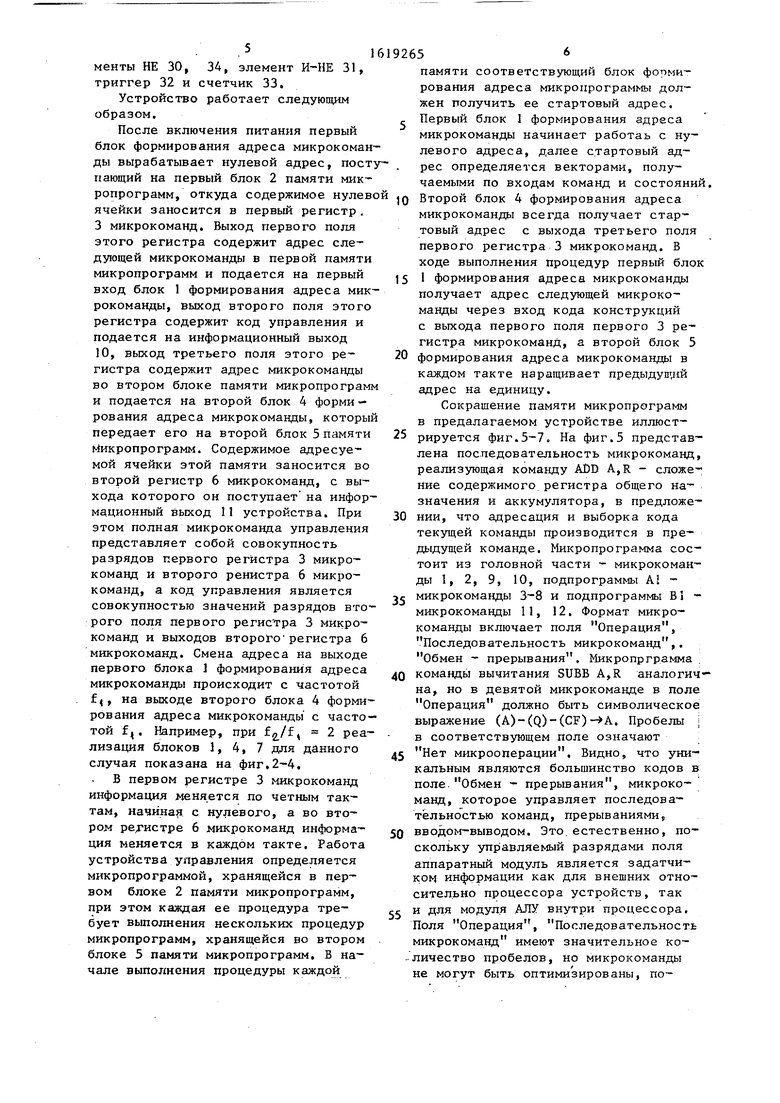

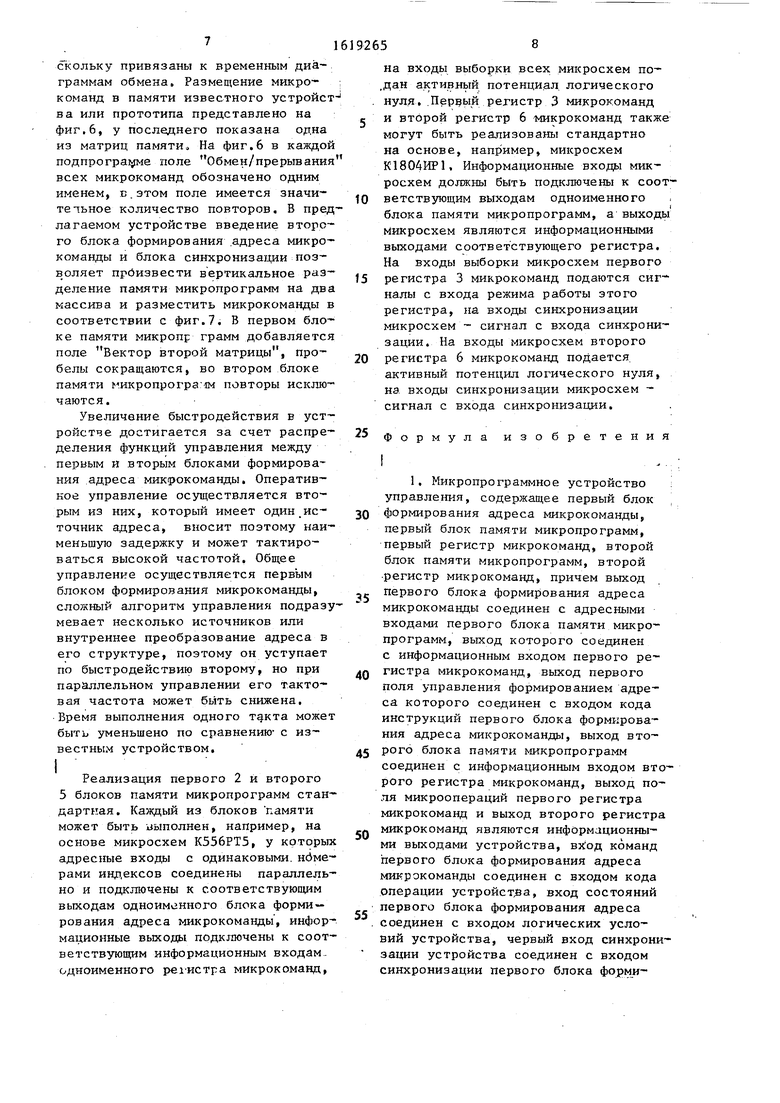

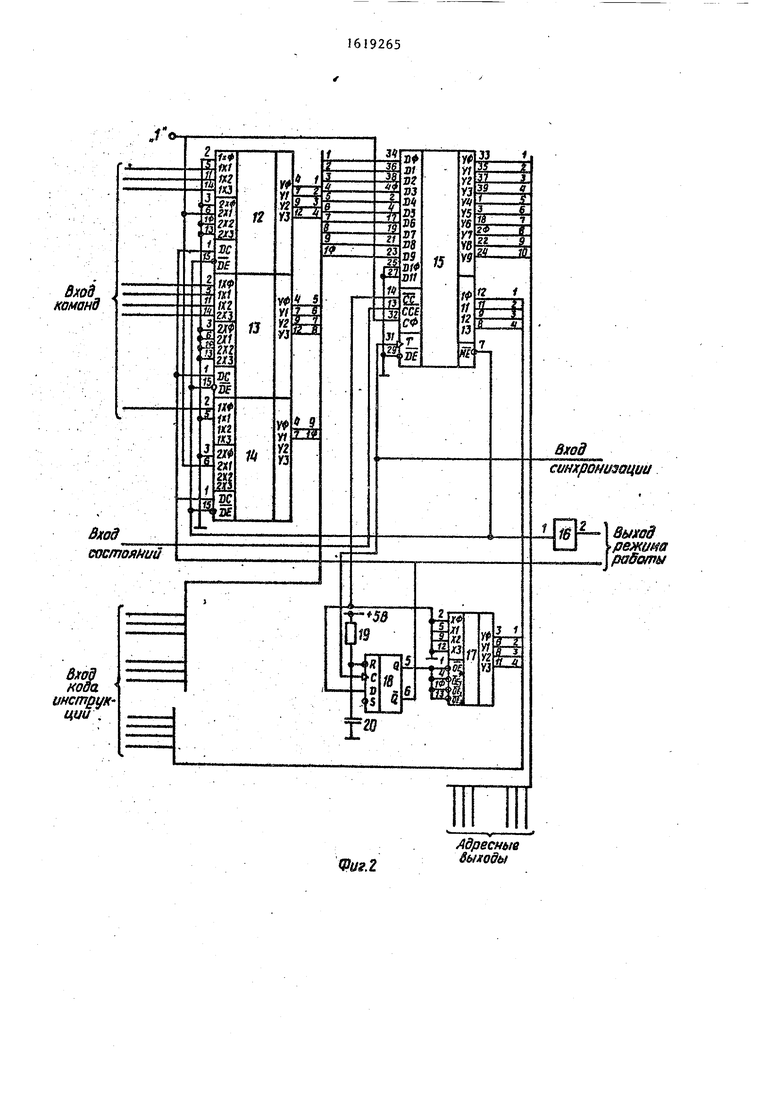

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - схема первого блока формиро- вания адреса микрокоманды; на фнг.З - блок синхронизации; на фиг.4 - схема второго блока формирования адреса микрокоманды; на фиг.5 - алгоритм работы устройства; на фиг,6, 7

схема распределения информации в

блоках памяти микрокоманд.

Микропрограммное устройство управления (фиг.1) содержит первый блок 1 формирования адреса микрокоманды, первый блок 2 памяти микро- программ, первый регистр 3 микрокоманд, второй блок 4 формирования адреса микрокоманды, второй блок 5 памяти микропрограмм, второй регистр 6 микрокоманд, блок 7 синхронизации, вход 8 кода операции, входы 9 логи-, ческих условий, первый JO и второй 11 инф мационные выходы (микроопераций) .

Первый блок 1 формирования адреса микрокоманды (фиг.2) содержит с первого по третий мультиплексоры 12-14, схему 15 формирояания адреса микрокоманды, элемент НЕ 16, узел 17 ключей с тремя устойчивыми состояниями, триггер 18, резистор 19 и Конденсатор 20.

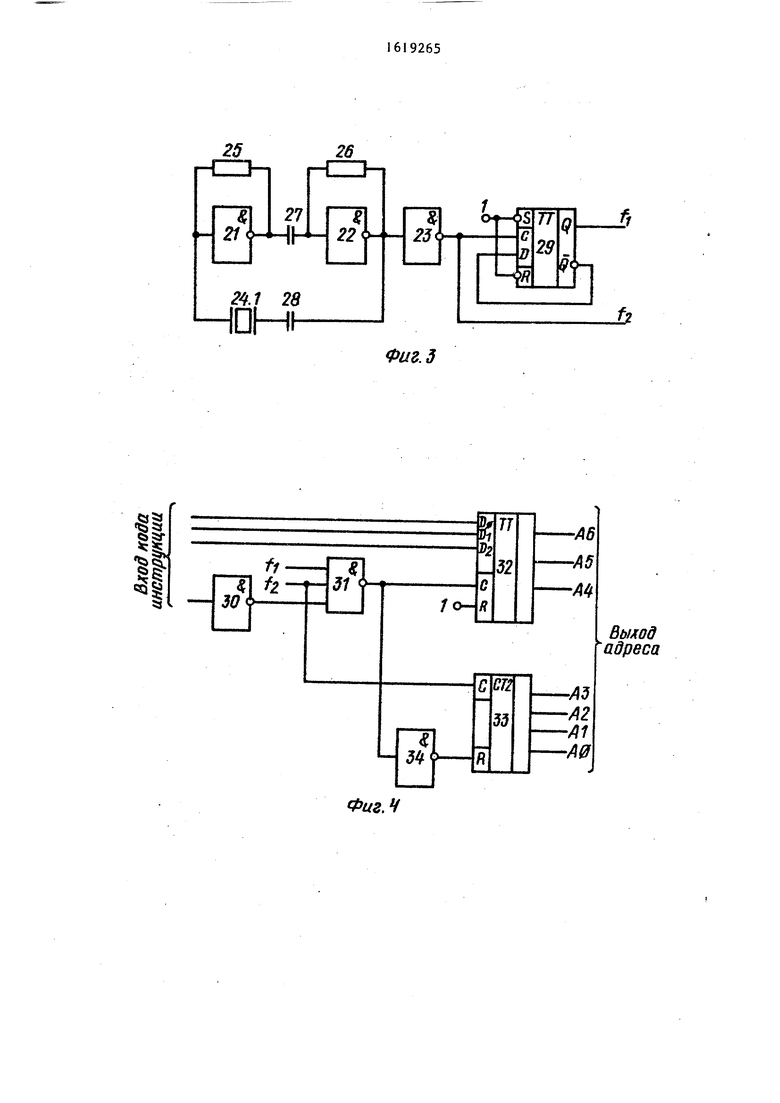

Бпок 7 синхронизации (фиг.З) содержит генератор, включающий в себя элементы НЕ 21-23, кварцевый резона- тор 24, резисторы 25, 26, конденсаторы 27, 28 и триггер 29.

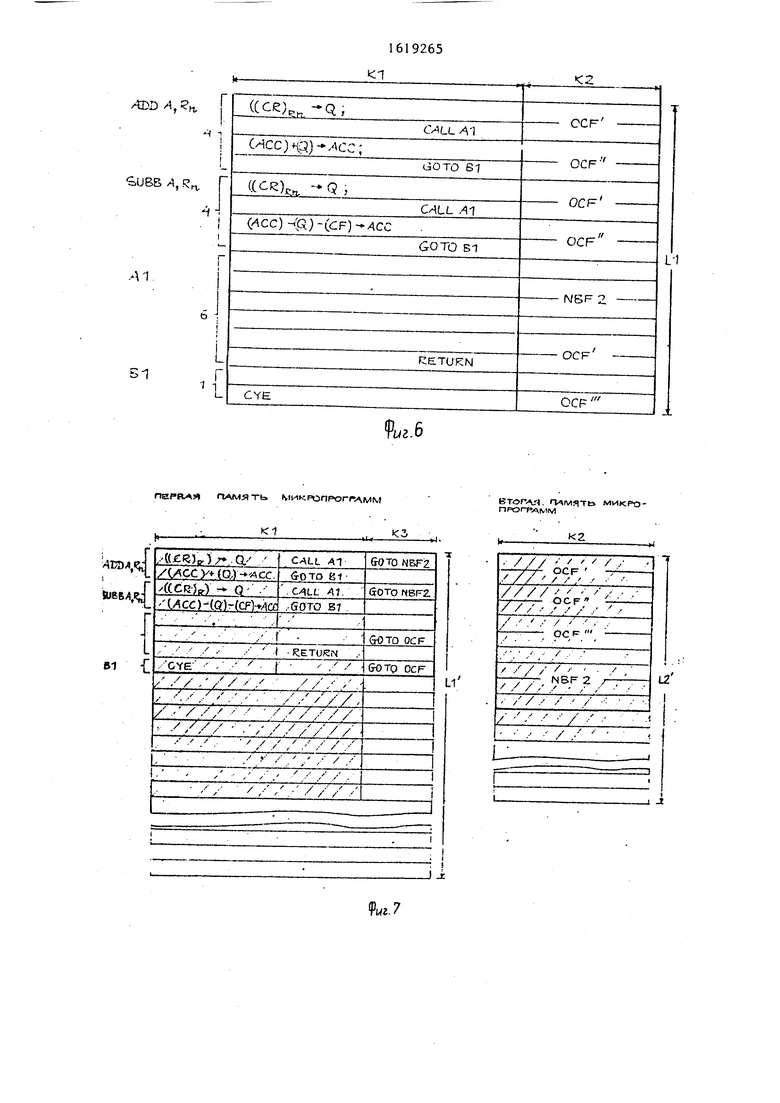

Второй блок 4 формирования адреса микрокоманды (фиг,4) содержит эле5 1

менты НЕ 30, 34, элемент И-НЕ 31, триггер 32 и счетчик 33.

Устройство работает следующим образом.

После включения питания первый блок формирования адреса микрокоманды вырабатывает нулевой адрес, поступающий на первый блок 2 памяти микропрограмм, откуда содержимое нулево ячейки заносится в первый регистр . 3 микрокоманд. Выход первого поля этого регистра содержит адрес следующей микрокоманды в первой памяти микропрограмм и подается на первый вход блок 1 формирования адреса микрокоманды, выход второго поля этого регистра содержит код управления и подается на информационный выход 10, выход третьего поля этого регистра содержит адрес микрокоманды во втором блоке памяти микропрограмм и подается на второй блок 4 форми - рования адреса микрокоманды, который передает его на второй блок 5 памяти Микропрограмм. Содержимое адресуемой ячейки этой памяти заносится во второй регистр 6 микрокоманд, с выхода которого он поступает на информационный выход И устройства. При этом полная микрокоманда управления представляет собой совокупность разрядов первого регистра 3 микрокоманд и второго ренистра 6 микрокоманд, а код управления является совокупностью значений разрядов второго поля первого регис тра 3 микрокоманд и выходов второго регистра 6 микрокоманд. Смена адреса на выходе первого блока формирования адреса микрокоманды происходит с частотой f, на выходе второго блока 4 формирования адреса микрокоманды с частотой fi, Например, при fg/f 2 pea- лизация блоков 1, 4, 7 для данного случая показана на фиг.2-4.

В первом регистре 3 микрокоманд информация меняется по четным тактам, начиная с нулевого, а во втором регистре 6 микрокоманд информация меняется в каждом такте. Работа устройства управления определяется микропрограммой, хранящейся в первом блоке 2 памяти микропрограмм, при этом каждая ее процедура требует выполнения нескольких процедур микропрограмм, хранящейся во втором блоке 5 памяти микропрограмм. В начале выполнения процедуры каждой

2656

памяти соответствующий блок фопми- рования адреса микропрограммы должен получить ее стартовый адрес. Первый блок 1 формирования адреса микрокоманды начинает работаь с нулевого адреса, далее стартовый адрес определяется векторами, получаемыми по входам команд и состояний.

Q Второй блок 4 формирования адреса микрокоманды всегда получает стартовый адрес с выхода третьего поля первого регистра 3 микрокоманд. В ходе выполнения процедур первый блок

5 1 формирования адреса микрокоманды получает адрес следующей микрокоманды через вход кода конструкций с выхода первого поля первого 3 регистра микрокоманд, а второй блок 5

0 формирования адреса микрокоманды в каждом такте наращивает предыдущий адрес на единицу.

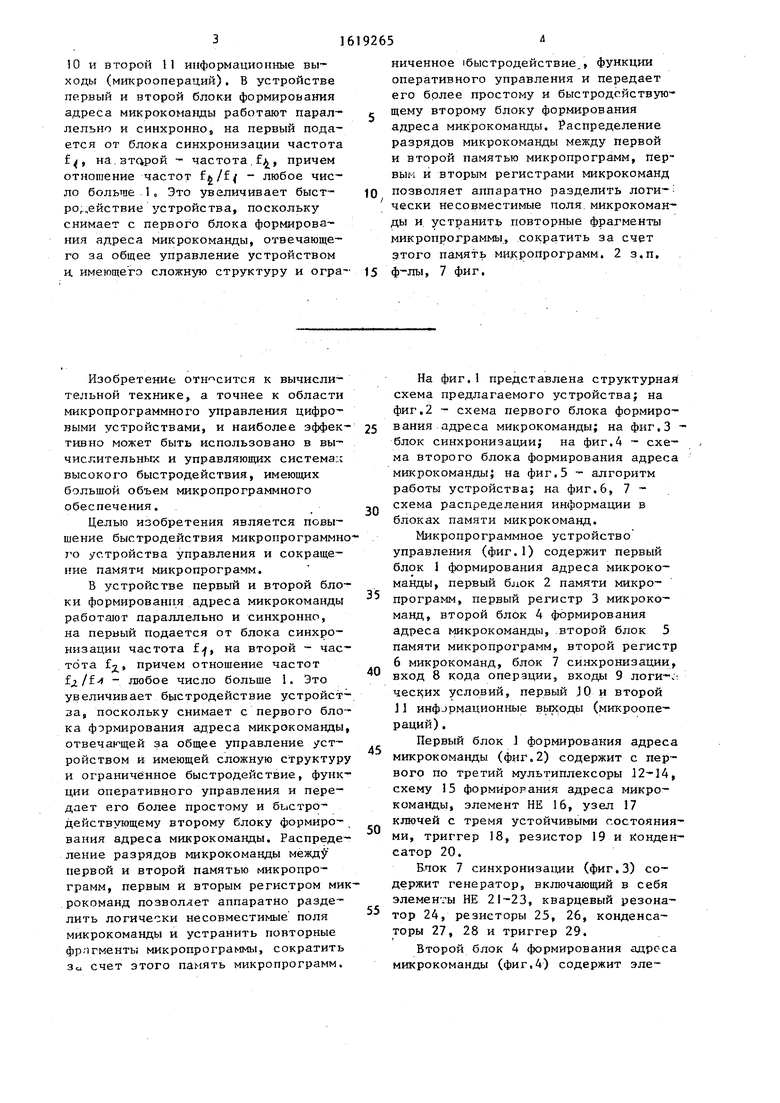

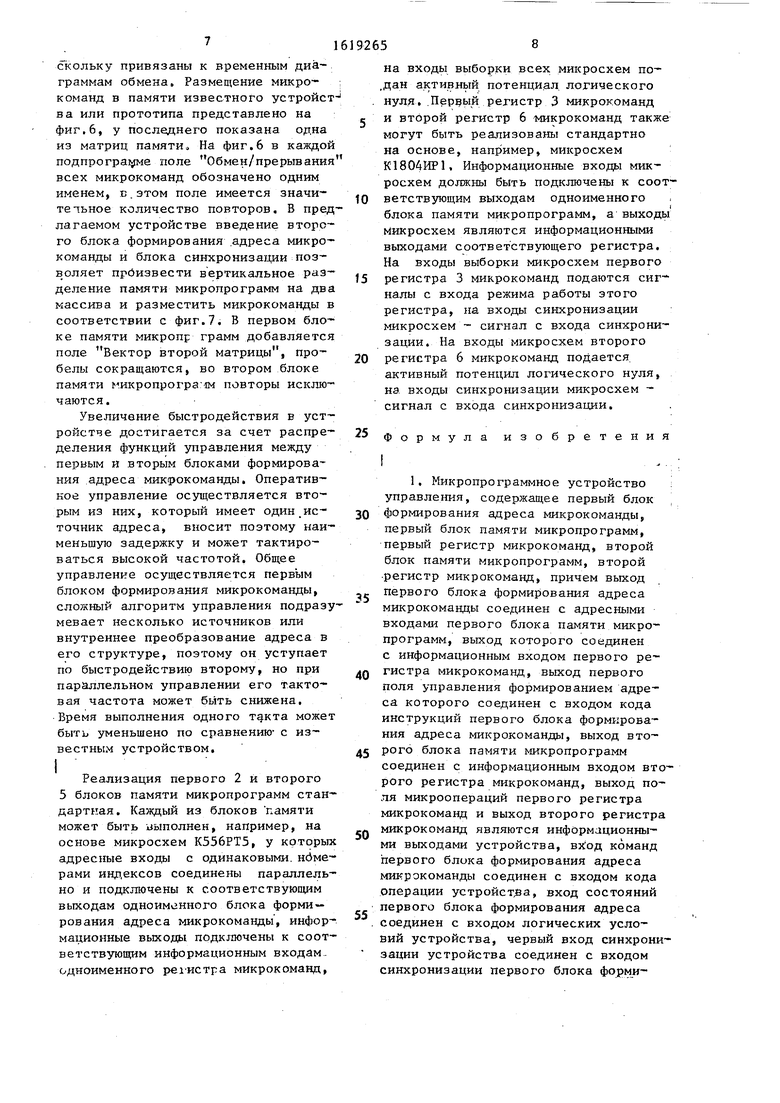

Сокращение памяти микропрограмм в предалагаемом устройстве иллюст-

5 рируется фиг.5-7. На фиг.5 представлена последовательность микрокоманд, реализующая команду ADD A,R - сложение содержимого регистра общего назначения и аккумулятора, в предложе0 нии, что адресация и выборка кода текущей команды производится в предыдущей команде. Микропрограмма состоит из головной части - микрокоманды 1, 2, 9, 10, подпрограммы AJ c микрокоманды 3-8 и подпрограммы В - микрокоманды 11, 12. Формат микрокоманды включает поля Операция, Последовательность микрокоманд,. Обмен - прерывания. Микропрграмма

о команды вычитания SUBB A,R аналогична, но в девятой микрокоманде в поле Операция должно быть символическое выражение (A)-(Q)-(CF) . Пробелы , в соответствующем поле означают

5 Нет микрооперации. Видно, что уникальным являются большинство кодов в поле Обмен - прерывания, микрокоманд, которое управляет последовательностью команд, прерываниями,

0 вводом-выводом. Это естественно, поскольку управляемый разрядами поля аппаратный модуль является задатчи- ком информации как для внешних относительно процессора устройств, так

г и для модуля АЛУ внутри процессора. Поля Операция, Последовательность микрокоманд имеют значительное количество пробелов, но микрокоманды не могут быть оптимизированы, поскольку привязаны к временным диаграммам обмена. Размещение микрокоманд в памяти известного устройст в а или прототипа представлено на фиг.6, у последнего показана одна из матриц памяти На фиг.6 в каждой подпрограмме поле Обмен/прерывания всех микрокоманд обозначено одним именем, Б.этом поле имеется значительное количество повторов. В предлагаемом устройстве введение второго блока формирования адреса микрокоманды и блока синхронизации позволяет произвести вертикальное разделение памяти микропрограмм на два массива и разместить микрокоманды в соответствии с фиг.7. В первом блоке памяти микропр грамм добавляется поле Вектор второй матрицы, пробелы сокращаются, во втором блоке памяти микропрогра -м повторы исключаются.

Увеличение быстродействия в устройстве достигается за счет распределения функций управления между первым и вторым блоками формирования адреса микрокоманды. Оперативное управление осуществляется вторым из них, который имеет точник адреса, вносит поэтому наименьшую задержку и может тактироваться высокой частотой. Общее управление осуществляется первым блоком формирования микрокоманды, сложный алгоритм управления подразумевает несколько источников или внутреннее преобразование адреса в его структуре, поэтому он уступает по быстродействию второму, но при параллельном управлении его тактовая частота может быть снижена. Время выполнения одного такта может быть уменьшено по сравнению- с известным устройством.

Реализация первого 2 и второго 5 блоков памяти микропрограмм стандартная. Каждый из блоков памяти может быть выполнен, например, на основе микросхем К556РТ5, у которых адресные входы с одинаковыми нОме- рами индексов соединены параллельно и подключены к соответствующим выходам одноименного блока формирования адреса микрокоманды, информационные выходы подключены к соответствующим информационным входам одноименного регистра микрокоманд,

на входы выборки всех микросхем по- ,дан активный потенциал логического нуля. Первый регистр 3 микрокоманд и второй регистр 6 микрокоманд также могут быть реализованы стандартно на основе, например, микросхем К1804ИР1, Информационные входы микросхем должны быть подключены к соотO ветствующим выходам одноименного

блока памяти микропрограмм, а выходы Микросхем являются информационными выходами соответствующего регистра. На входы выборки микросхем первого

5 регистра 3 микрокоманд подаются сигналы с входа режима работы этого регистра, на входы синхронизации микросхем - сигнал с входа синхронизации. На входы микросхем второго

0 регистра 6 микрокоманд подается

активный потенция логического нуля, на входы синхронизации микросхем - сигнал с входа синхронизации.

25

Формула изобретения

1, Микропрограммное устройство управления, содержащее первый блок

формирования адреса микрокоманды, первый блок памяти микропрограмм, первый регистр микрокоманд, второй блок памяти микропрограмм, второй регистр микрокоманд, причем выход

первого блока формирования адреса микрокоманды соединен с адресными входами первого блока памяти микропрограмм, выход которого соединен с информационным входом первого регистра микрокоманд, выход первого поля управления формированием адреса которого соединен с входом кода инструкций первого блока формирования адреса микрокоманды, выход второго блока памяти микропрограмм

соединен с информационным входом второго регистра микрокоманд, выход поля микроопераций первого регистра микрокоманд и выход второго регистра

микрокоманд являются информационными выходами устройства, вх од команд первого блика формирования адреса микрокоманды соединен с входом кода операции устройства, вход состояний первого блока формирования адреса соединен с входом логических условий устройства, червый вход синхронизации устройства соединен с входом синхронизации первого блока формирования адреса микрокоманды, с входом синхронизации первого регистра микрокоманд, второй вход синхронизации устройства соединен с входом синхронизации второго регистра микрокоманд, отличающееся тем, что, с целью повышения быстродействия и сокращения емкости памяти микропрограмм, устройство содержит второй блок формирования адреса микрокоманды, причем выход второго поля управления формирование адреса первого регистра микрокоманды соединен с входом кода инструкции второго блока формирования адреса микрокоманды, выход которого соединен с адресным входом второго блока памяти микропрограмм, первый вход синхронизации второго блока формирования адреса микрокоманды соединен с первым входом синхронизации устройства, второй вход синхронизации второго блока формирования адреса микрокоманды соединен с вторым входом синхронизации устройства,

25 3. Устройство поп.Д, о тл и - чающееся тем, что второй блок формирования адреса микрокоманды содержит регистр, счетчик, элемент И-НЕ, первый и второй элементы

формирования адреса микрокоманд содержит с первого по третий мультиплек-30 НЕ, причем старшие разряды входа соры, узел формирования адреса, триг- кода инструкции блока соединены с гер, узел ключей с тристабильным выходом, причем вход команд блока соединен с первыми информационными входами с первого по третий мультиплек- 35 соров, выходы которых соединены с информационными входами узла формирования адреса, информационный выход которого соединен с выходом блока, вторые информационные входы с первого 40 по третий мультиплексоров подключены к шинам логического нуля и логической единицы устройства, вход состояний блока соединен с управляющим входом условия логического перехода узла фор-д5 низации блока соединен с вторым мирования адреса, шина логической входом элемента И-НЕ, второй вход единицы устройства подключена к входу синхронизации блока соединен с тре- логического перехода узла формирова- тьим входом элемента И-НЕ и со счет- ния адреса, D-входу триггера и к млад- ным входом счетчика.

информационным входом регистра, выход которого соединен со старшими разрядами выхода блока, младший разряд входа кода инструкции блока соединен с входом первого элемента НЕ, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с входом синхронизации регистра и с входом второго элемента НЕ, выход которого соединен с входом установки в О счетчика, выход которого соединен с младшими разряда ми выхода блока, первый вход синхрошим разрядам информационного входа узла ключей с тристаоильным выходом, выходы которого соединены со старшими разрядами входа кода инструкций блока и с входом кода инструкции узла формирования адреса, младшие разряды входа кода инструкции блока подключены к информационным входам узла форми-

рования адреса, вход синхронизации блока соединен с входами синхронизации узла формирования адреса и триггера, прямой выход которого соединен с управляющим входом узла ключей с

тристабильным выходом, информационный вход старших разрядов которого соединен с потенциалом логического нуля устройства, инверсный выход триггера соединен с управляющими входами с

первого по третий мультиплексоров, выход признака режима работы узла формирования адреса соединен с входом управления третьим состоянием с первого по третий мультиплексоров.

НЕ, причем старшие разряды входа кода инструкции блока соединены с низации блока соединен с вторым входом элемента И-НЕ, второй вход синхронизации блока соединен с тре- тьим входом элемента И-НЕ и со счет- ным входом счетчика.

НЕ, причем старшие разряды входа кода инструкции блока соединены с низации блока соединен с вторым входом элемента И-НЕ, второй вход синхронизации блока соединен с тре- тьим входом элемента И-НЕ и со счет- ным входом счетчика.

информационным входом регистра, выход которого соединен со старшими разрядами выхода блока, младший разряд входа кода инструкции блока соединен с входом первого элемента НЕ, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с входом синхронизации регистра и с входом второго элемента НЕ, выход которого соединен с входом установки в О счетчика, выход которого соединен с младшими разрядами выхода блока, первый вход синхроВходкоманд

Вход

Вход кода инструкции .

Фиг.2

Выход

режиме

раб&пы

Адресные выходы

25

HDHf

§§ 1

§с 8|

5J

Фиг.з

Выход адреса

Фиг.Ч

f

--J

U-

en

-Л

to

с

gs

n

и Jk.

Л}

355

35

I

s

л -t

tr

Д

С

| Булгаков С.С, и др | |||

| Проектирование цифровых систем на комплектах микропрограммируемых БИС | |||

| - М.: Радио и связь, 1984, с, 185, рис.7.5 | |||

| Там же, с | |||

| Парный рычажный домкрат | 1919 |

|

SU209A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1991-01-07—Публикация

1988-06-09—Подача