сд

а

4

3150

Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контроллеров, исполь- зуемых в автоматизированных системах управления, обработки информации, связи.

Цель изобретения - повьшение достоверности контроля.

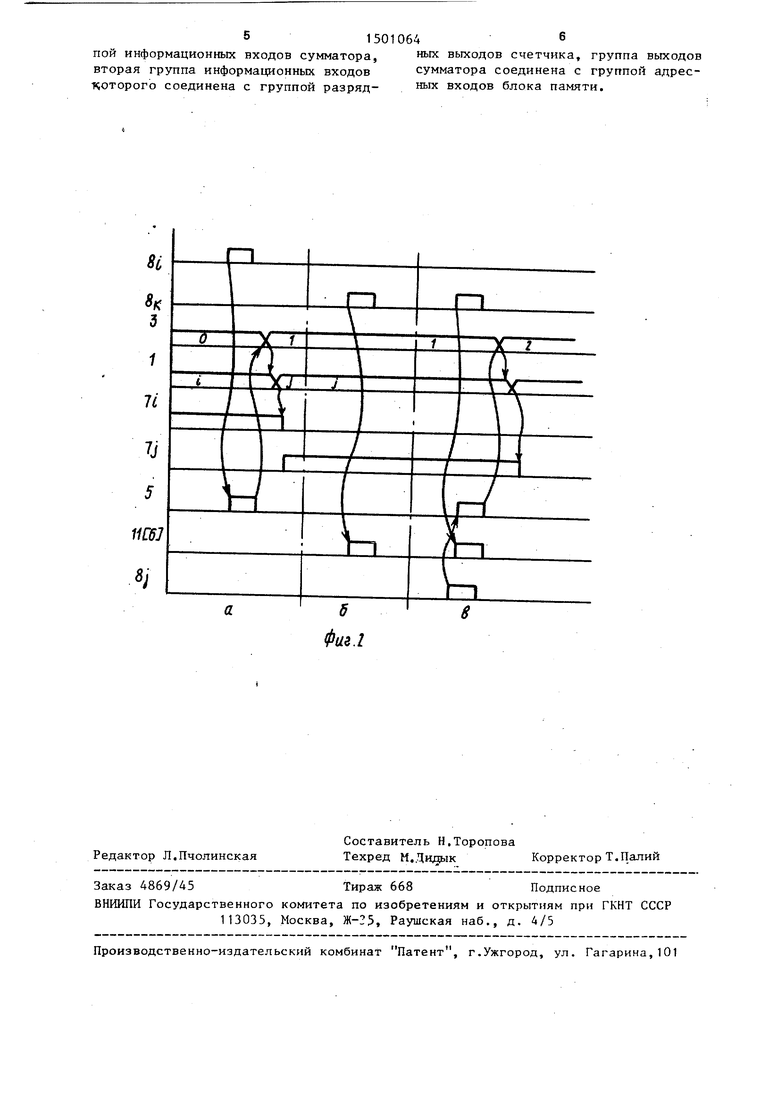

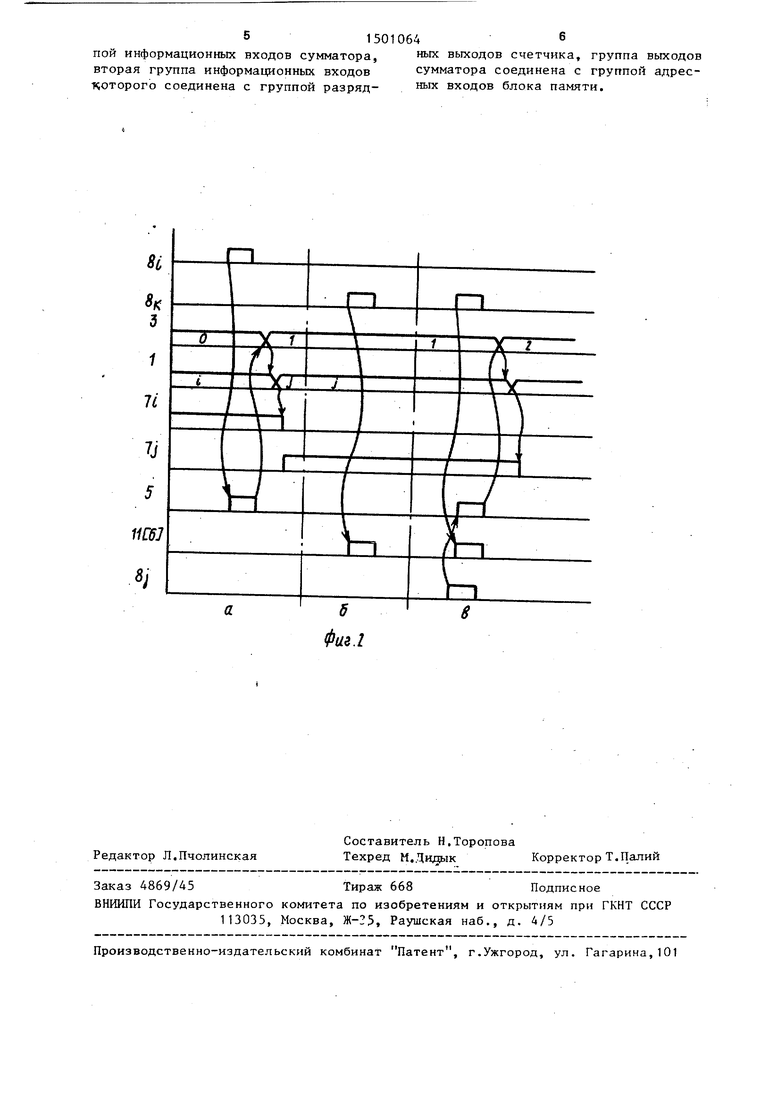

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временная диаграмма его работы.

Устройство содержит блок 1 памяти (ПЗУ), сумматор 2, счетчик 3, ре- гистр 4, первый 5 и второй 6 коммутаторы, дешифратор 7, входы 8 контролируемых последовательностей, группу 9 входов номера контролируемой последовательности, вход 10 разреше- ния записи и выход 11 ошибки.

Устройство работает следующим образом.

Перед началом функционирования элементы памяти устройства устанав- ливаются в О. В регистр 4 с группы 9 входов записывается адрес первой (ячейки, соответствующей контролируемой последовательности. Это осуществляется по входу 10 разрешения записи

По адресу, поступившему с выхода регистра 4, сумматор 2 формирует адрес ячейки памяти ПЗУ 1, из которой считывается код номера входа (например 8), который поступает на вход дешифратора 7. По этому коду дешифратор 7 формирует единичный сигнал на i-M выходе и нулевые сигналы - на остальных выходах. В результате i-й выходной сигнал дешифрато- ра 7 открьшает i-й информационный вход коммутатора 5 и закрывает i-й информационный вход коммутатора 6.

При поступлении импульса на вход 8; устройства (т,е, при правильной реализации контролируемой последовательности) последний через коммута-i тор 5 поступает на вход счетчика 3 и переводит его в единичное состояние, В результате этого на выходе сумма- тора 2 формируется адрес следующей ячейки памяти ПЗУ 1, и на вход дешифратора 7 поступает номер входа, по которому должен поступить очередной импульс (фиг, 2а) контролируемой последовательности (например-, вход

Если контролируемая последовательность искажена и очередной импульс

поступил на другой вход (например, вход 8), то этот импульс не проходит на выход коммутатора 5, Однако он проходит через коммутатор 6 на выход 11 устройства и формирует сигнал ошибки (фиг, 26),

Аналогично, если одновременно с импульсом по входу- 8j (соответствующим входной последовательности) поступает импульс на любой другой вход (например, 8), то этот импульс все равно проходит на выход коммутатора 6 и формирует на выходе 11 сигнал ошибки.

По окончании контролируемых последовательностей из ПЗУ 1 считывается ячейка, содержащая нулевой код. В результате на всех задействованных выходах дешифратора 7 имеется нулевой код и к.оммутатор 6 открыт по всем входам. Поэтому любой импульс, поступивший на входы 8, - 8 устройства, формирует сигнал ошибки на выходе 11 устройства.

Формула из.обретения

Устройство для контроля последовательностей импульсов, содержащее регистр, счетчик, блок памяти, дешифратор, первьй коммутатор, причем .информационные входы первого коммутатора являются входами контролируемых последовательностей устройства, выходы дешифратора соединены соответственно с управляющими входами первого коммутатора, выход которого соединен со счетным входом счетчика, вход разрешения записи регистра является входом устройства разрешения записи устройства, группа информационных входов регистра является группой входов номера контролируемой последовательности устройства, группа выходов блока памяти соединена с группой информационных входов дешифратора, отличающееся тем, что, с целью повьшгения достоверности контроля, в него введен сумматор и второй коммутатор, причем вход контролируемых последовательностей устройства соединены с информационными входами второго коммутатора, инверсные управляющие входы которого соединены с выходами дешифратора, выход первого коммутатора является выходом ошибки устройства, группа выходов регистра соединена с первой груп51501064

пой информационных входов сумматора. «ых вьпсодов счетчика, группа вьпсодов вторая группа информационных входов -которого соединена с группой разрядсумматора соединена с группой адресных входов блока памяти,

«ых вьпсодов счетчика, группа вьпсодов

сумматора соединена с группой адресных входов блока памяти,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Устройство для контроля двух последовательностей импульсов | 1988 |

|

SU1596336A1 |

| Устройство для контроля последовательностей импульсов | 1990 |

|

SU1725373A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1316053A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1649548A1 |

Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контролеров, используемых в автоматизированных системах управления, обработки информации, связи. Целью изобретения является повышение достоверности контроля. Отличительной особенностью устройства является то, что оно позволяет формировать сигнал ошибки в случае пропуска любого импульса в контролируемых последовательностях, а также при поступлении ложного импульса по любому из входов одновременно с импульсом, соответствующим контролируемой последовательности, что повышает достоверность контроля. Введение сумматора 2 и его связей позволяет формировать адрес очередного контрольного кода в блоке памяти. При этом разрядность этого адреса будет равна минимально возможной. 2 ил.

8L

11C6J

| Устройство для контроля многоканальных импульсных последовательностей | 1982 |

|

SU1042171A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля последовательностей импульсов | 1987 |

|

SU1444777A1 |

Авторы

Даты

1989-08-15—Публикация

1987-08-04—Подача