Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контроллеров, датчиков информации, используемых в автоматизированных системах управления, обработки информации, связи.

Цель изобретения - повышение достоверности контроля путем обеспечения контроля последовательностей импульсов с одинаковым периодом по разным входам.

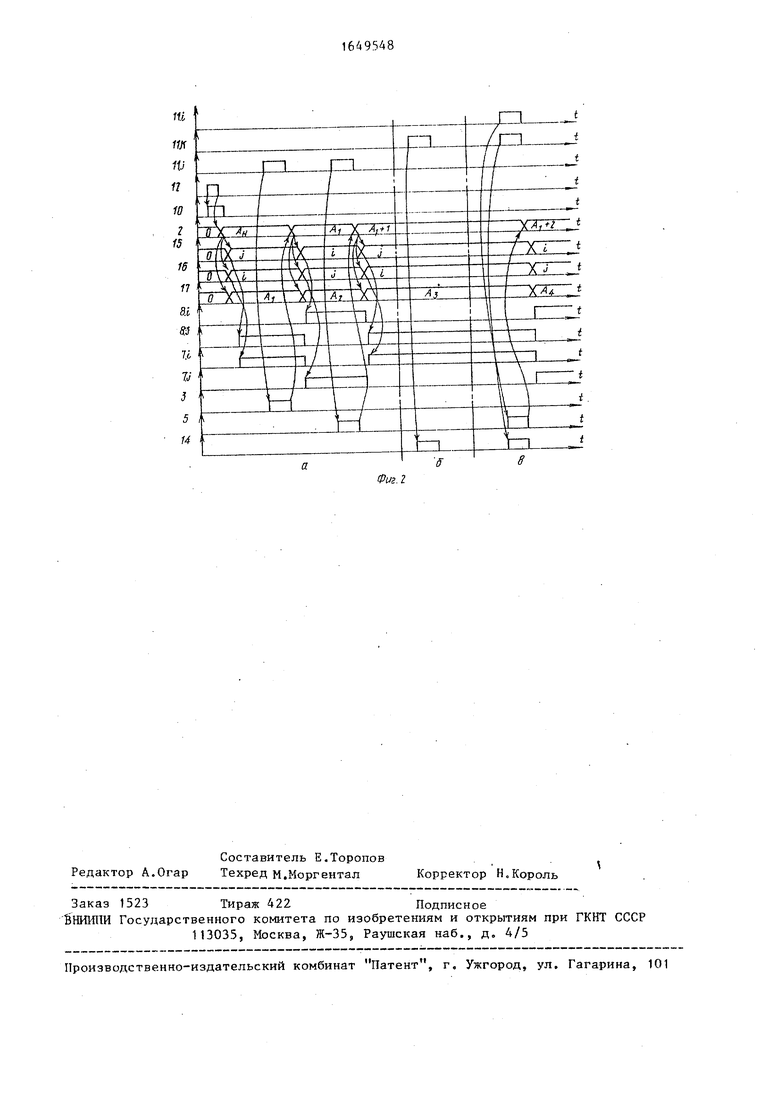

На фиг.1 приведена функциональная схема устройства; на фиг.2 - временные диаграммы его работы.

Устройство содержит блок 1 памяти, счетчик 2, с первого по четвертый коммутаторы 3-6, первый 7 и второй 8 дешифраторы, элемент ИЛИ 9, одно- вибратор 10, входы 11 контролируемых последовательностей, вход 12 запуска, группу 13 входов номера последовательности, выход 14 ошибки устройства, а также первую 15,вторую 16 и третью 17 группы выходов блока 1 памяти.

Устройство работает следующим образом.

Перед началом работы элементы памяти устройства устанавливаются в 6. Цепи начальной установки на фиг.1 условно не показаны.

Импульс, поступивший на вход 12 устройства, проходит на вход одно- вибратора 10. Последний формирует на своем выходе импульс, который открывает первую группу информационных входов коммутатора 6, и на информационные входы счетчика 2 коммутируется поступивший на вход 13 ., устройства код номера последователь ности. Одновременно импульс, поступивший на вход 12 устройства, через элемент ИЛИ 9 поступает на БХОД разрешения записи счетчика 2, и по его заднему фронту в счетчик 2 записывается код номера последовательности - адрес первой ячейки программы, соответствующей контролируемой последовательности.

Адрес из счетчика 2 поступает на входы блока 1 памяти, и из него с

выходов 15 и 16 считываются коды номеров входов (например, 11.} и 11.1 соответственно), которые поступают на входы дешифраторов 7 и 8, ас выхода группы 17 - адрес очередной ячейки блока 1. По поступившим на вход кодам дешифраторы 7 и 8 формируют единичный сигнал соответствен- ® но на j-м и i-м входах и нулевые на остальных. В результате j-й выходной сигнал дешифратора 7 открывает j-й информационный вход коммутатора 3 и закрывает j-й информационный вход коммутатора 4. Аналогично i-й сигнал дешифратора 8 открывает i-й информационный вход коммутатора 5 и закрывает i-й информационный вход коммутатора 4.

30 При поступлении импульса на вход 11.J устройства (т.е. при правильной реализации контролируемой последовательности) он через коммутатор 3 и элемент ИЛИ 9 проходит на вход раз- 35 решения записи счетчика 2, По этому импульсу в счетчик 2 записывается скоммутированный на его информационные входы (так как управляющий сигнал на коммутатор 6 нулевой) адрес AJ, № считанный с выхода группы 17 блока 1 памяти. Адрес со счетчика 2 поступает на вход блока 1 памяти, и он формирует на своих выходах 15 и 16 коды номеров входов (например, 11.1 и 11.J соответственно), а на выходе 17 - адрес Аг..

При поступлении импульса на вход 11.1 устройства (в соответствии с контролируемой последовательностью) 50 он проходит через коммутатор 5 на счетньй вход счетчика 2, Последний формирует новый адрес А + 1, в соответствии с которым из блока 1 считается новая информация: с выходов 15 ;5 и 16 - коды номеров входов (пусть 11.J и 11,1 соответственно), а с выхода 17 - адрес А9 (фиг.2а).

Таким образом, если импульс поступает по входу, код номера которо

51

го считывался с выхода 16 бпока 1 памяти, то в качестве очередной адреса испопьзуется адрес, считанный с выхода 17 блока 1 памяти, а если импульс поступает но входу, код которого считывался с выхода 16 блока 1 памяти, то очередной адрес Формируется путем увеличения предыдущего на единицу. Это позволяет обес- печить достоверность контроля при ветвлении контролируемой последовательности. Если контролируемая последовательность искажена и очередной импульс поступил на другой вход (на- пример, 11.К), то этот импульс не проходит на выходы коммутаторов 3 и 5. Однако он проходит через коммутатор 4 и формирует на выходе 14 устройства сигнал ошибки (фиг.26).

Аналогично если одновременно с импульсом, соответствующим входной последовательности (например, 11.1), поступает импульс, не соответствующий входной последовательности (на- пример, на вход 11.К), то этот импульс все равно проходит на выход коммутатора 4 и формирует на выходе 14 сигнал ошибки.

По окончании контролируемой по- следовательности из блока 1 памяти считывается ячейка, содержащая нулевые коды. В результате на всех задействованных выходах дешифраторов 7 и 8 будут нулевые сигналы и коммутатор 4 будет открыт по всем входам. Поэтому любой импульс, поступивший на входы 11,1 - 11,п устройства, сформирует сигнал ошибки на выходе 14 устройства.

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее блок памяти, счетчик, первый и второ коммутаторы и первый дешифратор, причем информационные входы первого и второго коммутаторов соединены соответственно между собой и являются входами контролируемых последовательностей устройства, первая группа

Q «, 0

5

0 Q

t

5

рыхшшч номера контролируемой последовательности блока памяти соединена с группой информационных входов первого дешифратора, группа выходов которого соединена с группой управляю- пшх входов первого коммутатора и первой группой инверсных управляющих входов второго коммутатора, выход которого является выходом ошибки уст. ройства, отличающееся тем, что, с целью повышения достоверности контроля путем контроля последовательностей импульсов с одинаковым периодом по разным входам, в него введены третий и четвертый коммутаторы, второй дешифратор, элемент ИЛИ и одновибратор, причем информационные входы третьего коммутатора соединены соответственно с информационными входами первого коммутатора, выход третьего коммутатора соединен со счетным входом счетчика, вторая группа выходов номера контролируемой последовательности блока памяти соединена с группой информационных входов второго дешифратора, группа выходов которого соединена с группой управляющих входов третьего коммутатора и второй группой инверсных управляющих входов второго коммутатора, выход первого коммутатора соединен с первым входом элемента ИЛИ, выход которого соединен с входом разрешения записи счетчика, разрядные выходы которого соединены соответственно с адресными входами блоха памяти, вход запуска устройства соединен с вторым входом элемента ИЛИ и входом одновиб- ратора, выход которого соединен с прямым и инверсным управляющими входами четвертого коммутатора, первая группа информационных входов которого является входами номера контролируемой последовательности устройства, третья группа выходов номера контролируемой последовательности блока памяти соединена с второй группой информационных входов четвертого коммутатора, группа выходов которого соединена с группой информационных входов счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1619277A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство для контроля последовательностей импульсов | 1990 |

|

SU1725373A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

| Устройство для контроля последовательностей импульсов | 1987 |

|

SU1501064A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1667080A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для контроля сложных блоков синхронизации, контроллеров, датчиков информации. Отличительной особенностью устройства является то, что оно позволяет проверять последовательности с одновременным присутствием импульсов по разным каналам. Целью изобретения является повышение досто

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1252930A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР по заявке № 4294348/24, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-15—Публикация

1989-05-23—Подача