Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем высокой производительности.

Цель изобретения - повышение быстродействия.

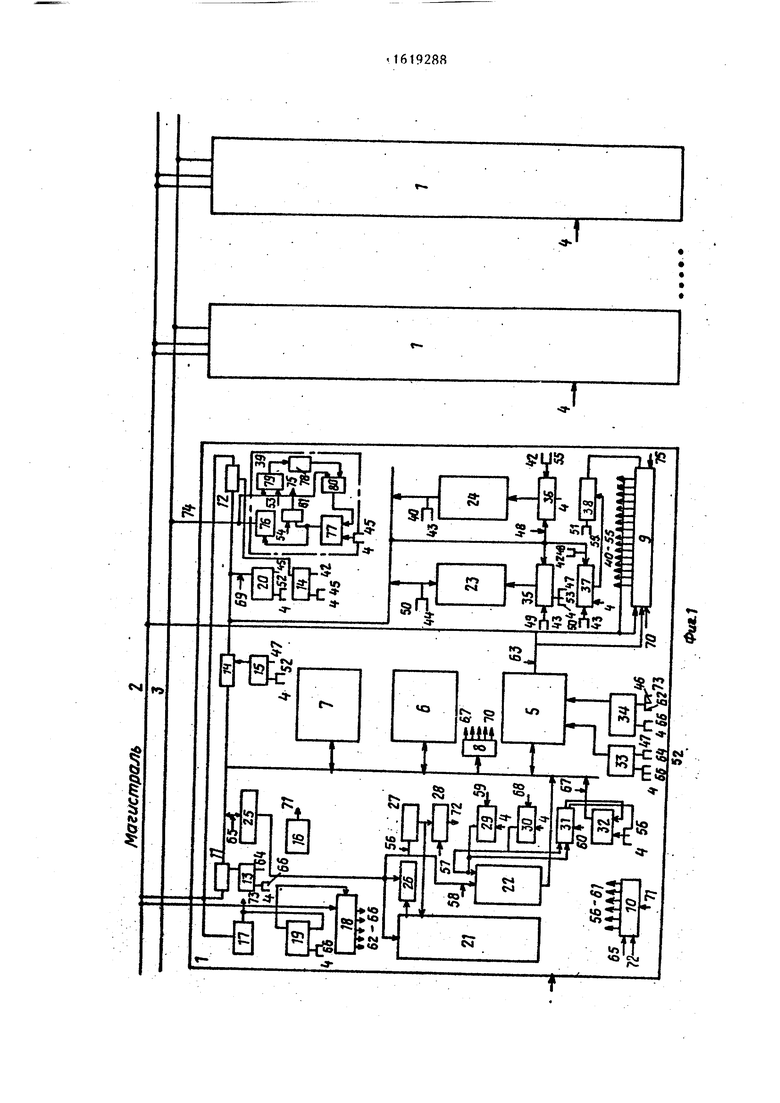

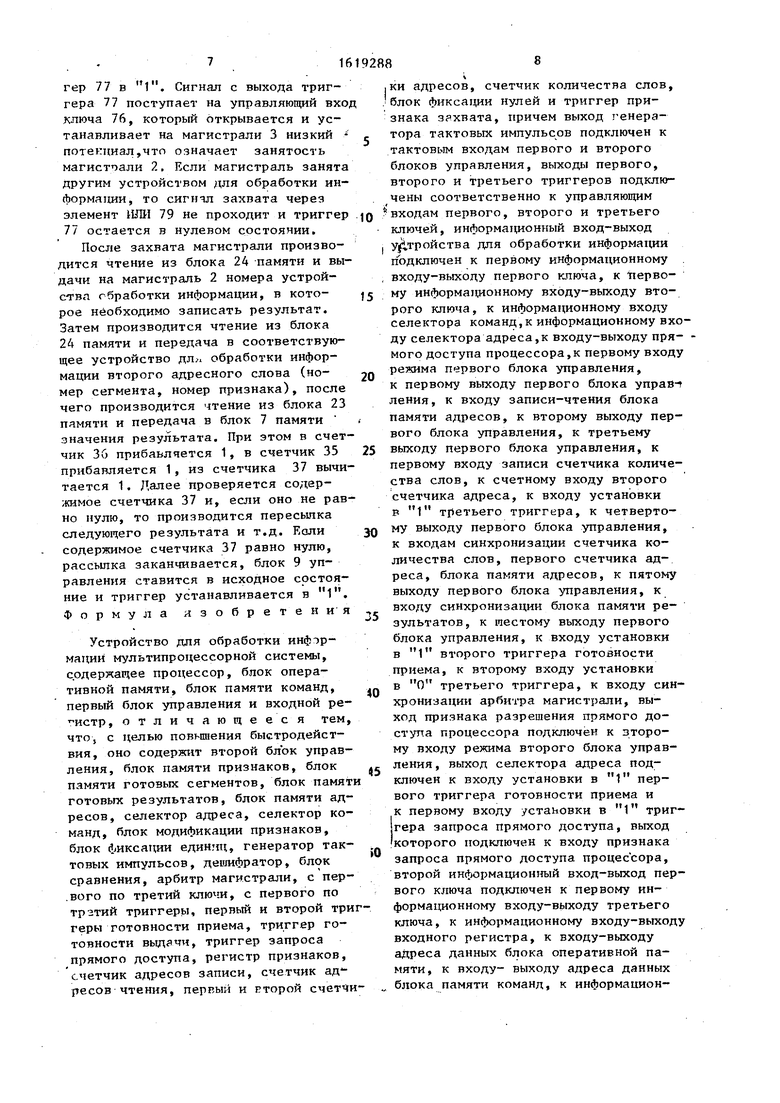

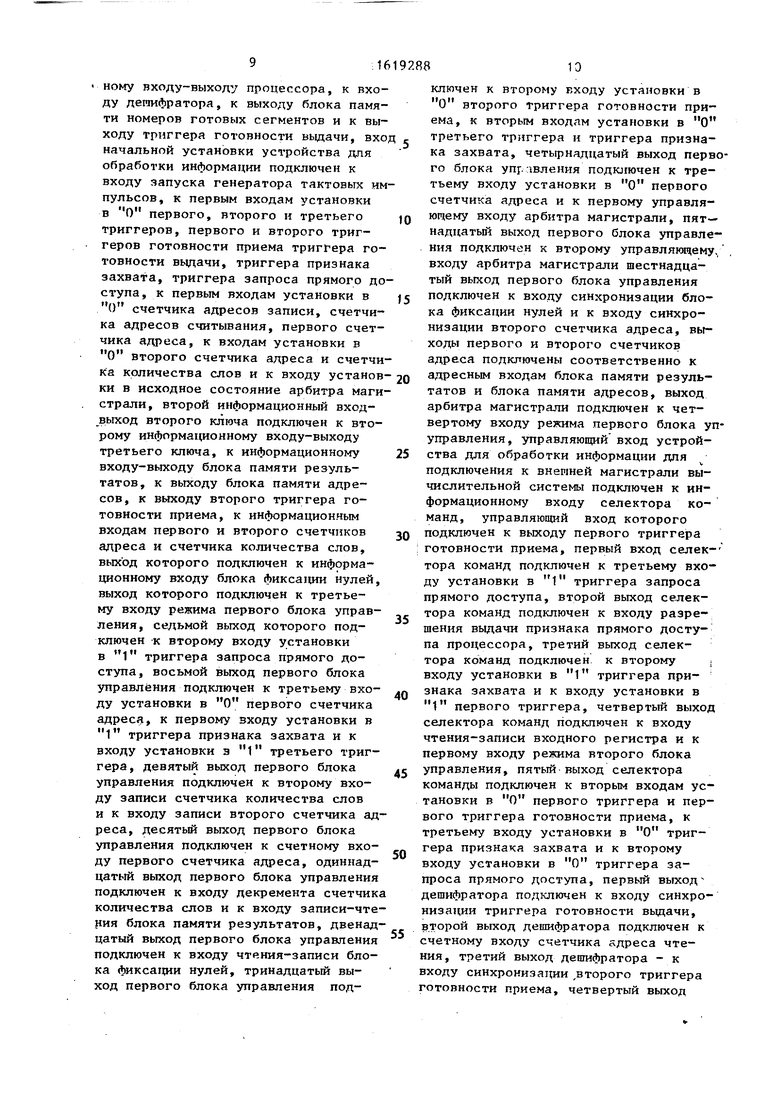

На фиг.1 представлена схема устройства для обработки информации и его внешнее подключение; на фиг.2 - схема блоков управления.

Вычислительная система содержит устройства 1 для обработки информации, внешнюю магистраль 2 вычислительной системы, вход-выход признака занятости магистрали 3 устройства

для обработки информации, вход 4 начальной установки устройства для обработки информации, процессор 5, блок 6 памяти команд, блок 7 оперативной памяти, дешифратор 8, первый 9 и второй 10 блоки управления, ключи 11 и 12, с первого 13 по третий 15 триггеры, генератор 16 тактовых импульсов, селектор 17 адреса, селектор 18 команд, первый 19 и второй 20 триггеры готовности приема, блок 21 памяти признаков, блок 22 памяти номеров готовых сегментов, блок 23 памяти результатов, блок 24 памяти адресов, входной регистр 25, блок 26 модифиODСО

to

00 00

кяции признаков, регистр 27 признаков, блок 28 фиксации единиц, счетчик 29 адресов записи, счетчик 30 адресов считывания, блок 31 сравнения, триггер 32 готовности выдачи, триггер 33 признака захвата, триггер 34 запроса прямого доступа, первый 35 ,и второй 36 счетчики адреса, счетчик 37 количества слов, блок 38 фиксации ну. ей, арбитр 39 магистрали, с пер- вого 40 по шестнадцатый 55 выходы блока 9 управления, с первого 56 по шестой 61 выходы блока 10 управления, с первого 62 по пятый 66 выходы селектора 18 команд, с первого 67 по четвертый 70 выходы дешифратора 8, выход 71 генератора 16 тактовых импульсов, выход 2 блока 28 фиксации единиц, выход 73 селектора 17 адреса, информационный вход-выход 74 арбитра 39 магистрали, выход 75 арбитра 39 магистрали. Арбитр 39 магистрали содержит ключ 76, триггер 77 запроса магистрали, элемент 78 задержки и с первого 79 по третий 81 элементы ИЛИ.

Первый 9 и второй 10 блоки управления содержат триггеры 82, элемен- ты 83 задержки и формирователи .84 сигналов управления.

Вся программа решения задачи разбивается на независимые участки (сегменты) , которые могут быть выполнены параллельно. Группы сегментов заносятся в блок 6 памяти команд (ПК) и запуск сегмента на исполнение производится по готовности аргументов сегмента. Исполнение сегмента производится процессором 5 по программе сегмента под управлением потока команд (по счетчику команд). Блок 21 памяти признаков (ППР) содержит линейки признаков, соответствующие каждому сегменту данного устройства для обработки информации Количество признаков соответствует копичеству информационных и логических аргументов сегмента. Если аргумент готов, то соответствующему признаку присваивается значение 1, если не готов - 0. Когда готовы все аргументы сегмента, то в линейке признаков сегмента устанавливаются все единицы, что является сдвиде- тельством того, что данный сегмент готов к исполнению. Отмека признаков и проверка единиц в пинейках

признаков производится при поступлении каждого аргумента.,

Аргумент от одного устройства для

обработки информации к другому передается с помощью двух слоев: адресного и значащего. Адресное слово содержит номер устройства для обработки информации, номер сегмента,

которому предназначен аргумент, номер признака, который присвоен данному аргументу в линейке признака, и количество признаков данного сегмента.

5 Адресное слово состоит из двух слов (для случая, например, 16-разрядного процессора 5):

первая часть адресного слова

20

15

I № устройства

J

вторая часть адресного слова

25

15

65

32

0

5

Значащее слово содержит собственно значение аргумента.

При появлении на магистрали 2 первой части адресного слова в определенном устройстве для обработки информации срабатывает селектор 1 7 адреса, который выдает сигнал на установку триггера 19 (ТгГП1) и триггера 34, что подготовит адресуемое

0 устройство для обработки информации к последующему приему второй части адресного слова и значащего слова . Рторая часть адресного слова поступает на входной регистр 25 (РгВх)

ц и служит адресом для записи в блок 7 значащего слова, а также адресом отмечаемой линейки признаков. При этом запускается блок 10 управления, осуществляющий управление, отметку признаков и определение готовых сегментов.

В первом такте работы блока 10 управления производится выборка из блока 21 памяти признаков сегмента по адресу, содержащемуся в разрядах

15-6 регистра 25. Выбранный код логдр- чески суммируется с, кодом,выбранным блоком 26 модификации, на вход которого поступает код разрядов с пятого

по нулевой входного регистра 25 и записывается в регистр 27 признаков. При этом в разряд регистра 77, который соответствует номеру признаков, записывается t (порядок номеров возрастает справа налево) и, кроме того, единицы записываются в такое количество крайних слева разрядов, какое соответствует числу неиспольэо- ванных признаков (свободных мест), равному разнице между максимально воможным и числом используемых в сегменте признаков, указанных в разрядах с второго по нулевой входного ре гистра 25.

Лалее производится опрос блока 28 фиксации единиц. Ксли в слове, записанном в регистр 27, окажутся все единицы, то производится запись но- мера сегмента, содержащегося в разрядах с пятнадцатого по шестой входного регистра 25 в блок 22 памяти готовых сегментов по адресу, содержащемуся в счетчике 29, а в блоке 21 памя- ти на место выбранного слова признаков записывается 0, если в регистре 27 признаков не все единицы, то запись в блок 22 памяти не производится, а в блок 21 памяти на место выб- ранного слова признаков записывается модифицированное слово. Управление блоком 22 памяти производится с помощью счетчиков 29 и 30. В начале работы при поступлении сигнала на вход 4 оба счетчика устанавливаются

О

После записи первого кода

готового сегмента (КГС) в счетчик 29 адресов записи прибавляется единица. Чтение блока 22 памяти производится по запросу процессором 5. Сначала опрашивается триггер 32 готовности выдачи, определяющий наличие информации (кодов готовых сегментов) в блоке 22 памяти. Триггер 32 устанавливается в 1, если содержимое счетчика 29 и счетчика 30 не равно (т.е., когда в блоке 22 имеется информация). При этом чтение КГС из блока 22 памяти производится по адресу, определяемому счетчиком 30. После чтения КГС в счетчик 30 добавляется 1.

Исходными данными для рассылки являются результаты работы сегмента, записанные в блок 7 памяти, файл адресов рассыпки (Р), записанный в области памяти адресов рассылки (ПАР и информационное слово (ИС), сопровождающее каждый сегмент программы и содержащее информацию о начальном адресе в ПАР и количестве рассылочных результатов. Формат информацион-) ного слова имеет вид:

15 11 10О

Распределение памяти адресов ПАР может иметь вид:

сегм. № 1

1-е адр. слово рез.1

сегм. N 2

2-е адр. слово .1

| айлы адресов результатов заносят|ся в ПАР при программировании.

i Массив результатов и информационное слово формируются в блоке 7 памяти процессором 5 в процессе реализации сегментов программы.

По окончании выполнения сегмента программы процессор 5 запрашивает готовность к приему информации и при ее наличии запускает блок 9 управле, нця, который управляет рассылкой.

Сначала осуществляется пересылка из блока 7 памяти в блок 23 памяти массива значений результатов сегмента, в счетчик 36 адреса начала ФР, в счетчик 37 - кода количества рас- сылок. Рассылка прекращается, когда в счетчике 37 будет нуль, что фиксируется блоком 38.

Далее осуществляется рассылка результатов по адресам согласно файлу рассылки (йр). Сначала производится захват магистрали 2 через арбитр 39 магистрали. Для этого через первый управляюпий вход арбитра 39 подается сигнал на первый вход элемента ИЛИ 79, второй вход которого связан с информационным входом-выходом 74 занятости магистрали 2. Если на входе-выходе 74 высокий потенциал (Магистраль свободна), то сигнал проходит через элемента ИЛИ 79, задержки 78, ИЛИ 80 и устанавливает тригrep 77 в 1. Сигнал с выхода триггера 77 поступает на управляющий вхо ключа 76, который открывается и устанавливает на магистрали 3 низкий потенциал,что означает занятость магистрали 2. Если магистраль занята другим устройством для обработки информации, то сигнтл захвата через элемент ИЛИ 79 не проходит и триггер 77 остается в нулевом состоянии.

После захвата магистрали производится чтение из блока 24 памяти и выдачи на магистраль 2 номера устройства обработки информации, в кото- рое необходимо записать результат. Затем производится чтение из блока 24 памяти и передача в соответствующее устройство длл обработки информации второго адресного слова (номер сегмента, номер признака), после чего производится чтение из блока 23 памяти и передача в блок 7 памяти значения результата. При этом в счетчик 36 прибавляется 1, в счетчик 35 прибавляется 1, из счетчика 37 вычитается 1. Далее проверяется содержимое счетчика 37 и, если оно не равно нулю, то производится пересылка следующего результата и т.д. Коли содержимое счетчика 37 равно нулю, рассыпка заканчивается, блок 9 управления ставится в исходное состояние и триггер устанавливается в 1. Формула изобретения

Устройство для обработки информации мультипроцессорной системы, содержащее процессор, блок оперативной памяти, блок памяти команд, первый блок управления и входной ре- истр, отличающееся тем, что, с целью повышения быстродействия, оно содержит второй блок управления, блок памяти признаков, блок памяти готовых сегментов, блок памят готовых результатов, блок памяти адресов, селектор адреса, селектор команд, блок модификации признаков, блок фиксации единиц, генератор тактовых импульсов, дешифратор, блок сравнения, арбитр магистрали, с пер- .вого по третий ключи, с первого по тр-дтий триггеры, первый и второй тригеры готовности приема, триггер готовности выдачи, триггер запроса прямого доступа, регистр признаков, счетчик адресов записи, счетчик адресов чтения, первый и нторой счетчи.

5 0

0

5

5

0

5

,ки адресов, счетчик количества слов, блок фиксации нулей и триггер признака зяхвата, причем выход генератора тактовых импульсов подключен к тактовым входам первого и второго блоков управления, выходы первого, второго и третьего триггеров подключены соответственно к управляющим входам первого, второго и третьего ключей, информационный вход-выход

. устройства для обработки информации подключен к первому информационному

, входу-выходу первого ключа, к первому информационному входу-выходу второго ключа, к информационному входу селектора команд,к информационному входу селектора адреса,к входу-выходу пря- - мого доступа процессора,к первому входу режима первого блока управления, к первому выходу первого блока управ-t ления, к входу записи-чтения блока памяти адресов, к второму выходу первого блока управления, к третьему выходу первого блока управления, к первому входу записи счетчика количества слов, к счетному входу второго счетчика адреса, к входу установки в 1 третьего триггера, к четвертому выходу первого блока управления, к входам синхронизации счетчика количества слов, первого счетчика адреса, блока памяти адресов, к пятому выходу первого блока управления, к входу синхронизации блока памяти результатов , к шестому выходу первого блока управления, к входу установки в 1 второго триггера готовности приема, к второму входу установки в О третьего триггера, к входу синхронизации арбитра магистрали, выход признака разрешения прямого доступа процессора подключен к второму входу режима второго блока управления , выход селектора адреса подключен к входу установки в 1 первого триггера готовности приема и к первому входу установки в 1 триггера запроса прямого доступа, выход которого подключен к входу признака запроса прямого доступа процессора, второй информационный вход-выход первого ключа подключен к первому информационному входу-выходу третьего ключа, к информационному входу-выходу входного регистра, к входу-выходу адреса данных блока оперативной памяти, к входу- выходу адреса данных блока памяти команд, к информациейному входу-выходу процессора, к входу дешифратора, к выходу блока памяти номеров готовых сегментов и к выходу триггера готовности выдачи, вхо начальной установки устройства для обработки информации подключен к входу запуска генератора тактовых импульсов, к первым входам установки в О первого, второго и третьего триггеров, первого и второго триггеров готовности приема триггера готовности выдачи, триггера признака захвата, триггера запроса прямого доступа, к первым входам установки в О счетчика адресов записи, счетчика адресов считывания, первого счетчика адреса, к входам установки в О второго счетчика адреса и счетчика количества слов и к входу установ- ки в исходное состояние арбитра магистрали, второй информационный вход- выход второго ключа подключен к второму информационному входу-выходу третьего ключа, к информационному входу-выходу блока памяти результатов, к выходу блока памяти адресов, к выходу второго триггера готовности приема, к информационным входам первого и второго счетчиков адреса и счетчика количества слов, выход которого подключен к информационному входу блока фиксации нулей, выход которого подключен к третьему входу режима первого блока управления, седьмой выход которого подключен к второму входу установки в 1 триггера запроса прямого доступа, восьмой выход первого блока управления подключен к третьему вхо- ду установки в О первого счетчика адреса, к первому входу установки в 1 триггера признака захвата и к входу установки э 1 третьего триггера , девятый выход первого блока управления подключен к второму входу записи счетчика количества слов и к входу записи второго счетчика адреса, десятый выход первого блока управления подключен к счетному входу первого счетчика адреса, одиннадцатый выход первого блока управления подключен к входу декремента счетчика количества слов и к входу записи-чтения блока памяти результатов, двенадцатый выход первого блока управления подключен к входу чтения-записи блока фиксации нулей, тринадцатый выход первого блока управления под

JQ 5 0 5 JQ 0

5

5

0

5

ключей к второму входу установки в О второго триггера готовности приема, к вторым входам установки в О третьего триггера и триггера признака захвата, четырнадцатый выход первого блока упг тления подключен к третьему входу установки в О первого счетчика адреса и к первому управля- кщему входу арбитра магистрали, пятнадцатый выход первого блока управления подключен к второму управляющему, входу арбитра магистрали шестнадцатый выход первого блока управления подключен к входу синхронизации блока фиксации нулей и к входу синхронизации второго счетчика адреса, выходы первого и второго счетчиков адреса подключены соответственно к адресным входам блока памяти результатов и блока памяти адресов, выход арбитра магистрали подключен к четвертому входу режима первого блока уп- управления, управляющий вход устройства для обработки информации для подключения к внешней магистрали вычислительной системы подключен к информационному входу селектора команд, управляющий вход которого подключен к выходу первого триггера готовности приема, первый вход селек- тора команд подключен к третьему входу установки в 1 триггера запроса прямого доступа, второй выход селектора команд подключен к входу разрешения выдачи признака прямого доступа процессора, третий выход селектора команд подключен к второму , входу установки в 1 триггера признака захвата и к входу установки в 1 первого триггера, четвертый выход селектора команд подключен к входу чтения-записи входного регистра и к первому входу режима второго блока управления, пятый выход селектора команды подключен к вторым входам установки в О первого триггера и первого триггера готовности приема, к третьему входу установки в О триггера признака захвата и к второму входу установки в О триггера запроса прямого доступа, первый выходх дешифратора подключен к входу синхронизации триггера готовности выдачи, второй выход дешифратора подключен к счетному входу счетчика адреса чтения, третий выход дешифратора - к входу синхронизации ,второго триггера готовности приема, четвертый выход

дешифратора - к пятому входу режима первого блока управления, выход входного регистра подключен к адресному входу блока памяти признаков, к первому информационному входу блока модификации признаков и к информационному входу блока памяти номеров готовых сегментов,выход блока памяти признаков подключен к второму информационному входу блока модификации, выход которого подключен к информационному входу регистра признаков, выход которого подключен к информационным входам блока памяти признаков и блока фиксации единиц, выход которого подключен к второму входу режима второго блока управления, первый выход которого подключен к второму входу установки в О триггера готовности выдачи и к входу записи-считывания регистра признаков, второй выход второго блока управления подключен к управляющему входу блока фиксации единиц, третий выход второго блока управления подключен к входу записи- чтения блока памяти номера готовых сегментов и-к входу записи блока памяти признаков, четв ертый выход второго блока управления подключен к счетному входу счетчика адресов записи, пятый выход второго блока уп равления подключен к входу синхронизации блока сравнения, прямой и ин- ,версный выходы которого подключены

0

5

0

5

соответственно к входу установки в м и к третьему входу установки в

Г

О триггера готовности выдачи, шестой выход второго блока управления подключен к входу чтения блока памяти признаков, выход триггера признака захвата подключен к входу признака захвата процессора, вход-выход признака занятости магистрали устройства для обработки информации подключен к информационному входу-выходу арбитра магистрали, выход счетчика адресов записи подключен к первому информационному входу блока сравнения и к первому адресному входу блока памяти номеров готовых сегментов .выход счетчика адресов чтения подключен к второму информационному входу |блока сравнения и к второму адресному входу блока памяти номеров готовых сегментов.

Магистраль

56-61 Hz

65 Jiiiii trb

Я w rrC3

72-1-ЈLJц S6

ет за ш

&Г1 55 .rffi Л.UH

g 52

ш L

TT 70 H « SB W

от-51

Л tttmrnttTttft

g «55 52

Ј

Фи«.;

и

Со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

| Многопроцессорная система | 1989 |

|

SU1686455A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Периферийный процессор для обработки сигналов | 1985 |

|

SU1368889A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Многопроцессорная вычислительная система | 1988 |

|

SU1569843A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем высокой производительности. Цель изобретения - повышение быстродействия. Поставленная цель достига- ется тем, что устройство для обработки информации содержит процессор, блок памяти команд, блок оперативной памяти, дешифратор, два блока управления, три ключа, три триггера, ге- , нератор тактовых импульсов, селектор адреса, селектор команд, два триггера готовности приема, блок памяти признаков, блок памяти номеров готовых сегментов, блок памяти результатов, блок памяти адресов, входной регистр, блок модификации, регистр признаков, блок фиксации единиц, счетчик адресов записи, счетчик адресов считывания, блок сравнения, триггер готовности выдачи, триггер признака захвата, триггер запроса прямого доступа, два счетчика адреса, счетчик количества слов, блок фиксации нулей и арбитр магистрали, 2 ил. I

«SI

«о

ос

т

Csl

I

ь

00

I

л

51

4

| EEETrans on Computers, 1983, v.32, № 5, p.32 | |||

| Хвощ С.Т., Вардинский Н.Н | |||

| и Попов Е.А | |||

| Микропроцессоры и мик- ,роЭВМ в системах автоматического управления | |||

| Справочник | |||

| Л.: Машиностро-; ение | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1991-01-07—Публикация

1989-03-22—Подача