входами сброса блока управления, выход запуска кочюрого соединен с вторым информационным входом первох-о коммутатора, управляющий вход которого соединен с выходом старшего разряда двоичного счетчика, с входом переноса сумматора и с управляющим входом второго коммутафора, информационный вход которого соединен с выходом счетчика коррекции, а первый и второй выходы второго коммутатора соединены соответственно с входами сложения и вычитания двоично-десятичного счетчика, информационный вход которого соединен с выходом блока памяти, входы младших разрядов и вход старшего разряда которого соединены.соответственно с выходами суммы и выходом переноса сумматора, первая группа входов которого соединена с информационными входами старших разрядов преобразователя/ вход логического нуля которого соединен . с второй группой входов сумматора.

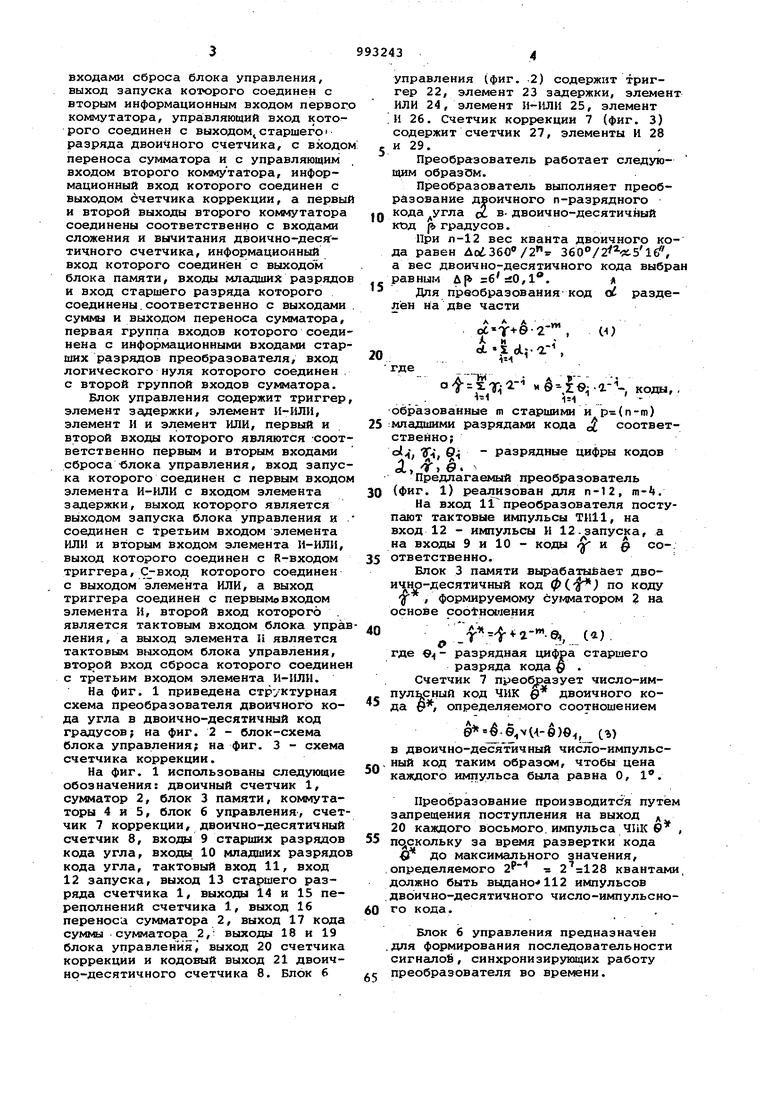

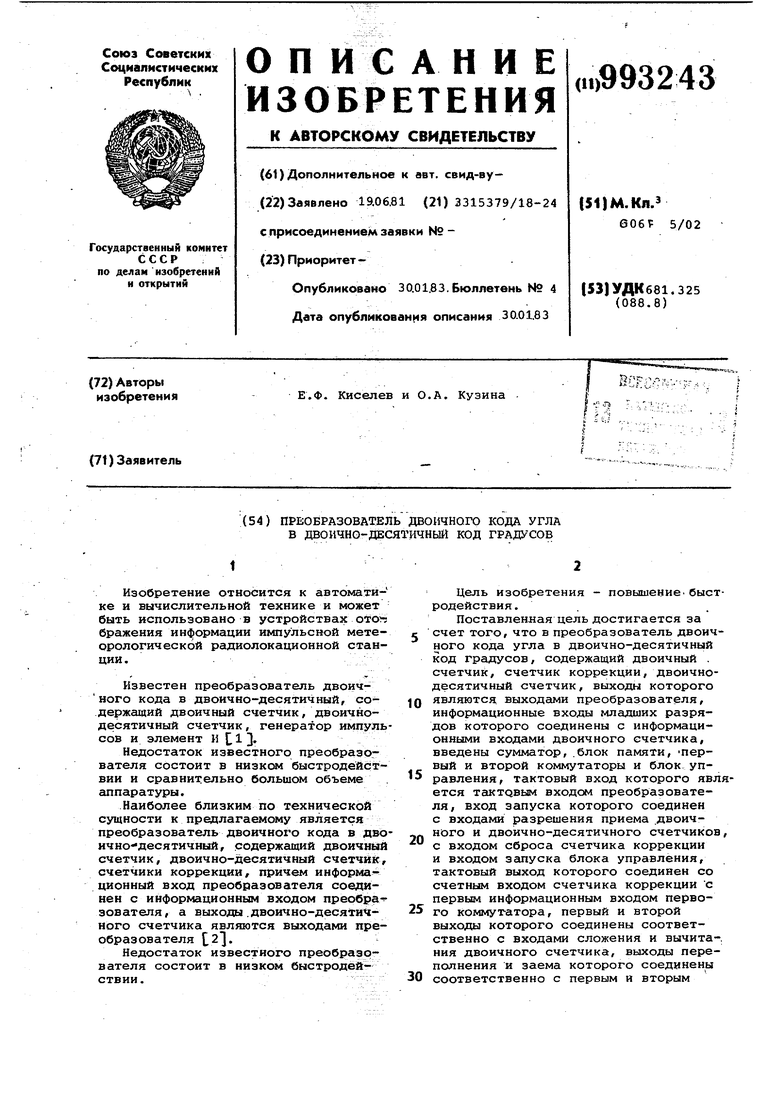

Блок управления содержит триггер элемент задержки, элемент Н-ИЛИ, элемент И и элемент ИЛИ, первый и второй входы которого являются -соответственно первым и вторым входами сброса -блока управления, вход запуска которого соединен с первым входом элемента И-ИЛИ с входом элемента задержки, выход которого является выходом запуска блока управления и соединен с третьим входом элемента ИЛИ и вторым входом элемента И-ИЛИ, выход которого соединен с R-входом триггера, С -вход которого соединен с выходом элемента ИЛИ, а выход триггера соединен с первымовходом элемента И, второй вход которого является тактовым входом блока управления, а выход элемента И является тактовым выходом блока управления, второй вход сброса которого соединен с третьим входом элемента И-ИЛИ.

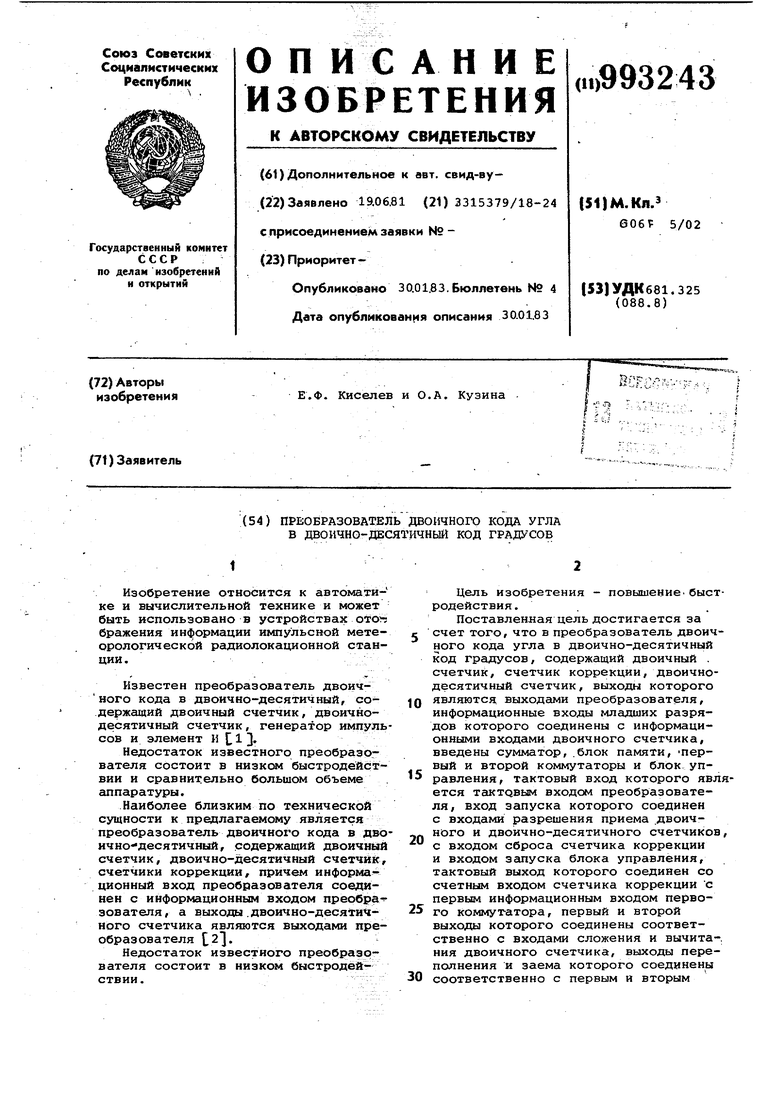

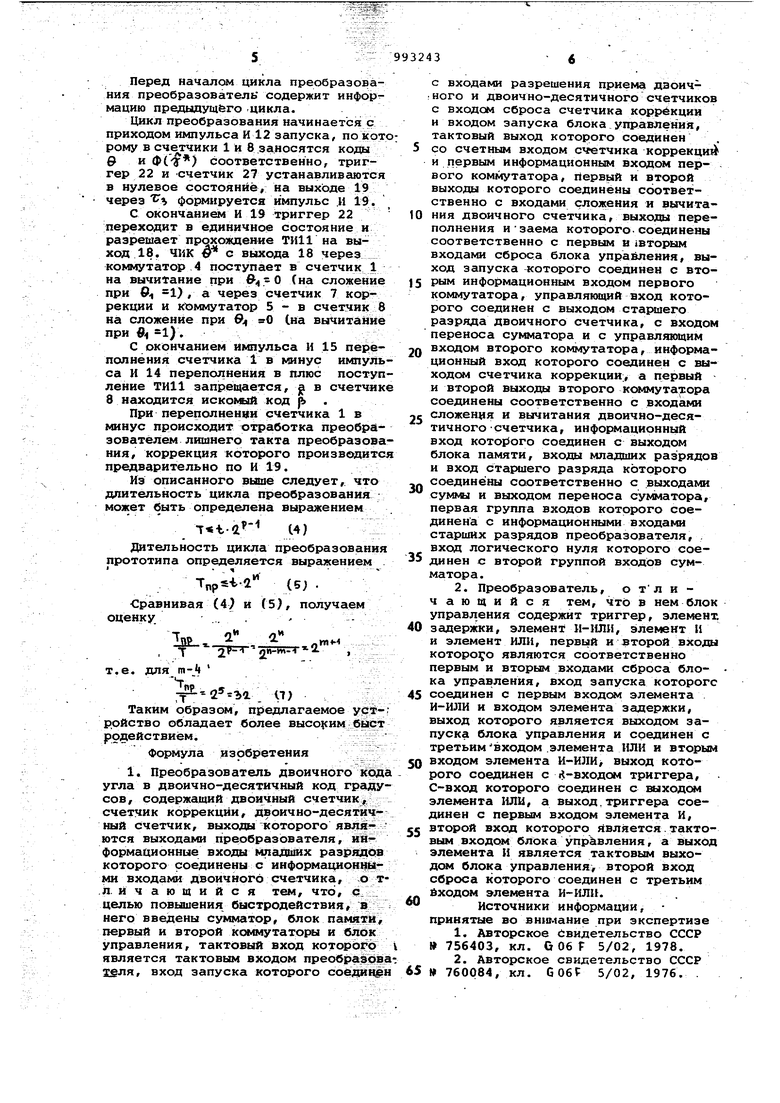

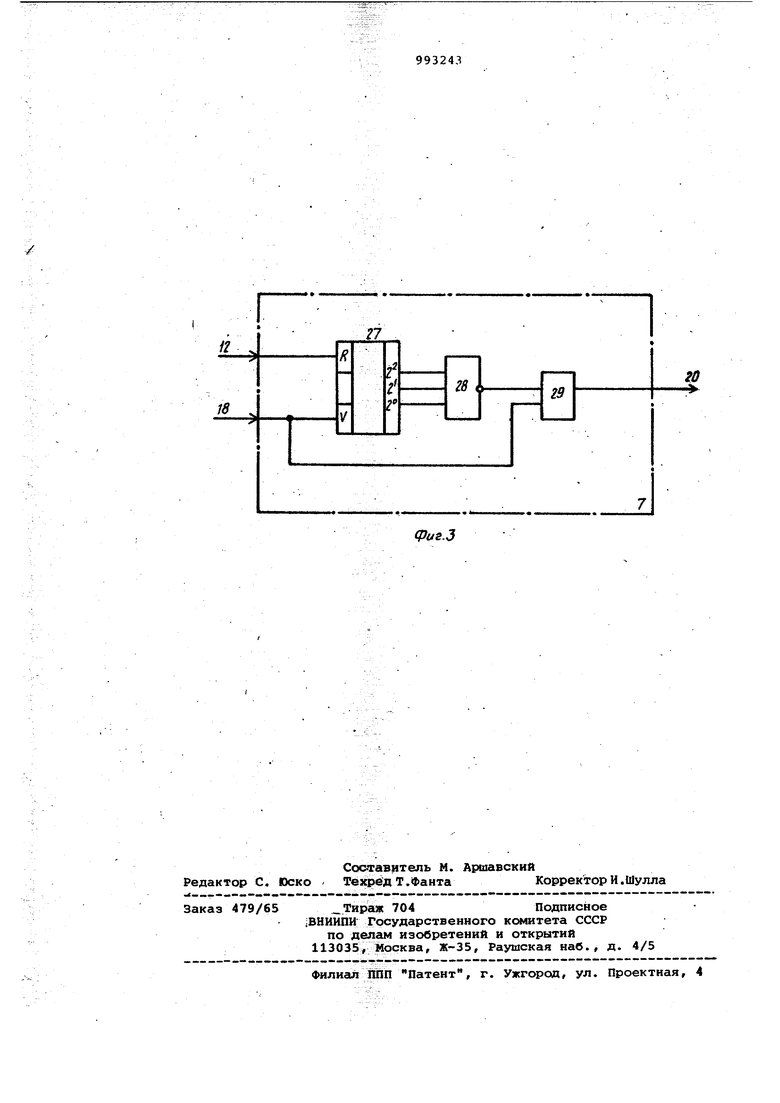

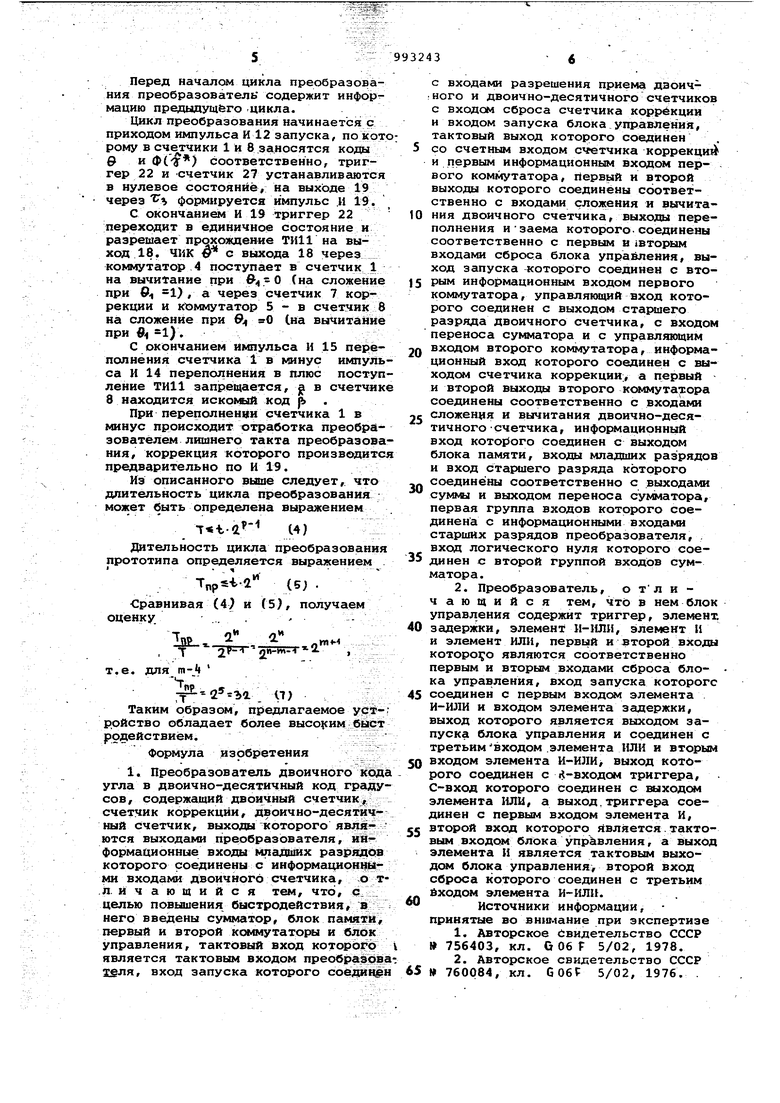

На фиг. 1 приведена структурная схема преобразователя двоичного кода угла в двоично-десятичный код градусов; на фиг. 2 - блок-схема блока управления; на фиг. 3 - схема счетчика коррекции.

На фиг. 1 использованы следующие обозначения: двоичный счетчик 1, сумматор 2, блок 3 памяти, коммутаторы 4 и 5, блок 6 управления, счетчик 7 коррекции, двоично-десятичный счетчик 8, входы 9 старших разрядов кода угла, входы 10 младших разрядов кода угла, тактовый вход 11, вход 12 запуска, выход 13 старшего разряда счетчика 1, выходы 14 и 15 переполнений счетчика 1, выход 16 переноси сумматора 2, выход 17 кода суммы сумматора 2, выходы 18 и 19 блока управления выход 20 счетчика коррекции и кодовый выход 21 двоично-десятичного счетчика 8. Блок 6

управления (фиг. 2) содержит триггер 22, элемент 23 задержки, элемент ИЛИ 24, элемент И-ИЛИ 25, элемент .И 26. Счетчик коррекции 7 (фиг. 3) содержит счетчик 27, элементы И 28 и 29.

Преобразователь работает следующим образом.

Преобразователь выполняет преобразование двоичного п-разрядного кода угла оС в- двоично-десятичный К1эд (% градусов.

При л-12 вес кванта двоичного кода равен Aoi360 /2 sr .51б,

а вес двоично десятичного кода выбран

равным Д|% б;гО,1

Я Для преобразования код

d разделён на дйе части

А А А

-WI

oc,f+e-2

О)

Х и ;

6L.xdL,-ai-l

де

,-.й-|«,

a-V

коды.

образованные m старшими и p-(n-m) младшими разрядами кода соответственно;ol, T-i, 0i разрядные цифры кодов

i, - .

Предлагаемый преобразователь (фиг. 1) регшизован для п-12, т-.

На вход 11 преобразователя поступают тактовые импульсы ТИП, на вход 12 - импульсы И 12.запуска, а на входы 9 и 10 - коды /у и со-. ответственно.

Блок 3 памяти вырабатывает двоично-десятичный код ф(.) по коду f I формируемому сумматором 2 на основе соо но1тдения

f $- ., (1},

где - разрядная цифра старшего

разряда кода Счетчик 7 прео азует число-импульсный код ЧИК 0 двоичного кода , определяемого соотношением

e,vu-e)e, С)

в двоично-де ятйчный число-импульсный код таким образом, чтобы цена каждого импульса была равна О, 1.

Преобразование производится путём запрещения поступления на выход д 20 каждого восьмого.импульса ЧИК в , п(51скольку за время развертки кода

до максимального значения, определяемого квантами, должно быть выдано-«112 импульсов двоично-десятичного число-импульсного кода.

Блок 6 управления предназначен для формирования последовательности сигналоё, синхронизирующих работу преобразователя во времени.

Перед началом цикла преобразования преобразователь содержит инфор мацию предыдущего .цикла.

Цикл преобразования начинается с приходом импульса И 12 запуска, по кото рому в счетчики 1 и 8 заносятся коды В к (ЯУ) соответственно, триггер 22 и Счетчик 27 устанавливаются в нулевое состояние, на выходе 19 через г формируется импульс ,и 19.

С окончаниет И 19 триггер 22 переходит в единичное состояние и разрешает прохождение ТИП на выход 18. ЧИК & с выхода 18 через коммутатор 4 поступает в счетчик 1 на вычитание при (на сложение при & 1), а через счетчик 7 коррекции и кЮммутатор 5 - в счетчик 8 на сложение при & sQ (на вычитание при 9 -I).

С окончанием импульса И 15 переполнения счетчика 1 в минус импульса И 14 переполнения в плюс поступление ТИП запрещается, g в счетчике 8 находится искокклй код

При переполнении счетчика 1 в минус происходит отработка преобразователем лишнего такта преобразования, коррекция которого производится предварительно по И 19.

Из описанного выше следует, что длительность цикла преобразования может быть определена выражением

jpH

t4)

T«t-u

Дительность цикла преобразования прототипа определяется выражением

Tnpfil-i (В) .

Сравнивая (4 и (5), получаем оценку...

ТПР . а а .„ -f -2igT- 2 - -

т.е. для т-Ц

, Ч1

Таким образом, предлагаемое уст-; ррйство обладает более высо)сим быст родействиём.

Формула изобретения

1. Преобразователь двоичного кода угла в двоично-десятичный код градусов, содержащий двоичный счетчик, счетчик коррекции, двоично-десятичный счетчик, выходы которого являются выходами преобразователя, информационные входы младших разрядов которого соединены с информационными входами двоичного счетчика, о т.JI. и ч а ю щ и и с я тем, что, с . целью повышения быстродействия, в него введены сумматор, блок памяти, первый и второй коммутаторы и блок управления, тактовый вход которого является тактовым входом преобразова 1ёля, вход запуска которого соединрн

с входами разрешения приема даоичнего и двоично-десятичного счетчиков с входом сброса счетчика коррекции и входом запуска блока управления, тактовый выход которого соединен

со счетным входом сч«тчика коррекци и первым информационным вхсшсм пер- . вого коммутатора, йервый и второй выхода которого соединены соответственно с входами сложения и вычитания двоичного счетчика, выходы переполнения нзаема которого-соединены соответственно с первым и(вторым входами сброса блока управления, выход запуска -которого соединен с вторым информационным входом первого коммутатора, управляющий вход которого соединен с выходом старшего разряда двоичного счетчика, с входом переноса сумматора и с управлшощим

входом второго коммутатора, информационный вход которого соединен с выходом счетчика коррекции, а первый и второй выходы второго коммута Еора соединены соответственно с входами

сложения и вычитания двоично-десятичного -счетчика, информационный вход KOToi oro соединен с выходом блока памяти, входы младших разрядов и вход старшего разряда которого соединены соответственно с выходами суммы и выходом переноса сукшатора, первая группа входов которого соединена с информационными входами старших разрядов преобразователя, . вход логического нуля которого соединен с второй группой входов сумматора.

2. Преобразователь, о тл и чающийся тем, что в нем блок управления содержит триггер, злекюнт.

задержки, элемент И-1ШИ, элемент И и элемент или, первый и второй входы которого являются соответственно первым и вторым входами сброса блока управления, вход запуска которогс

соединен с перклм входом элемента И-ИЛИ и входом элемента задержки, выход которого является выходом запуска блока управления и соединен с третьимвходом .элемента ИЛИ и вторым

входом элемента И-Ш1И выход которого соединен с -входом триггера, С-вход которого Соединен с выходом элемента 1ШЫ, а выход.триггера соединен с первым входом элемента И,

второй вход которого является.тактовьм входом блока управления, а выход элемента И является тактовым выходом блока управления, второй вход сброса которого соединен с третьим дходом элемента И-ИЛИ. .

Источники информации,

принятые во внш.1ание при экспертизе

1.Авторское Свидетельство СССР 756403, кл. G06F 5/02, 1978.

2.Авторское свидетельство СССР 760084, кл. G06P 5/02, 1976. .

(риг.Э

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1985 |

|

SU1275777A1 |

Авторы

Даты

1983-01-30—Публикация

1981-06-19—Подача