Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники при разработке счетчиков, регистров, делителей частоты, распределителей импульсов, формирователей- парофазного сигнала и тому подобных с повышенной достоверностью функционирования и эксплуатационной отказоустойчивостью.

Целью изобретения является повышение ремонтопригодности путем введения в структуру триггера резервных первой и второй ступеней со средствами автоматической реконфигурации работоспособной структуры.

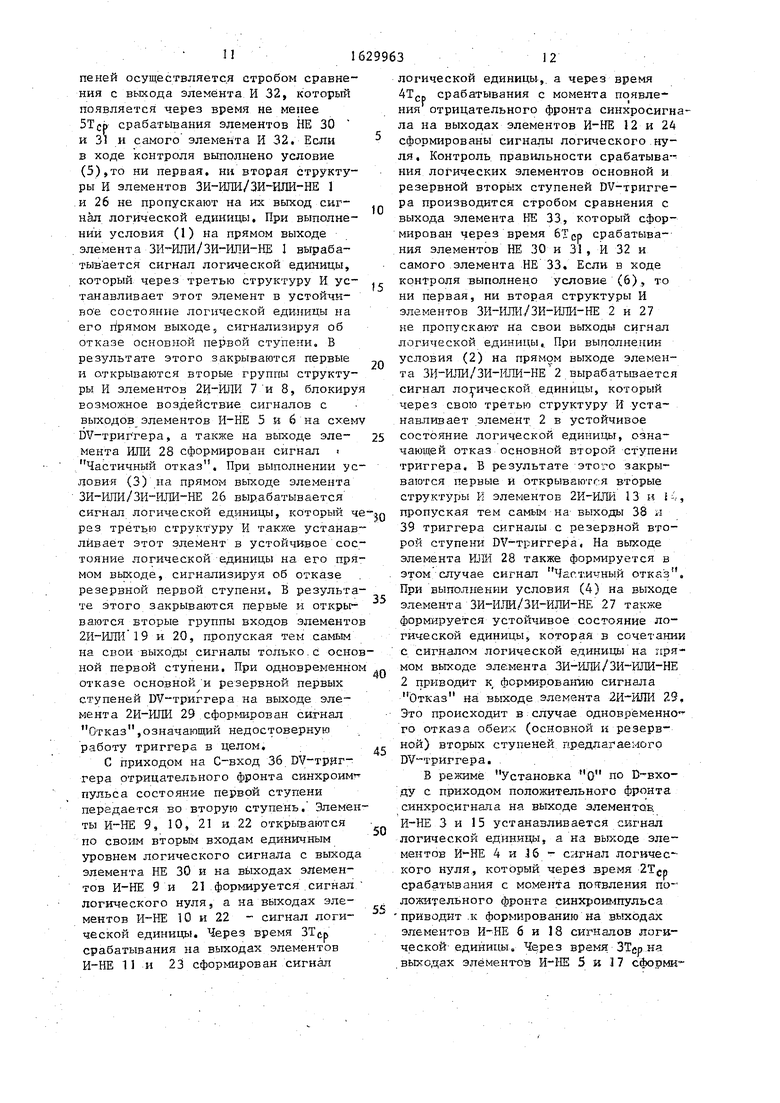

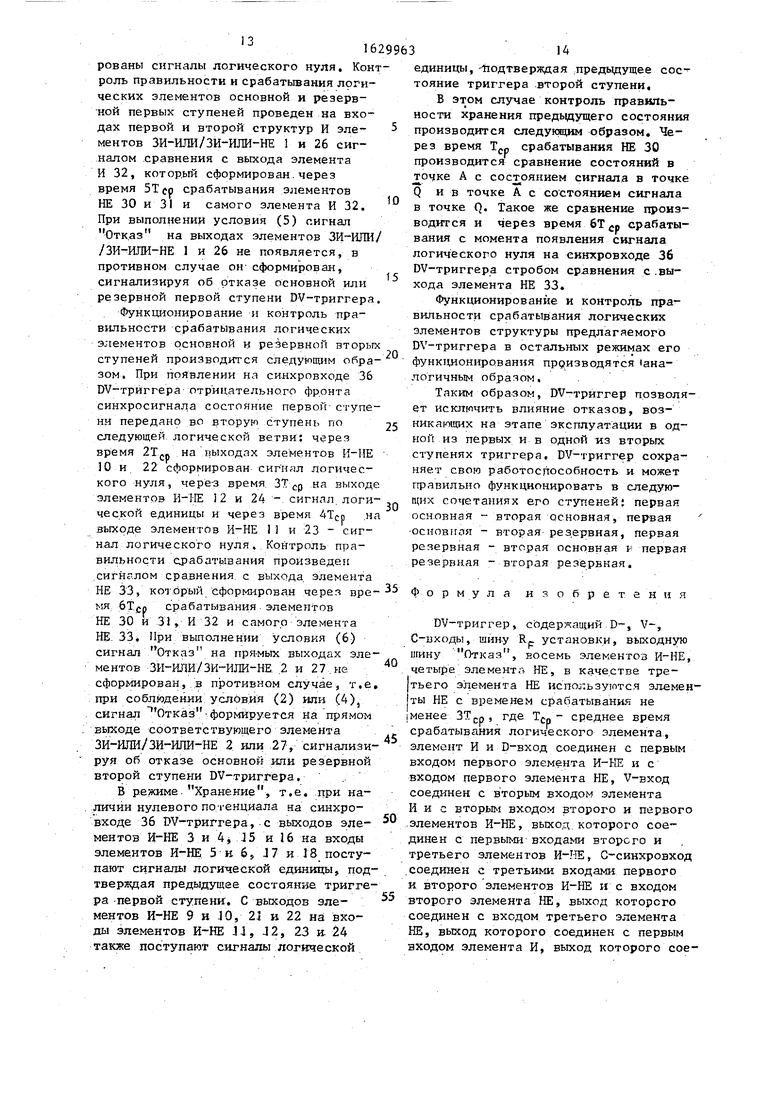

На фиг.1 представлена функциональная схема предлагаемого DV- триггера; на фиг.2 - временные диаграммы его работы.

DV-триггер содержит элементы ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 3 и 2, элементы И-НЕ 3-6, элементы 2И-ИЛИ 7 и 8, элементы И-НЕ 9-12, элементы 2И-ИЛИ 13 и 14, элементы И-НЕ 15-18 элементы 2И-ИЛИ 19 и 20, элементы И-НЕ 21 - 24, элемент НЕ 25, элементы ЗЙ-ИЛИ/ /К-ИПИ-НЕ 26 и 27, элемент ИЛИ 28,

о к

со

CD

о

G3

элемент 2И-ИЛИ 29, элементы НЕ 30 и 31, элемент И 32 и элемент НЕ 33„

D-вход 34 триггера соединен с вторым входом первой структуры И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1, с первыми входами элементов И-НЕ 3 и 15 и с входом элемента НЕ 25. V-вход 35 триггера соединен с вторыми входами элементов И-НЕ 3, 4, 15н1бис вторым входом элемента И 32. Синхро- вход 36 триггера соединен с третьими входами элементов 3, 4, 15 и 16 и с входом элемента НЕ 30. Вход 37 установки в исходное состояние средств функционального контроля триггера соединен с первыми входами третьих структур И элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1, 2 и 26 и 27.

Инверсный выход элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 1 соединен с первыми входами первых структур И элементов 2И-ИЛИ 7 и 8. Прямой выход элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1 соединен с вторым входом своей третьей структуры И, с вторыми входами вторых структур И элементов 2И-ИЛИ 7 и 8, с первым входом элемента ИЛИ 28 и с первым входом первой структуры И элемента 2И-ИЛИ 29.

Инверсный выход элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 2 соединен с первыми входами первых структур И элементов 2И-ИЛИ 13 и 14. Прямой выход элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 соединен с вторым входом своей третьей структуры И, с первыми входами вторых структур И элементов 2И-ИЛИ 13 н 14, с вторым входом элемента ИЛИ 28 и с первым входом второй структуры И элемента 2И-ИЛИ 29.

Выход элемента И-НЕ 3 соединен с первыми входами элементов И-НЕ 5 и 4, Выход элемента И-НЕ 4 соединен с вторым входом элемента И-НЕ 6. Выход эле мента И-НЕ 5 соединен с первым входом элемента 6, с вторым входом первой структуры И элемента 2И-ИЛИ 7 и с первым входом второй структуры И

элемента 2И-ИЛИ 19. Выход элемента

И-НЕ 6 соединен с вторым входом элемента И-НЕ 5, с вторым входом первой структуры И элемента 2И-ИЛИ 8 и с первым входом второй структуры элемента 2И-ИЛИ 20, а также с первым входом второй структуры И элемента 2И-ИЛИ 8.

Выход элемента 2И-ИЛИ 7 соединен с первым входом элемента И-НЕ 9, с

O 5

0 5 0

Q

5

0

первым входом второй структуры И элемента ЗИ-ШШ/ЗИ-ИЛИ-НЕ 1 и с вторым входом второй структуры И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2. Выход элемента 2И-ИЛИ 8 соединен с первым входом элемента И-НЕ 10, с первым входом первой структуры И элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 1 и с вторым входом первой структуры И элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 2.

Выход элемента И-НЕ 9 соединен с первым входом элемента И-НЕ 1, выход которого соединен с вторым входом первой структуры элемента 2И-ИЛИ 13, с первым входом элемента И-НЕ 32 и с первым входом первой структуры элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2. Выход элемента И-НЕ 10 соединен с вторым входом элемента 12, выход которого соединен с вторым входом первой структуры И элемента 2И-ИЛИ 14, с вторым входом элемента 11 и с первым входом первой структуры И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2,

Выход элемента И-НЕ 15 соединен с первыми входами элементов 17 и 16. Выход элемента И-НЕ 16 соединен с вторым входом элемента И-НЕ 18, выход которого соединен с вторым входом элемента 17, с вторым входом первой структуры Ь элемента 2И-ИЛИ 20. Выход элемента И-НЬ 17 соединен с первым входом элемента И-НЕ 18, с первым входом второй структуры И элемента 2И-ИЛИ 7 и с вторым входом первой структуры И элемента 2Я-ИЛИ 19.

Выход элемента 2И-ИЛИ 1 9 соединен с первым входом элемента И-НЕ 21, с первым входом второй структуры И элемента ЗИ-ИЛИ/ЗИ-ШШ-НЕ 26 и с вчорым входом второй структуры л элемента Зй-ИЛИ/ЗИ-ИЛИ-НЕ 27. Выход элемента ЗИ-ИЛИ 20 соединен с первым входом элемента И-НЕ 22, с первым входом первой структуры И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 26 и с вторым уходом первой структуры И элемента ЗИ-ИЛИ/ЗИ-ИЛК-НЕ 27

Выход элемента И-НЕ 21 соединен с первым входом элемента И-КЕ 23,, выход которого соединен с вторым входом второй структуры И элемента 2И-ИЛИ 13, с первым входом элемента -И-НЕ 24 и с первым входом первой структуры И элемента ЗИ-ШШ/ЗИ-ИЛИ-НЕ 27. Выход элемента 22 соединен с вторым входом Элемента И-НЕ 24, выход которого соединен с вторым входо второй структуры И элемента 2И-ИЛИ 14, с вторым входом элемента 23 и с первым входом второй структуры И элемента ЗИ-ИЛИ/ЗИ-ШШ-НЕ 27.

Выход элемента НЕ 25 соединен с вторым входом второй структуры И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1 и с вторым входом второй структуры И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 26.

Инверсный выход элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 26 соединен с первыми входами первых структур И элементов 2И-ИЛИ 19 и 20. Прямой выход элемент ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 26 соединен с вторым входом своей третьей структуры И, с вторыми входами вторых структур И элементов 2И-ИЛИ 19 и 20, с четвертым входом элемента ИПИ 28 и с вторым входом первой структуры II элемента 2И-ИЛИ 29,

Прямой выход элемента ЗИ-ИЛИ/ ЗИ-ИЛИ-НЕ 27 соединен с вторым входо своей третьей структуры И, с третьим входом элемента ИЛИ 28 и с вторым вхдом второй структуры И элемента 2И-ИЛИ 29.

Выход элемента НЕ 30 соединен с входом элемента НЕ 31, с четвертыми входами первой и второй структур И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2, с вторыми входами элементов И-НЕ 9, 10, 21 и 22. с четвертыми входтми первой и второй структур И элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 27.

Выход элемента НЕ 31 соединен с первым входом элемента ИЗ/, выход которого соединен с входом элемента НЕ 33, с третьими входами первой и второй структур И элемента ЗИ-ИЛК/ /ЗИ-ИЛИ-НЕ 1 и с третьими входами первой и второй структур И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1 и с третьими входами первой и второй структур И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 26.

Выход элемента НЕ 33 соединен с третьими входами первой и второй структур И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 и с третьими входами первой и второй структур И элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 27.

Выход элемента 2И-ИЛИ 13 является прямым выходом 38 предлагаемого DV-триггера, Выход элемента 2И-ИЛИ 14 является инверсным выходом 39 триггера.

Выход элемента ИЛИ 28 является выходом Частичный отказ 40 DV-триггера. Выход-элемента 2И-ИЛИ 29 является выходом Отказ 41 триггера.

Функциональное назначение логических элементов структуры предлагаемого

DV-триггера заключается в следующем.

Элементы ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1,2, 26 и 27 представляют собой однофазные триггеры, осуществляющие на своих

первых и вторых структурах И контроль правильности срабатывания соответствующих им первых основной и резервной ступеней, вторых основной и резервной ступеней.

5 Функционал отказа, реализованный на первой и второй группах входов по И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1, можно представить следующим выражением:

A-V-C-A v D.V-C-A i. (i)

0Функционал отказа, реализованный

на входах первой и второй структур И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2, можно предетавить следующим выражением: О-А-С V ГЬА С 1.(2)

5 Функцио гал отказа, реализованный на входах первой и второй структур И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 26, можно предста.ви-гь следующим выражением: D-VvON V D V-C-N 1(3)

0 Функционал отказа, реализованный на входах первой и второй структур И элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 27, можно предс пвить следующим выр- ением: M N-C V M-N C 1 .(4)

Выполнение условий одного из .УГЧО- шений (1)-(4) приводит к тому, что соответствующий элемент ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ посредством своей обратной связи через соответствующую

0 третью структуру И устанавливается в устойчивое сосюяние логической единицы, означающей отказ соответствующей основной или резервной, первой или второй ступеней DV-триггера«

5 |

Элементы И-НЕ 3-6 образуют схему

основного триггера первой ступени.

Элементы 2И-ИЛИ 7 и 8 пропускают на свои выходы сигналы с выходов 0 основной первой ступени или с выходов резервной ступени триггера, в зависимости от их исправного (неисправного) состояния.

Элементы И-НЕ 9-12 образуют схему е основной второй ступени триггера.

Элементы 2И-ИЛИ 13 и 14 пропускают на выходы 38 и 39 соответственно сигналы с выходов основной или резервной вторых ступеней триггера, в зависимос5

ти от их исправного (неисправного) состояния.

Элементы И-НЕ 35-18 образуют схему резервной первой ступени триггера,

Элементы 2И-ИЛИ 39 к 20 пропускают на свои выходы сигналы с выходов основной и резервной первой ступеней триггера, в зависимости от исправного (неисправного) состояния резервной первой ступени.

Элементы И-НЕ 2-1-24 образуют схему резервной второй ступени, триггера.

Элемент НЕ 25 инвертирует сигнал с входа 34 DV-триггера, формируя тем самым аргумент D для функционала отказов в равенствах (1) я (3).

Элемент НЕ 30 инвертирует синхросигнал, подаваемый на вход 36 DV- триггера, реализуя тем самым двухтактный режим его работы при наличии одного синхровхода. Кроме того, на выходе элемента НЕ 30 формируется нулевой уровень сигнала Отсечки проведения этапа контроля основной и резервной вторых ступеней триггера на время действия единичного логического уровня сигнала на входе 36, что предотвращает ложное срабат ша- ние схемы контроля при смене состояний в основной и резервной ступенях триггера.

Элемент НЕ 31 инвертирует сигнал, приходящий с выхода элемента НЕ 30, и обеспечивает формирование противо- пол ожнрго ему сигнала через время не менее ЗТср , где ТСр- среднее время срабатывания логического эле мента структуры DV-триггера, что обеспечивает корректный контроль первых ступеней (основной и резервной) на структурах И элементов ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 1 и 26 при установке по V-входу триггера.

Элемент И 32 формирует на своем выходе сигнал строба сравнения для первой и второй структур И элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1 и 26 через время не менее 5ТСр, т.е. через полное вре мя завершения переходных процессов в основной и резервной первых ступенях триггера.

Элемент НЕ 33 формирует на своем выходе сигнал строба сравнения для элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 к 27, который,является противоположным сигналу на выходе элемента И 32, через время 6Тср сравнения с момента окончания действия сигнала высокого логического уровня на синхровходе 36. Время бТср срабатывания является временем завершения переходных процессов в основной и резервной вторых ступенях DV-триггера.

Элементы 2И-ИЛИ 13 и 14 пропускают на прямой 38 и инверсный 39 выходы DV-триггера сигналы с выходов основной или резервной вторых ступеней, в зависимости от исправного (неисправного) состояния основной первой ступени,

Элемент ИЛИ 28 формирует на своем выходе сигнал Частичный отказ, который, поступая на выход 40 DV-триггера сигнализирует о недостоверной работе одной из его ступеней.

Элемент 29 формирует на своем выходе сигнал Отказ (полный отказ), который, поступая на выход 4 DV-триггера, сигнализирует о недостоверной работе устройства из-за одновременного отказа либо обеих первых ступеней (основной и резервной), либо обеих вторых ступеней DV-триггера,

Отличительной особенностью элемента НЕ 31 является то, что наряду с функционально-логической нагрузкой, он выполняет функиию задержки времени- функционирования сигнала на своем выходе. Время срабатывания элемента НЕ 31 должно быть не менее 3 Т™ . Это условие можно выполнить при разработке технологии производства микросхемы следующими путями: увеличением количества последовательно включеншгх транзисторов в элементе НЕ 31; технологией изготовления„ т,е, увеличением геометрических размеров базы траьзистора этого логического элемента по сравнению с другими логическими элементами структуры DV-триггера 5 увеличением резисторной и емкостной нагрузок логического элемента НЕ 31.

DV-триггер работает следующим образом.

После включения питания на Rp-вход триггера (на шину 37) подается нулевой уровень сигнала для устзьовки в исходное состояние срадстз функционального контроля (СФК), так как в силу случайного характера переходных процессов во время включения питания элементы ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1, 2, 26 и 27, представляющие собой однофазные триггеры, могут устанавливаться в i

V-N где D, D

единичные состояния на своих прямых выходах, соответствующие фиксации отказа контролируемой ими ступени DV-триггера. ,

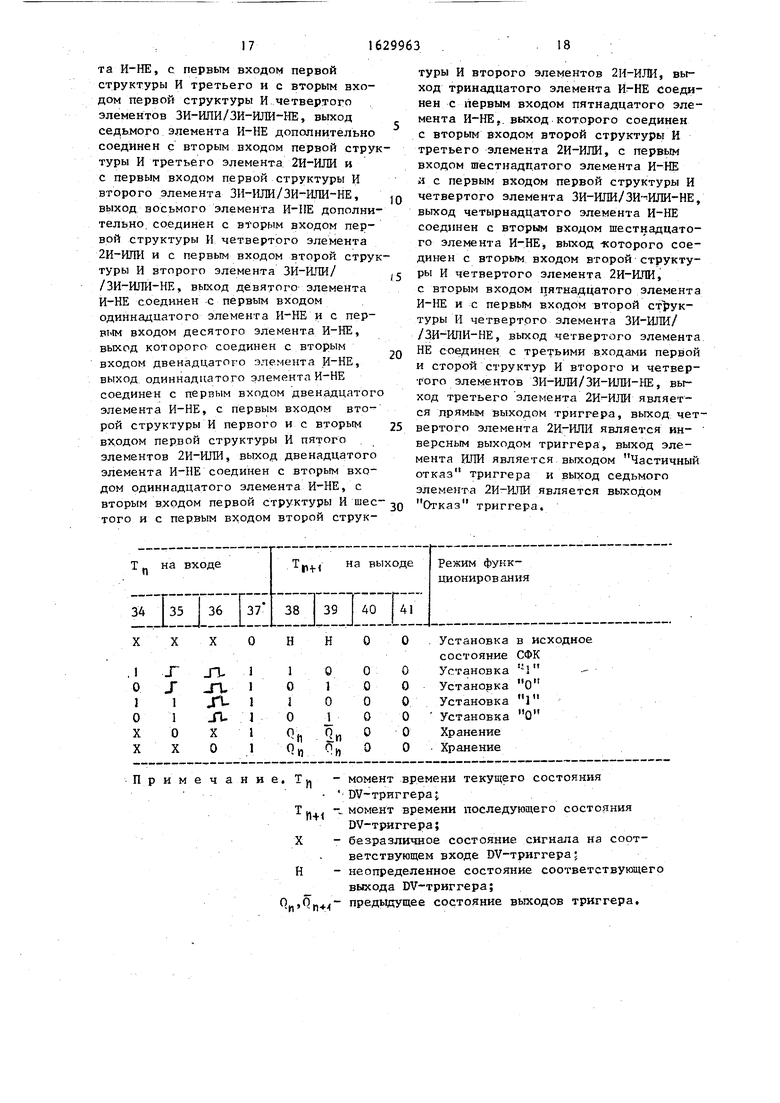

Далее при исправном состоянии всех логических элементов структуры DV-триггера его работа подчиняется (соответствует) закону функционирования, приведенному в таблице перехо- дов DV-триггера.

В процессе своего функционирования основная и резервная первые ступени DV-триггера подчиняются закону, представленному следующим выражением: (D OV.A 0) V(D C.V-A 0) V(D CX 0) V (D-C-ViN 0), (5)

единичное и нулевое соответственно состояния сиг- налов на входе 34 DV- григгора;

единичное состояние сигнала на выходе элемента И 32 триггера;

состояния сигналов в точках А и А соответственно; состояния сигналов в точках N и N соответственно За выполнением условий выражения (5) следят первая и вторая структуры И элементов ЗИ-ИЛИ/ЗИ-Ш1И-НЕ 1

и 26.

В процессе своего функционирования основная и резервная вторые ступени DV-триггера подчиняются закону, который можно представить следующим выражением:

о-А оГс) омз) olvrM-if (vTc) () qj, , 1(6)

где V С - единичное состояние сигнала на выходе элемента НЕ 33;

состояния сигналов в точках Q и Q соответствен но

М - состояния сигналов в точках М и М соответственно,

OV А, А - N, N

Q, Q М,

За выполнением условий выражения (6) следят первая и вторая структуры И элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 и 27.

В случае нарушения условий функ- ционирования э представленных в выражении (5), на соответствующем прямом выходе элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1 или 26 уже в момент срабатывания ло

5

д

5

0

гических элементов первой ступени формируется единичный сигнал отказа.

Для основной первой ступени он сформирован при условии выполнения равенства (1), а для резервной первой ступени сигнал отказа сформирован на выходе элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 26 при условии выполнения равенства (3).

В случае нарушения условий функционирования, представленных в выражении (6), на соответствующем прямом выходе элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 или 27 также вырабатывается сигнал отказа одной или обеих одновременно второй ступени DV-триггера.

Для основной второй ступени он сформирован на прямом выходе элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 при условии выполнения равенства (2), а для резервной второй ступени сигнал отказа сформирован на прямом выходе элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 27 при условии выполнения равенства (4).

Рассматривают последовательность срабатывания всех элементов логической структуры предлагаемого DV-триггера в его трех основных режимах функционирования: Хранение, Установка 1 и Установка О.

В режиме Установка l no D-вхо- ду с поступлением положительного фронта синхросигнала на вход 36 триггера на выходе элемента И-НЕ 3 через время Тср срабатывания этого элемента устанавливается сигнал логического нуля. Следовательно, через время 2Тсо срабатывания с момента поступления положительного фронта сигнала на вход 36 на выходах элементов И-НЕ 4 и 5 устанавливаются сигналы логической единицы и через время ЗТсп срабатывания на выходе четвертого элемента И-НЕ 6 устанавливается сигнал логического нуля. Таким образом, через время 4ТСр срабатывания в точке А (фиг.1) установлено состояние единицы, а в точке А - состояние логического нуля. Аналогичным образом срабатывает и резервная первая ступень триггера (элементы И-НЕ 15- 18), в результате чего через время 4ТСР срабатывания в точке N установлено состояние логической единицы, а в точке N - состояние логического нуля..

Контроль правильности срабатывания основной и резервной первых стул

пеней осуществляется стробом сравнения с выхода элемента И 32, который появляется через время не менее 5ТСр срабатывания элементов НЕ 30 и 31 и самого элемента И 32, Если в ходе контроля выполнено условие (5),то ни первая, ни вторая структуры И элементов ЗИ-ИПИ/ЗИ ЩЩ-НЕ 1 и 26 не пропускают на их выход сигнал логической единицы. При выполнении условия (1) на прямом выходе элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ I вырабатывается сигнал логической единицы, который через третью структуру И устанавливает этот элемент в устойчивое состояние логической единицы на его прямом выходе, сигнализируя об отказе основной первой ступени. В результате этого закрываются первые и открываются вторые группы структуры И элементов 2И-ИЛИ 7 и 8, блокируя возможное воздействие сигналов с выходов элементов И-НЕ 5 и б на схему DV-триггера, а также на выходе элемента ИЛИ 28 сформирован сигнал Частичный отказ. При выполнении условия (3) на прямом выходе элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 26 вырабатывается сигнал логической единицы, который че рез третью структуру И также устанав ливает этот элемент в устойчивое состояние логической единицы на его прямом выходе, сигнализирзгя об отказе резервной первой ступени, В результате этого закрываются первые и открываются вторые группы входов элементов 2И-ШШ 19 и 20, пропуская тем самым на свои выходы сигналы только с основной первой ступени, При одновременном отказе основной и резервной первых

j

ступеней DV-триггера на выходе элемента 2И-ИЛИ 29 сформирован сигнал Отказ,означающий недостоверную работу триггера в целом.

С приходом на С-вход 36 DV-тряг- гера отрицательного фронта синхроим пульса состояние первой ступени передается во вторую ступень. Элементы И-НЕ 9, 10, 21 и 22 открываются по своим вторым входам единичным уровнем логического сигнала с выхода элемента НЕ 30 и на выходах элементов И-НЕ 9 и 21 формируется сигнал логического нуля, а на выходах элементов И-НЕ 10 и 22 - сигнал логической единицы. Через время ЗТСр срабатывания на выходах элементов И-НЕ 11 и 23 сформирован сигнал

п

96312

логической единицы, а через время

0

5

0

5

п

5

0

5

0

5

4Тср срабатывания с момента появления отрицательного фронта синхросигнала на выходах элементов И-НЕ 12 и 24 сформированы сигналы логического нуля . Контроль правильности срабатывания логических элементов основной и резервной вторых ступеней DV-триггера производится стробом сравнения с выхода элемента НЕ 33, который сформирован через время срабатывания элементов НЕ 30 и 31, И 32 и самого элемента НЕ 33. Если в ходе контроля выполнено условие (6), то ни первая, ни вторая структуры И элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 и 27 не пропускают на свои выходы сигнал логической единицы. При выполнении условия (2) на прямом выходе элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕТ2 вырабатывается сигнал логической единицы, который через свою третью структуру И устанавливает элемент 2 в устойчивое состояние логической единицы, означающей отказ основной второй ступени триггера, В результате этого закрываются первые и открываютгя вторые структуры И элементов 2И-ИЛИ 13 и - , пропуская тем самым на выходы 38 л 39 триггера сигналы с резервной второй ступени DV-триггера, На выходе элемента ИЛИ 28 также формируется в этом случае сигнал Частичный отказ. При выполнении условия (4) на выходе элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 27 также формируется устойчивое состояние логической единицы, которая в сочетании с сигналом логической единицы на прямом выходе элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 приводит к формированию сигнала Отказ на выходе элемента 2И-ИЛИ 29. Это происходит в случае одновременно-- го отказа (основной к резервной) вторых ступеней предлагаемого DV-триггера.

В режиме Установка О по D-вхо- ду с приходом положительного фронта синхросигнала на выходе элементов И-НЕ 3 и 15 устанавливается сигнал логической единицы, а на выходе элементов И-НЕ 4 и J6 - сигнал логического нуля, который через время 2ТСр срабатывания с момента появления положительного фронта синхроимпульса приводит к формированию на выходах элементов И-НЕ б и 18 сигналов логической единицы. Через время ЗТСр на выходах элементов И-НЕ 5 и 7 сформн

рованы сигналы логического нуля. Конт роль правильности и срабатывания логических элементов основной и резервной первых ступеней проведен на входах первой и второй структур И элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1 и 26 сигналом сравнения с выхода элемента И 32, который сформирован через время 5Тсо срабатывания элементов НЕ 30 и 31 и самого элемента И 32. При выполнении условия (5) г.игнал Отказ на выходах элементов ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 1 и 26 не появляется, в противном случае он сформирован, сигнализируя об отказе основной или резервной первой ступени DV-триггера.

Функционирование и контроль правильности срабатывания логических элементов основной и резервной вторых ступеней производится следующим образом. При появлении на синхровходе 36 DV-триггера отрицательного фронта синхросигнала состояние первой ступени передано во вторую ступень по следующей логической ветви: через время 2Тср на выходах элементов И-НЕ 10 и 22 сформирован сигнал логического нуля, через время ЗТ с(} на выходе элементов И-НЕ 12 и 2Ј - сигнал логической единицы и через время на выходе элементов 11 и 23 - сигнал логического нуля. Контроль поа- вильности срабатывания произведен сигнглом сравнения с выхода элемента НЕ 33, который сформирован через вре-

5 5

0

0

единицы, -подтверждая предыдущее состояние триггера второй ступени.

В этом случае контроль правильности хранения предыдущего состояния производится следующим образом. Через время Тср срабатывания НЕ 30 производится сравнение состояний в точке А с состоянием сигнала в точке Q ив точке А с состоянием сигнала в точке Q. Такое же сравнение производится и через время 6Т с« срабатывания с момента появления сигнала логического нуля на синхровходе Зб DV-триггера стробом сравнения с выхода элемента НЕ 33.

Функционирование и контроль правильности срабатывания логических элементов структуры предлагаемого DV-триггера в остальных режимах его функционирования производятся аналогичным образом.

Таким образом, DV-триггер позволяет исключить влияние отказов, возникающих на этапе эксплуатации в одной из первых и в одной из вторых ступенях триггера, DV-триггер сохраняет свою работоспособность и может правильно функционировать в следующих сочетаниях его ступеней: первая основная - вторая основная, первая основная - вторая резервная, первая резервная - вторая основная v первая резервная - вторая резервная.

Формула

н

обретен и ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный RS-триггер | 1989 |

|

SU1629962A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Счетчик-делитель | 1989 |

|

SU1598169A1 |

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| DV-триггер | 1987 |

|

SU1465936A1 |

Изобретение относится к цифровой технике и может быть использовано в автоматике и вычислительной технике при построении счетчиков, регистров, делителей частоты, распределителей импульсов и формирователей па- рофазного сигнала с повышенной ремонтопригодностью и достоверностью функционирования. Цель изобретения повышение ремонтопригодности. Устройство содержит элементы И-НЕ 15-18 и 21-24, элементы 2И-ЙЛИ 7, 8, 13, 14, 19 и 20, элементы ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 1 и 2 и элемент ИЛИ 28. В совокупности с элементами И-НЕ 3-6 и 9-12, элементами НЕ 25, 30, 31 и 33, И 32 с соответствующими конструктивными связями в данном техническом решении обеспечивается одновременное срабатывание основных и резервных ступеней, непрерывный встроенный контроль за правильностью срабатывания и, в случае отказа какой-либо из ступеней, автоматическое перестроение работоспособной структуры DV-триггера путем покрытия отказавшей ступени резервной. В случае одновременного отказа двух первых или двух вторых ступеней на выходе 41 вырабатывается сигнал Отказ, сигнализирующий недостоверную работу DV-триггера. 2 ил., 1 табл. SS (Л

мя 6Т

ср

срабатывания элементов

НЕ 30 и 31, И 32 и самого элемента НЕ 33. При выполнении условия (6) сигнал Отказ на прямых выходах элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 и 27 не сформирован, в противном случае, т.е. при соблюдении условия (2) или (4), сигнал Отказ формируется на прямом выходе соответствующего элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 2 или 27, сигнализируя об отказе основной или резервной второй ступени DV-триггера,

В режиме Хранение, т.е. при наличии нулевого по генциала на синхровходе 36 DV-триггера, с выходов элементов И-НЕ Зи4, 45 входы элементов И-НЕ 5нб 47и48 поступают сигналы логической единицы, подтверждая предыдущее состояние триггера первой ступени. С выходов элементов И-НЕ 9 и 40, 21 к 22 на входы элементов И-НЕ J4, J2, 23 и- 24 также поступают сигналы логической

5

0

0

DV-триггер, содержащий D-, V-, С-входы, шину Rp установки, выходную шину Отказ, восемь элементов И-НЕ, четыре эле мент НЕ, в качестве третьего элемента НЕ используются элементы НЕ с временем срабатывания не |менее ЗТС„, где ТСр- среднее время срабатывания логического элемента, элемент И и D-вход соединен с первым входом первого элемента И-НЕ и с входом первого элемента НЕ, V-вход соединен с вторым входом элемента И и с вторым входом второго и первого элементов И-НЕ, выхоц которого соединен с первыми входами второго и третьего элементов , С-синхровход соединен с третьими входами первого к второго элементов И-НЕ и с входом 5 второго элемента НЕ, выход которого соединен с входом третьего элемента НЕ, выход которого соединен с первым входом элемента И, выход которого сое

динен с входом четвертого элемента НЕ, выход второго элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ, выход которого соединен с вторым входом третьего элемент И-НЕ, выход третьего элемента И-НЕ соединен с первым входом четвертого элемента И-НЕ, выходы пятого и шестого элементов И-НЕ соединены соответственно с первым входом седьмого и с вторым входом восьмого элементов И-НЕ, выход седьмого элемента соединен с первым входом восьмого элемента И-НЕ, выход которого соеди- нен с вторым входом седьмого элемента И-ПЕ, выход второго элемента НЕ соединен с вторыми входами пятого и шестого элементов отличающийся тем, что, с целью повышения ремонтопригодности, в него введены восемь элементов И-НЕ, се элементов 2И-ИЛИ, четыре элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и элемент ИЛИ, шина установки соединена с первыми входа- ми третьих структур и всех четырех элементов ЗИ-ИПИ/ЗИ-ИЛИ-НЕ, D-вход дополнительно соединен с вторим вхо- дом первой структуры И первого и третьего элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и с первым входом девятого элемента И-НЕ, V-вход дополнительно соединен с вторыми входами девятого и десятого элементов И-НЕ, С-синхровход дополнительно соединен с третьими вхо- дами девятого и десятого элементов И-НЕ, выход первого элемента НЕ соединен с вторыми входами вторых структур И первого и третьего элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ, выход второго элемента НЕ дополнительно соединен с четвертыми входами первой и второй структур И второго и четвертого элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и с вторыми входами тринадцатого и четырнадцатог элементов И-НЕ, выход элэмента И дополнительно соединен с третьими входами первой и второй структур И первого и третьего элементов ЗЧ-ИЛИ/ /ЗИ-ИЛИ-ИЕ, инверсный выход первого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ соединен с первыми входами первых структур И первого и второго элементов 2И-ИЛИ, прямой выход первого элемента ЗИ--ИЛИ /ЗИ-ИЛИ-НЕ соединен с вторым входом своей третьей структуры К, с вторыми входами вторых структур И первого и .второго элементов 2И-ШШ, с первым входом элемента ИЛИ и с первым вхо0

- ,„ 5 0 . Q д-

дом первой структуры И седьмого элемента 2И-ИЛИ, инверсный выход второго элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ соединен с первыми входами первых структур И третьего и четвертого элементов 2И-ИЛИ, прямой выход второго элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ соединен с вторым входом своей третьей структуры И, с первыми входами вторых структур И третьего и четвертого элементов 2И-ИЛИ, с вторым входом элемента ИЛИ и с первым входом второй структуры И седьмого элемента 2И-ИЛИ5 инверсный выход третьего эпемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ соединен с первыми входами первых структур И пятого и шестого элементов 2И-ИЛИ, прямой выход третьего элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ соединен с вторым входом своей третьей структуры И, с вторыми входами вторых структур И пятого и шестого элементов 2И-ИЛИ, с четвертым входом элемента ИЛИ л с вторым входом первой структуры И седьмого элемент 2И-ИЛИ, прямой выход четвертого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ соединен с вторым входом свое тре ъей структуры И, с треч.им входом элемента ИЛИ и с вторым входом вгророй структ -- ры И седьмого эл мента 2И-ТПИ, выход третьего эпепента И-НЕ дополнительно соединен с /вторые входом первой структуры И первого и с первым иходом второй структуры И пятого элементов 2И-ИЛИ, выход ч&1 тертого ,лле мента И-НЕ дополнительно соед .лен с вторым входом первой ст чуктуры И второго и с первым входом второй структуры И шестого элементов 1И-ИЛИ, выход порвого элемента 2И--ИЛИ соеди- ii -i- с первым входом пятого элемента И-Иь, с первым входом второй структуры И первого и с втором входом второй структуры И второго элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ, вьп.од второго элемента 2И-ИЛИ соединен с первым вхо- до.-i шестого элемента И-НЕ, с первым входом первой структуры И первого к с вторым входом первой структуры il

второго ЗИ 11ЛИУЗИ-Ш1И-НЕ, выход пятого элемента 2И-ИЛИ соединен г, первым „ходом тринадцатого эле мента И-ПК, с первым входом второй структуры И третьего и с вторым входом второй структуры И четвертого элементов ЗИ-ИШ/ЗИ-ИПИ-НЕ, выход шестого элемента 2И-ИЛИ соединен с nepBfci t входом четырнадцатого элемен™

та И-НЕ, с первым входом первой структуры И третьего и с вторым входом первой структуры И четвертого элементов ЗИ-Ш1И/ЗИ-ИЛИ-НЕ, выход седьмого элемента И-НЕ дополнительно соединен с вторым входом первой структуры И третьего элемента 2И-ИЛИ и с первым входом первой структуры И второго элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ, выход восьмого элемента И-НЕ дополнительно соединен с вторым входом первой структуры И четвертого элемента 2И-ИЛИ и с первым входом второй структуры И второго элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ, вьгход девятого элемента И-НЕ соединен с первым входом одиннадцатого элемента И-НЕ и с первым входом десятого элемента И-НЕ, выход которого соединен с вторым входом двенадцатого -элемента И-НЕ, выход одиннадцатого элемента И-НЕ соединен с первым входом двенадцатог элемента И-НЕ, с первым входом второй структуры И первого и с вторым входом первой структуры И пятого элементов 2И-ИЛИ, выход двенадцатого элемента И-НЕ соединен с вторым входом одиннадцатого элемента И-НЕ, с вторым входом первой структуры И шестого и с первым входом второй струкПримечание. Tfj - момент времени текущего состояния

DV-триггера; Т п . - момент времени последующего состояния

DV-триггера;

X - безразличное состояние сигнала на соответствующем входе DV-триггера; Н - неопределенное состояние соответствующего

выхода DV-триггера; О ,0.- предыдущее состояние выходов триггера.

туры И второго элементов 2И-ИЛИ, выход тринадцатого элемента И-НЕ соединен с первым входом пятнадцатого эле- мента И-НЕ, выход которого соединен с вторым входом второй структуры И третьего элемента 2И-ИЛИ, с первым входом шестнадпатого элемента И-НЕ я с первым входом первой структуры И

четвертого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ, выход четырнадцатого элемента И-НЕ соединен с вторым входом шестнадцатого элемента И-НЕ, выход -которого соединен с вторым входом второй структуры И четвертого элемента 2И-ИЛИ,

с вторым входом пятнадцатого элемента И-НЕ и с первым входом второй структуры И четвертого элемента ЗИ-ИЛИ/ /ЗИ ИЛИ-НЕ, выход четвертого элемента

НЕ соединен с третьими входами первой и сторой структур И второго и четвертого элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ, выход третьего элемента 2И-ИЛИ является прямым выходом триггера, выход четвертого элемента 2И-ИЛИ является инверсным выходом триггера, выход элемента ИЛИ является вьгходом Частичный отказ триггера и выход седьмого элемента 2И-ИЛИ является выходом

Отказ триггера.

Фиг.

ЙА

Фи$,2

| Файзулаев Б.Н | |||

| и др | |||

| Основы построения технических средств ЕС ЭВМ на интегральных микросхемах,- М.: Радио и связь, 1981, с.131, рис.4.3В | |||

| Авторское свидетельство СССР по заявке S 4273503/24-2J, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-23—Публикация

1989-03-31—Подача