Изобретение относится к электронике и вычислительной технике и может быть использовано при проектировании сумматоров и арифметических блоков цифровых БИС на ШОП транзисторах.

Цель изобретения - повышение надежности.

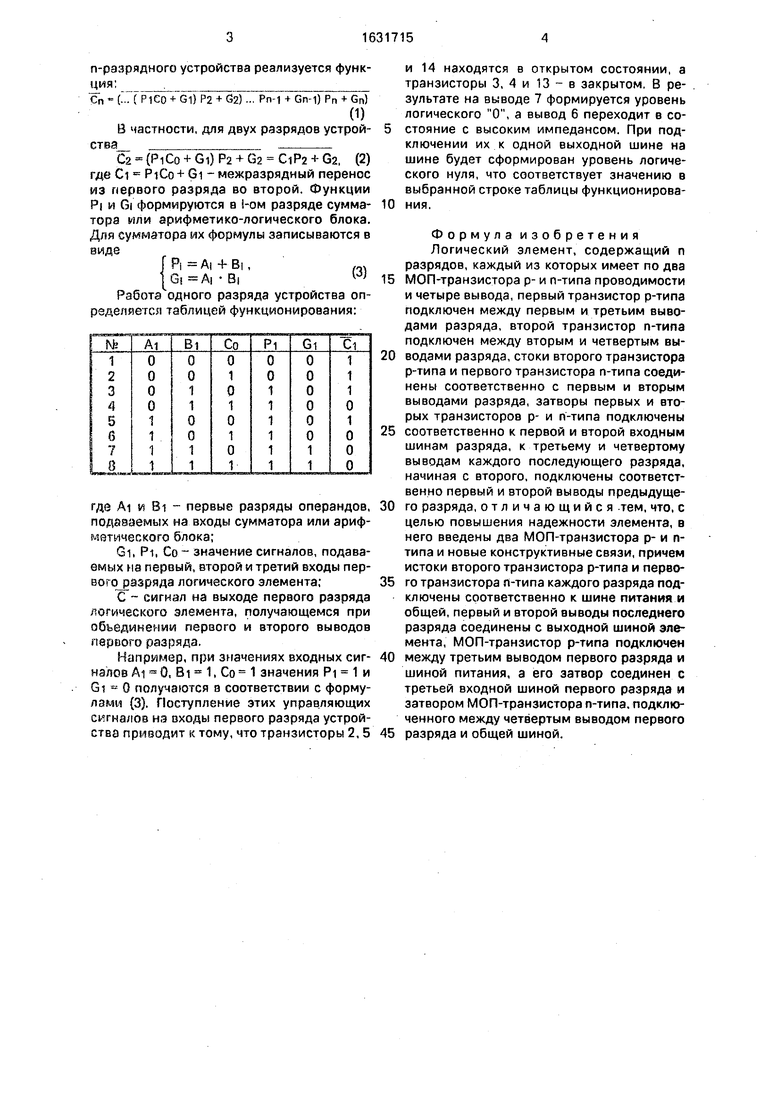

На чертеже изображена схема логического элемента.

Схема содержит п разрядов 1-1 - 1-i, i 1, ...., п, каждый из которых имеет два МОП-транзистора р-типа 2-3, два МОП- транзистора п-типа 4-5, четыре вывода 6 9 и два входа Ю-i и 11-i, i 1п, причем

первый транзистор р-типа 2 подключен между первым 6 и третьим 8 выводами разрядов, второй транзистор р-типа 3 подключен между первым выводом 6 и шиной питания Еп, первый транзистор п-типа 4 подключен между вторым выводом 7 и общей шиной, второй транзистор п-типа 5 подключен между вторым 7 и четвертым 9 выводами разряда, первый и второй выводы п-го разряда соединены с шиной выхода 12

элемента, третий и четвертый выводы (i + 1)-го разряда подключены соответственно к первому и второму выводам i-ro разряда (i 1п - 1), между третьим выводом 8

первого разряда и шиной питания Еп подключен транзистор р-типа 13, а между четвертым выводом 9 и общей шиной подключен транзистор п-типа 14, затворы транзисторов 2 и 4 соединены с первым входом Ю-i разряда, затворы транзисторов 3 и 5 соединены со вторым входом 11-1 разряда, затворы транзисторов 13 и 14 подключены к шине третьего входа 15 первого разряда.

Логический элемент работает следующим образом.

На первые входы Ю-i каждого из разрядов поступают соответственно сигналы .....Сп-функции генерации поразрядного переноса, на вторые входы 11-1 каждого из разрядов подаются соответственно сигналы PiРп - функции распространения поразрядного переноса, на вход 15 поступает сигнал входного переноса Со. На шине 12

СО

С

СЬ

со VJ ел

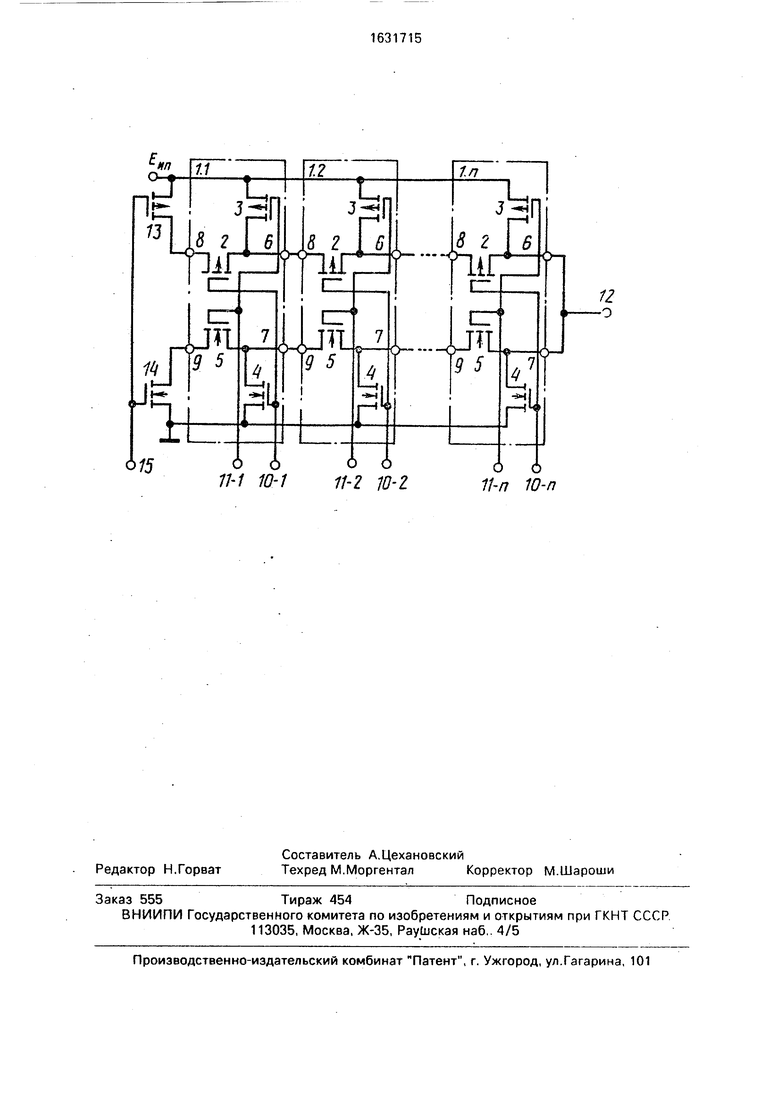

n-разрядного устройства реализуется функция: ,

Сп - (-. ( P1GO + G1) Р2 G2) ... Рп-1 + Gn-1) Рп + Gn)

(D

В частности, для двух разрядов устройства .

C2 {PiCo + Gi)P2 + G2 CiP2 + G2, (2) где Ci PiCo + 61 - межразрядный перенос из первого разряда во второй. Функции PI и GI формируются в -ом разряде сумматора или арифметико-логического блока. Для сумматора их формулы записываются в виде

Pi Ai + Bi,п

Gi A|-Biw

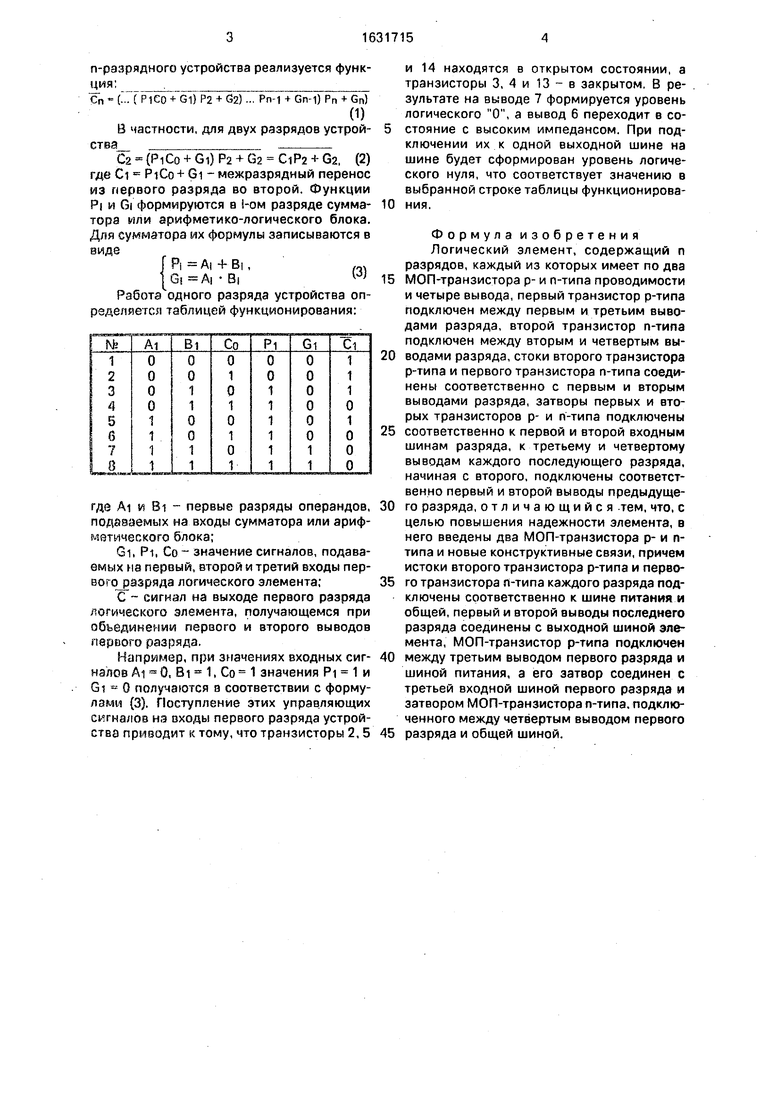

Работа одного разряда устройства оп- ределяетсл таблицей Функционирования:

где AI и 81 - первые разряды операндов, подаваемых на входы сумматора или арифметического блока;

Gi, Pi, Co значение сигналов, подаваемых на первый, второй и третий входы пер- вого азряда логического элемента;

С сигнал на выходе первого разряда логического элемента, получающемся при объединении первого и второго выводов первого разряда.

Например, при значениях входных сигналов AI 0, Bi 1, Со 1 значения PI 1 и Gi - 0 получаются в соответствии с формулами (3). Поступление этих управляющих сигналов на входы первого разряда устройства приводит к тому, что транзисторы 2, 5

и 14 находятся в открытом состоянии, а транзисторы 3, 4 и 13 - в закрытом, В результате на выводе 7 формируется уровень логического О, а вывод 6 переходит в состояние с высоким импедансом. При подключении их к одной выходной шине на шине будет сформирован уровень логического нуля, что соответствует значению в выбранной строке таблицы функционирования.

Формула изобретения Логический элемент, содержащий п разрядов, каждый из которых имеет по два

МОП-транзистора р- и n-типа проводимости и четыре вывода, первый транзистор р-типа подключен между первым и третьим выводами разряда, второй транзистор п-типа подключен между вторым и четвертым выводами разряда, стоки второго транзистора р-типа и первого транзистора n-типа соединены соответственно с первым и вторым выводами разряда, затворы первых и вторых транзисторов р- и n-типа подключены

соответственно к первой и второй входным шинам разряда, к третьему и четвертому выводам каждого последующего разряда, начиная с второго, подключены соответственно первый и второй выводы предыдущего разряда, отличающийся тем, что, с целью повышения надежности элемента, в него введены два МОП-транзистора р- и п- типа и новые конструктивные связи, причем истоки второго транзистора р-типа и первого транзистора n-типа каждого разряда подключены соответственно к шине питания и общей, первый и второй выводы последнего разряда соединены с выходной шиной элемента, МОП-транзистор р-типа подключен

между третьим выводом первого разряда и шиной питания, а его затвор соединен с третьей входной шиной первого разряда и затвором МОП-транзистора n-типа. подключенного между четвертым выводом первого

разряда и общей шиной.

О фСО

11-1 10-1 11-2 10-2

11-п Ю-п

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1987 |

|

SU1481742A1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| Блок формирования переноса | 1989 |

|

SU1679482A1 |

| Многоканальный коммутатор | 1989 |

|

SU1723667A1 |

| Блок формирования переноса сумматора | 1989 |

|

SU1718214A1 |

| ОДНОРАЗРЯДНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО КОМБИНАЦИОННОГО ТИПА ДЛЯ КОДА 8-4-2—1 | 1973 |

|

SU407309A1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ПЕРЕНОСА В СУММАТОРЕ | 2013 |

|

RU2525111C1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

Изобретение относится к области электроники и вычислительной техники и может быть использовано при проектировании сумматоров и арифметических блоков цифровых БИС на КМОП-транзисторах. Цель изобретения - повышение надежности. Устройство содержит п разрядов 1.1 -1 .п, каждый из которых имеет четыре вывода 6 - 9 и два входа 10 и 11, выходную шину 12 и третий вход 15 первого разряда. Введение МОП-транзисторов 13 и 14, а также новых конструктивных связей позволило повысить надежность. 1 ил.

| Формирователь переноса | 1984 |

|

SU1223223A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логический элемент | 1984 |

|

SU1223358A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-28—Публикация

1989-04-19—Подача