(21)4702278/24

(22)06.06.89

(46) 15.03.91. Бюл. № 10

(71)Одесский политехнический институт

(72)А.В. Дрозд, ЕЛ. Полин, К.Г. Сотова и Ю.В. Дрозд (53) 681.33(088.8)

(56) Авторское свидетельство СССР № 1193662, ют G 06 F 7/38, 1984.

Авторское свидетельство СССР № 1508206, кл. G 06 F 7/38, 1987.

(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА

(57) Изобретение относится к вычислительной технике и позволяет вычислять модуль комплексного числа в двоично- десятичной системе счисления по приближенной формуле. Цель изобретения - повышение точности вычислений. Устройство содержит первую и вторую группы сумматоров, первый, второй и третий сумматоры и коммутатор с соответствующими связями. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1987 |

|

SU1508206A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Устройство для контроля умножения чисел по модулю | 1985 |

|

SU1259269A1 |

| Устройство для подсчета количества единиц | 1990 |

|

SU1829119A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1714594A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках ЭВМ.

Цель изобретения - повышение точности вычислений.

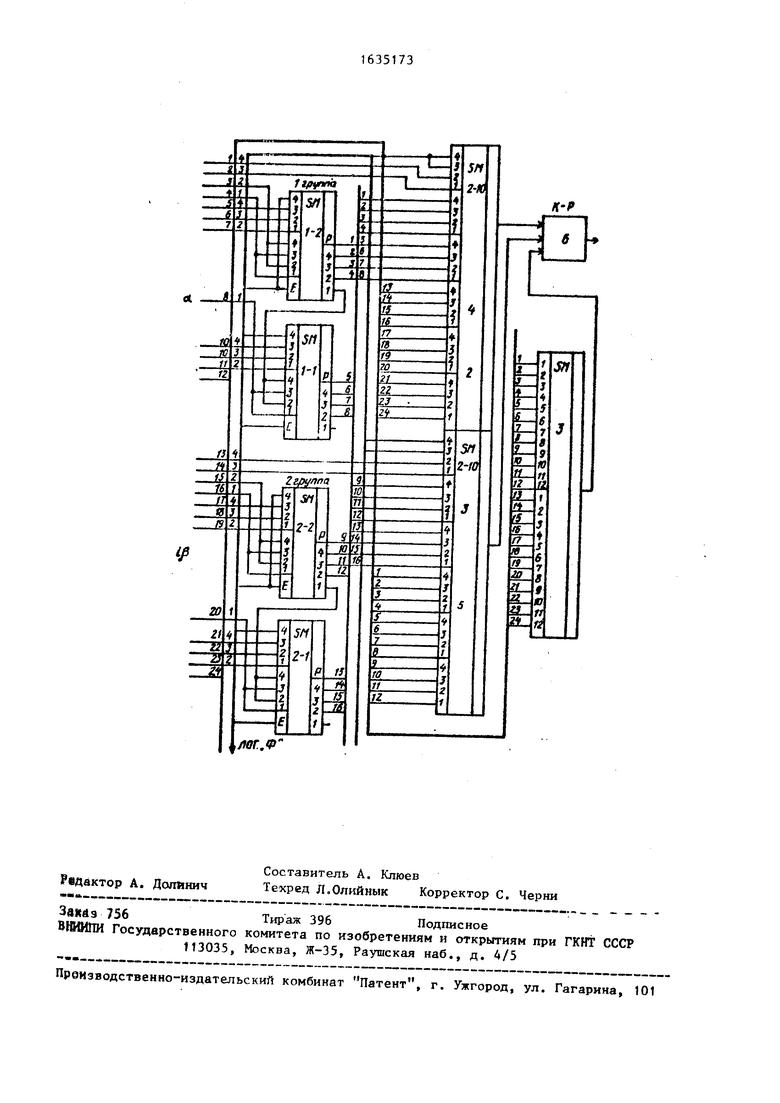

На чертеже представлена схема устройства для вычисления модуля комплексного числа для ).

Устройство содержит первый и второй сумматоры 1-1 и 1-2 первой группы, первый и второй сумматоры 2-1,. 2 второй группы, первый, второй и третий сумматоры 3-5 и коммутатор 6.

Устройство работает следующим образом.

В начальный момент времени на входах устройства установлены соответственно М-тетрадные значения в двоично- десятичном коде действительной об и мнимой /3 составляющих комплексного числа.

На входы разрядов второго слагаемого второго сумматора 4 подается 1/4 об (четверть действительной составляющей комплексного числа). Для этого на входы первого и второго разрядов М-й (старшей) тетрады входы второго слагаемого второго сумматора 4 подаются соответственно второй и первый разряды входа действительной части числа устройства. На входы разрядов К-й тетрады входа второго слагаемого второго сумматора 4 поступают соответственно разряды со второго, третьего и четвертого выходов разрядов суммы и выхода переноса К-го сумматора 1 первой группы, на входы первого, второго и третьего разрядов входа первого слагаемого К-го сумматора 1 первой группы подаются соответственно входы второго, третьего и четвертого разрядов К-й тетрады входа действи0

оо ел

bo

тельной части числа уст pi in. г на, на входы первого и i, i гы ю j нарядов входа второю слагаемою II-1-го сумматора нерпой группы подие.и.л первого ( i ь t PJзр А 1 1 ieiрады ВлОД l . , i , Ч С и , С i УСТ 01,L , , i l u т- . рШ J 1 ILinPp Г01 1 1 i-ri П i I l .М( 1 О Л I „ J ii д i Одае s т юр.) , ) р iи) .

тетрадь ди i чп, mi cm числа

crpoj cn i, входюр - т. д четверток; P jpJ A-ода , с „ iaraРМОЮ vl , lie iPJ ll O) i .u I1 Л,u,, tj i.. inт bClli, 1 (. nl,

v,u; u , PL ,

i /11

О J

I )LJML i J ;

L J.I, i jO i -. 1 1Ь Л1

Of О3 , К U I /Ю ЧОЛ v-M

i 43Ci . J J I u

л lOI

о ГьЛ , у хь- я

LI ОД( Д.Ы , (C, i

(j 5 оп1еделяе ся

v7 oia i op

3

: UliJlJbi О j1 I i Ч(П iOj (Hi

, I О

nil I i

КО U), 1

3ll V КОДОВ U i .

для JH 0 (x ,3 ;

для ЗП 1 l(6 p.

Ча вход пер t ото слагаемого с ми- тора 3 , код (X , а ьа инверс- ньй вход второго слагаемого поступает код ft .

На первый и второй информационные входы коммутатора б посгупапт соответственно резучьт1ап слоленчя М1 и М2, снимаемпе с ЕПЧОДОВ дво11-нго--дес(1 ип- ных сумматоров ч 5, II г управл чогц ч вход коммутатора 6 поступает знаковый разряд с выхода первого сумматора 3. Коммутатор 6 пропускает на выход результат сложения Ml, если , или результат сложения М2, если ЗН-0.

Таким образом, на выходе устройства определяется приближенное значение м модуля комплексного ччсаа Р по формуле

И

Г ui +i/ +(3 , cv 3

| ,3 Ч / t t/ , 0 4: fi .

j и t P i и я

,

I Mi) , i Н1ИЧИ1.11Р11ИЯ M Ду 14

io uu ii, i tpmiiL,ee ; i M,1)1 . I Jj H TCJ л «ropyio суммаюроь и KQMj юр, причсM j одп р.-зртдоь i ода i о 11 i г (Уты оп чюги чис ус рг йства f с ДкЧ L.HII (- B -o.viMi г оотьетств нп их

i J, Jii 1 чО j, Ь К pBOI О TMiatMOrO ЧШГС И lpi.1,aiOpi П, ii Ы

i зря it i HAO sa i

juiponuiia u(u cii

T i 1.111 -.,

i I pO i О „I lv l i L -v t, L l и J j чО ij il( рЬОГ 1 i ij t

Jl I J

П

ч п i ра дов

l }pt 1 j С у l

-.

4а i oi i,

II J ul

i )

ii

0

laiOpOB COL J,HHc H I С L О I 13 L. 1 L- i В til J I

первым и ьгорь м маципн ч ми ги о1 in j orm iaioi ,j, , ьр i/ n,ii

ВчОД КОЮрСЧо it i I - 1 -

НО С -ЗЫлОДОМ jUibj П С

п аьового pa j i

v4 ,Ulit U i 11 (КО i

i ода ri iv, i

c.J Ч 1C M )

i

О

5

0

5

ia MOjjuit i,Miai pa,

i I Ol L, III J i H in PJ (НИ l рОИ i J i , . li о ., tl ii,b)op iOI J 1 ,,d

r i i, 1рдг1ь i чогп лорого iaiaeMorc Г ь cv iii юра, о входами чегвер- 1 j) t JPH,J,O лО ов iiepBL x слагаемых c-s riaiopOB ju i-JiLb и второй групп, влоды второго, ipeibcro и четвертого ° разрядов k-и тетрады (k 1-m-1) входа деистBII i слььоп части числа устройства соединены COOIBCiсгвенио с вхо- rTcii;u первого, в.ирого и грен, о раз- t л J,UB ncpiuji о слагаемого k-ro

cyHMj ipl H. ip.Jill, ЧХ ЛП1 BTrpOjn, rpt ь г то и ie i i)ijpi 01 о рачрядог k-п rt тратн лода tuinnon части числа стропеiна соединены соответственно с входами первого, второго и третьего разрядов входа первого слагаемого k-ro сумматора второй группы, вход первою разряда (k-M)-u тетрады входя действительной части числа уст- pcrtfiBa соединен i Плодами первою и третьего г ч фгдов второю

гаемого k-го сумматора первой группы, вход первого разряда (k+O-й тетрады входа мнимой части числа устройства соединен с входами первого и третье- | го разрядов входа второго слагаемого k-ro сумматора второй группы, отличающееся тем, что, с целью повышения точности вычислений, вход нулевого потенциала устройства соединен с входами третьих разрядов тп-х тетрад входов второго слагаемого второго и третьего сумматоров, входы третьего и четвертого разрядов m-й тетрады входа действительной части числа устройства соединены соответственно с входами первого и второго разрядов m-й тетрады входа второго слагаемого второго сумматора, входы третьего и четвертого разрядов m-й тетрады входа мнимой части числа устройства соединены соответственно с входами первого и второго разрядов m-й тетрады входа второго слагаемого третьего сумматора, вход второго разряда m-й тетрады входа действительной части числа устройства сот единен с входами второго и четвертого разрядов входа второго слагаемого (ш-1)-го сумматора первой группы,

вход второго разряда m-й тетрады входа мнимой части числа устройства соединен с входами второго и четвертого разрядов входа второго слагаемого (ш-1)-го сумматора второй группы, входы второго и четвертого разрядов входа второго слагаемого р-го сумматора первой группы (р 1-т-2) соединены

с выходом первого разряда выхода суммы (р+1)-го сумматора первой группы, входы второго и четвертого разрядов входа второго слагаемого р-го сумматора второй группы соединены с выходом первого разряда выхода суммы

(р+1)-го сумматора второй группы, выходы второго, третьего и четвертого разрядов выхода суммы и выход переноЧ са k-ro сумматора первой группы соединены соответственно с входами с первого по четвертый разрядов k-й тетрады входа второго слагаемого второго сумматора, выходы второго, третьего и четвертого разрядов выхо-

5 да суммы и выход переноса k-ro сум- j матора второй группы соединены соответственно с входами с первого по четвертый разрядов k-й тетрады входа. второго слагаемого третьего сумматора.

Авторы

Даты

1991-03-15—Публикация

1989-06-06—Подача