СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для вычисления модуля комплексного числа | 1987 |

|

SU1508206A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1741130A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

Изобретение относится к вычислительной технике и позволяет определять количество единиц в параллельном коде в двоично-десятичной системе счисления. УСТРОЙСТВО содержит делители количества единиц на две группы 1, определяющие младшие разряды тетрад результата, и делители количества единиц на пять групп 2, вычисляющие три старших результата. 4 ил., 2 табл.

till

21

15

1$

00

ю ю

Фиг.1

Ю

Изобретение относится к вычислительной технике и может использоваться в арифметических блоках ЭВМ, работающих в двоично-десятичной системе счисления.

Цель изобретения - расширение класса решаемых задач за счет возможности получения результата в двоично-десятичной системе счисления..

Изобретение по сравнению с известными решениями содержит делители количества единиц на пять, позволяющие в совокупности с вновь введенными связями выполнить вычисление результата в двоично-десятичной системе счисления.

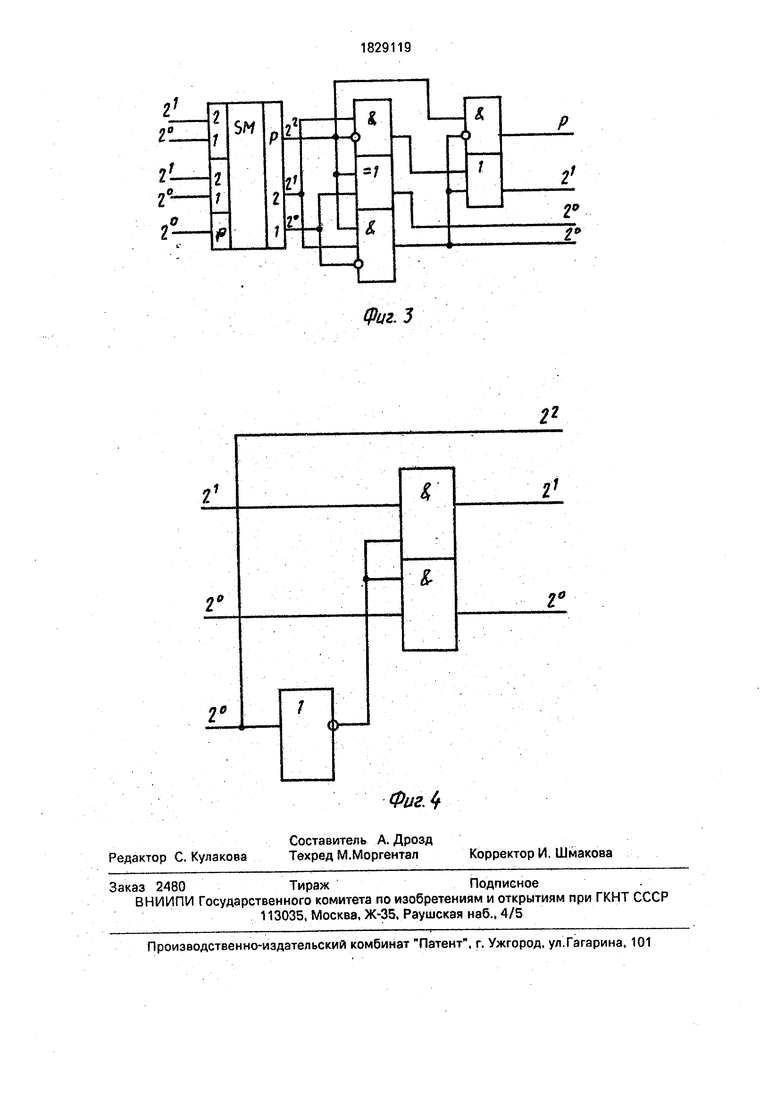

Структурная схема устройства показана на фиг/1.

Устройство содержит г одю

п + 1

блоков деления количества единиц в коде на два 1.1-1.г и блоков деления количества единиц в коде на пять 2.1-2.Г, где г- разрядность входного кода, причем входы блока 1.1 являются входами устройства, выходы частного каждого блока деления количества единиц в коде на два 1.1-1.гсоединены соответственно с входами соответствующего блока деления количества единиц в коде на пять 2.1-2.Г, выходы частного каждого, предыдущего блока деления количества единиц в коде на пять соединены с соответствующими входами последующего по номеру блока деления количества единиц в коде на два, выходы остатка соответствующих блоков деления количества единиц в коде на пять являются выходами разрядов соответствующих тетрад устройства, начиная с младшей тетрады, выход частного следнего блока деления количества единиц в коде на пять 2 является выходом первого разряда старшей (г+1)-й тетрады устройства.

Устройство работает следующим образом.

На выходы устройства поступает код, в котором необходимо определить количество единиц в двоично-десятичной системе счисления. Этот код подается на входы первого блока деления количества единиц в коде на два 1.1, который на выходах частного формирует код с количеством единиц, равным целочисленному частному от деления на два количества единиц входного кода, а на выходе остатка - остаток от указанного деления, являющийся младшим разрядом младшей тетрады искомого результата. Код, полученный на выходах частного блока 1.1 поступает на входы блока деления количества единиц в коде на пять 2.1, который на выходах частного формирует код с количеством единиц, равным целочисленному частному от деления на пять количества единиц его входного кода, а на выходах остатка - трехразрядный код остатка от указанного деления, определяющий три старших разряда младшей тетрады результата.

Код, полученный на выходах частного блока,поступает далее на входы блока деления количества единиц в коде на два 1.2, который аналогично блоку 1.1, описанному

0 выше, определяет на выходе остатка младший разряд второй тетрады результата и код на выходах частного, обрабатываемый далее в блоке деления количества единиц в коде на пять 2.2 с получением трех старших

5 разрядов второй тетрады результата на выходах остатка и кода на выходах частотного для вычисления последующих тетрад результата на последующих блоках деления количества единиц в коде на два и пять. На

0 последних делителях блоках деления коли-- чества единиц в кеде на два 1.г и пять 2.г формируются разряды последней тетрады результата (соответственно младший и три старших разряда тетрады), а также младший

5 (единственный) разряд старшей тетрады результата на выходе частного блока 2.г. В случае нулевого значения этого разряда предпоследняя тетрада оказывается старшей тетрадой результата. Полученные раз0 ряды тетрад результата с выходов остатка блоков деления количества единиц в коде на два и пять, а также с выхода частного блока 2.г поступают на выходы устройства.

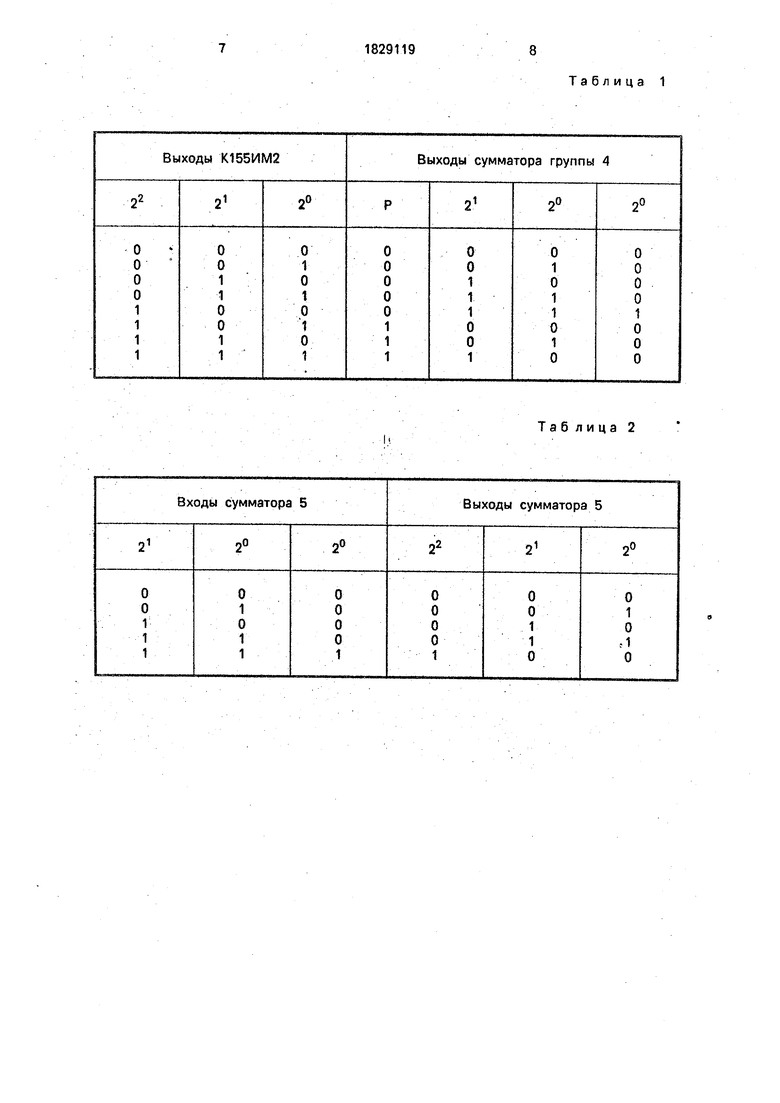

Блок деления количества единиц в коде

5 на пять показан на фиг,2 и содержит сумматоры первой группы 3, сумматоры второй группы 4 и сумматор 5, все входы суммато- . ров первой группы 3 являются входами блока, выходы суммы и переноса первого

0 сумматора 3.1 группы соединены соответственное входами первого и второго разрядов первого слагаемого первого сумматора 4,1 группы, вход переноса которого подключен к нулевой шине, первый и второй выходы

5 первого разряда и выход второго.разряда каждого предыдущего сумматора группы 4 соединены соответственно с входом переноса и входами первого и второго разрядов первого слагаемого последующего суммато0 ра группы 4, входы первого и второго разрядов второго слагаемого каждого сумматора группы 4 соединены соответственно с выходами суммы и переноса сумматора группы 3 с большим на единицу номером первый и

5 второй выходы первого разряда и выход второго разряда последнего сумматора группы 4 соединены соответственно с выходами соответствующих разрядов сумматора 5, выходы которого являются выходами ос- татка блока, а выходы переноса сумматоров

группы 4 являются выходами частного блока.

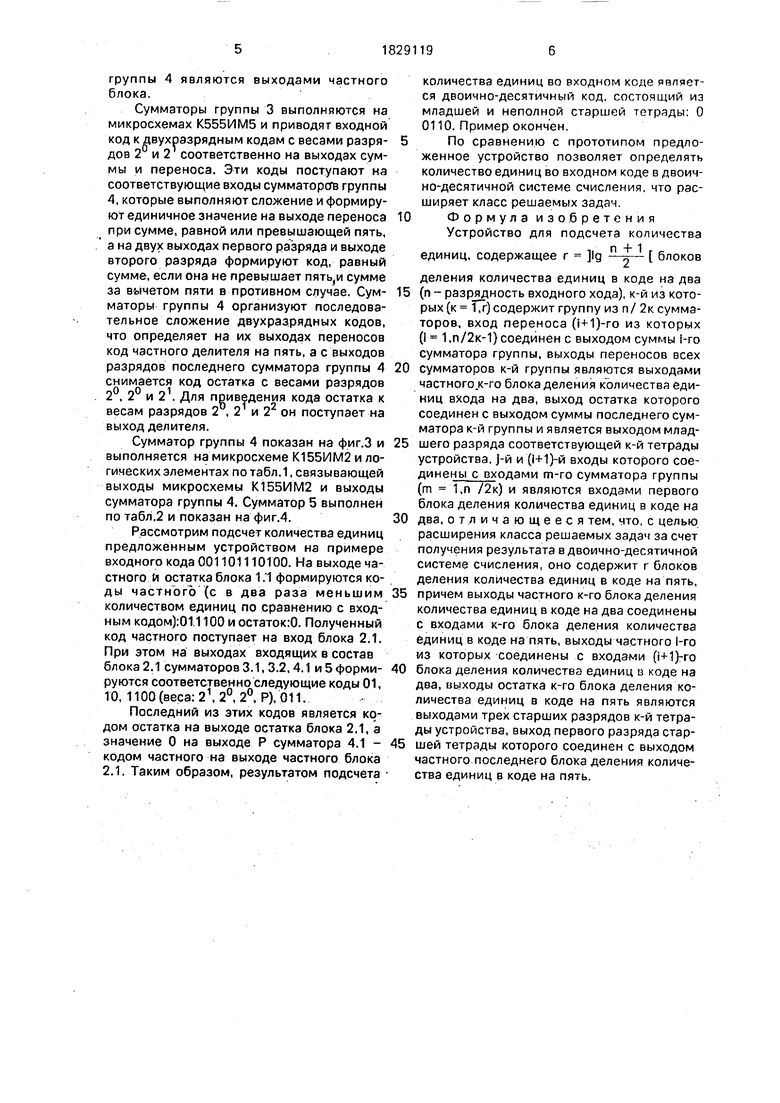

Сумматоры группы 3 выполняются на микросхемах К555ИМ5 и приводят входной код к двухразрядным кодам с весами разрядов 2 и 2 соответственно на выходах суммы и переноса. Эти коды поступают на соответствующие входы сумматорсгв группы 4, которые выполняют сложение и формируют единичное значение на выходе переноса при сумме, равной или превышающей пять, а на двух выходах первого разряда и выходе второго разряда формируют код, равный сумме, если она не превышает пять,и сумме за вычетом пяти в противном случае. Сумматоры группы 4 организуют последовательное сложение двухразрядных кодов, что определяет на их выходах переносов код частного делителя на пять, а с выходов разрядов последнего сумматора группы А снимается код остатка с весами разрядов 2°, 2° и 21. Для приведения кода остатка к весам разрядов 2,2 и 2 он поступает на выход делителя.

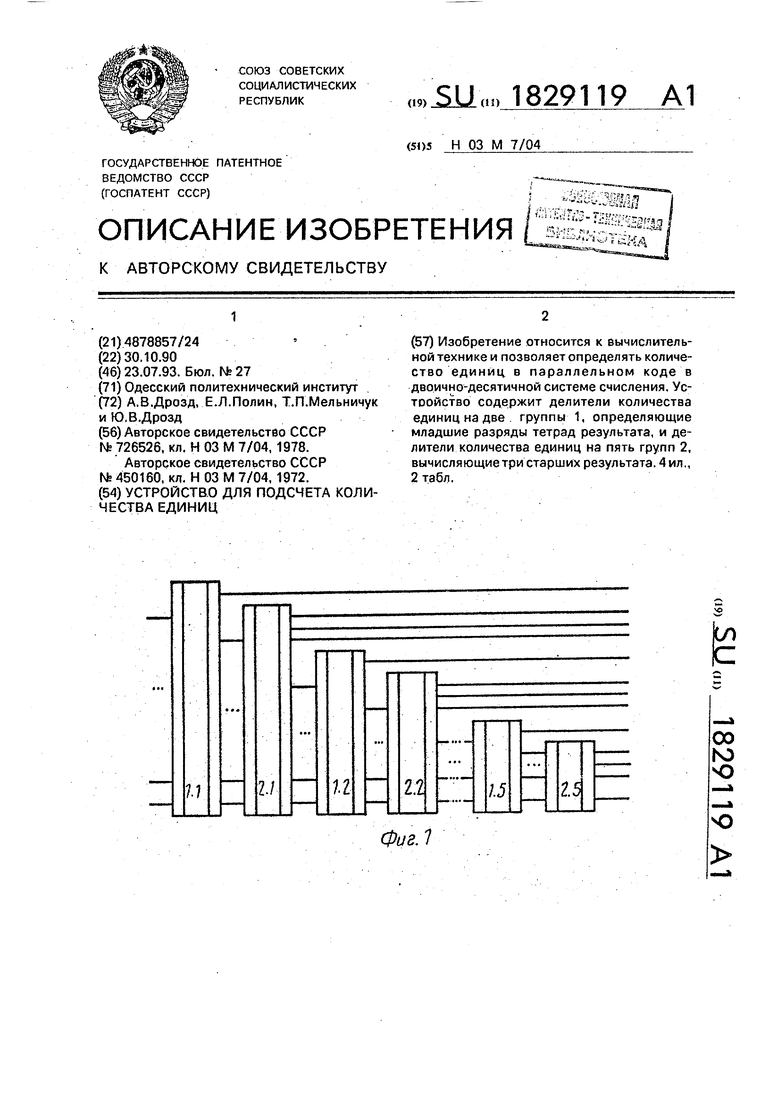

Сумматор группы 4 показан на фиг.З и выполняется на микросхеме К155ИМ2 и логических элементах по табл.1, связывающей выходы микросхемы К155ИМ2 и выходы сумматора группы 4. Сумматор 5 выполнен по табл.2 и показан на фиг.4.

Рассмотрим подсчет количества единиц предложенным устройством на примере входного кода 001101110100. На выходе частного и остатка блока 1.1 формируются коды частного (с в два раза меньшим количеством единиц по сравнению с входным кодом):01.1100 и остаток. О. Полученный код частного поступает на вход блока 2.1. При этом на выходах входящих в состав блока 2.1 сумматоров 3.1, 3.2.4.1 и 5 формируются соответственно следующие коды 01, ТО, 1100 (веса: 21, 2°, 2°, Р), 011.

Последний из этих кодов является кодом остатка на выходе остатка блока 2,1, а значение 0 на выходе Р сумматора 4.1 - кодом частного на выходе частного блока 2.1. Таким образом, результатом подсчета

количества единиц во входном коде является двоично-десятичный код, состоящий из младшей и неполной старшей тетрады: О 0110, Пример окончен.

По сравнению с прототипом предложенное устройство позволяет определять количество единиц во входном коде в двоично-десятичной системе счисления, что расширяет класс решаемых задач.

Формула изобретения Устройство для подсчета количества

единиц, содержащее г lg

блоков

деления количества единиц в коде на два

(п - разрядность входного хода), к-й из которых (к 1 ,г) содержит группу из гт/ 2к сумматоров, вход переноса (i+1)-ro из которых (I 1 ,п/2к-1) соединен с выходом суммы i-ro сумматора группы, выходы переносов всех

сумматоров к-й группы являются выходами частного.к-го блока деления количества единиц входа на два, выход остатка которого соединен с выходом суммы последнего сумматора к-й группы и является выходом младшего разряда соответствующей к-й тетрады устройства, j-й и (1+1)-й входы которого сое- динены с входами m-го сумматора группы (т 1,п /2к) и являются входами первого блока деления количества единиц в коде на

два, отличающееся тем, что, с целью расширения класса решаемых задач за счет получения результата в двоично-десятичной системе счисления, оно содержит г блоков деления количества единиц в коде на пять,

причем выходы частного к-го блока деления количества единиц в коде на два соединены с входами к-го блока деления количества единиц в коде на пять, выходы частного 1-го из которых соединены с входами (i+1)-ro

блока деления количества единиц в коде на два, выходы остатка к-го блока деления количества единиц в коде на пять являются выходами трех старших разрядов к-й тетрады устройства, выход первого разряда стзршей тетрады которого соединен с выходом частного последнего блока деления количества единиц в коде на пять.

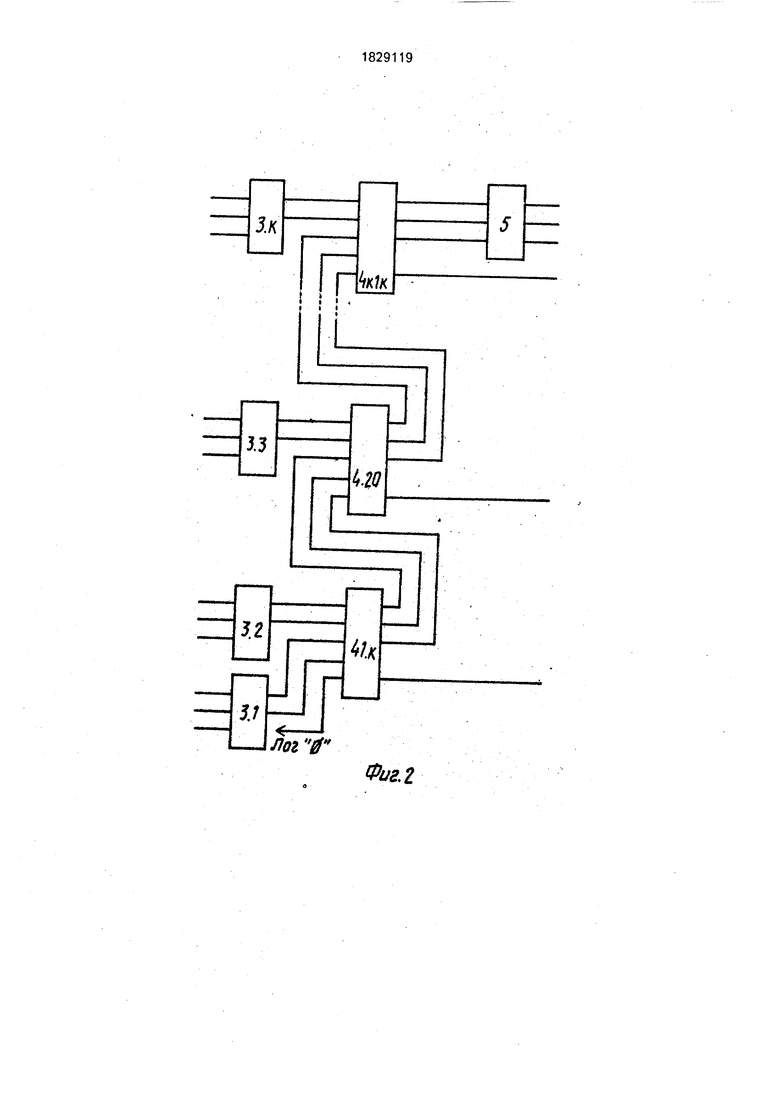

Таблица 1

Таблица 2

; i

rfe

U

Лог 0

ttff

tit

Фиг. 2

| Устройство для параллельного счета количества единиц (нулей) в двоичном числе | 1978 |

|

SU726526A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для параллельного счета количества единиц(нулей)в двоичном числе | 1972 |

|

SU450160A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-07-23—Публикация

1990-10-30—Подача