Изобретение относится к вычислительной технике и может быть использовано в системах цифровой автоматики для ускорения операций целочисленной арифметики.

Цель изобретения - повышение быстродействия при одновременном упрощении устройства.

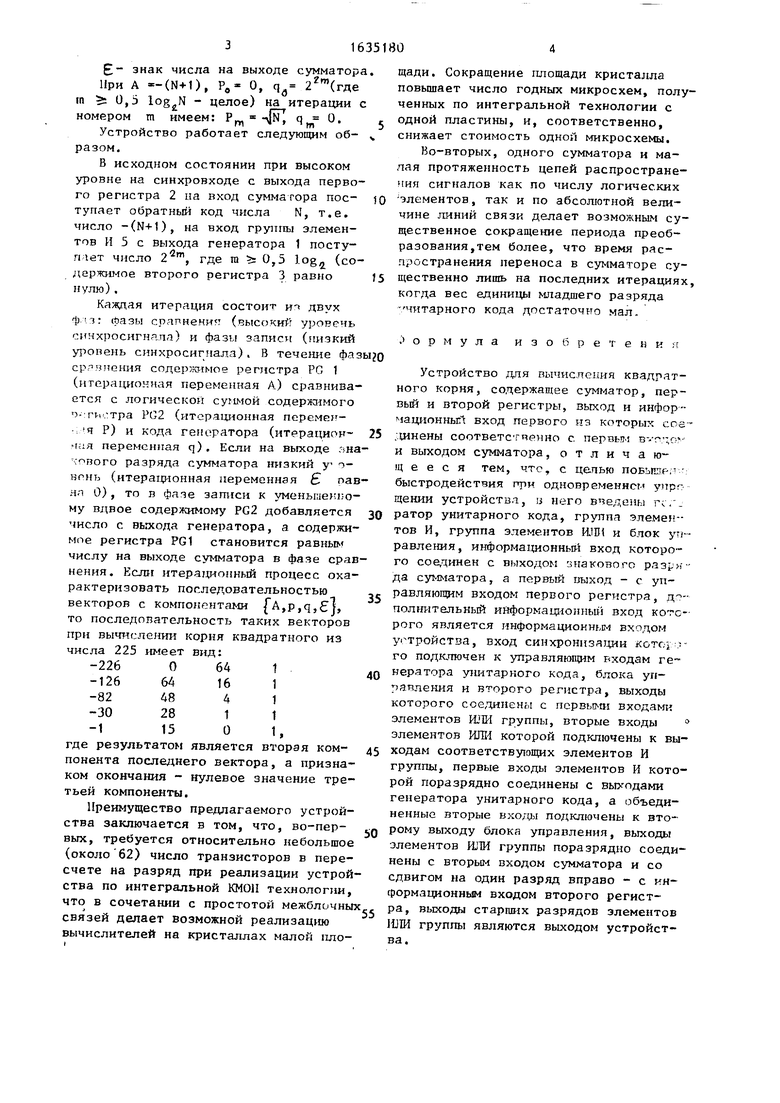

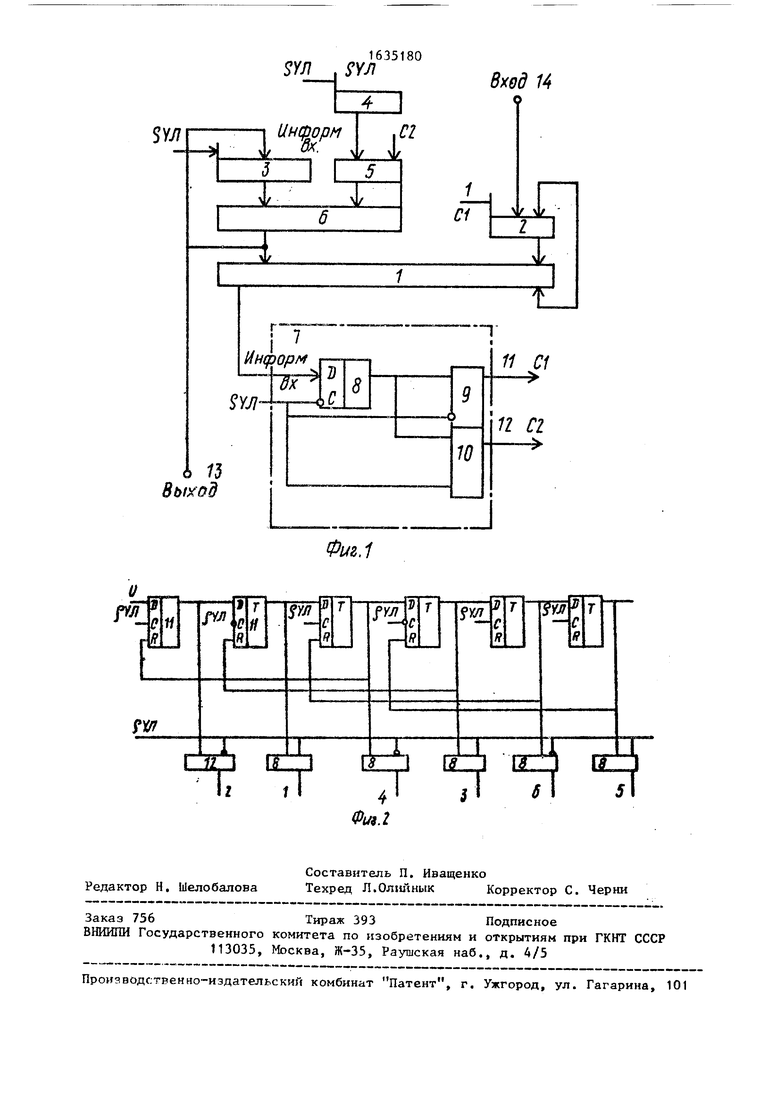

На фиг. 1 представлена структурная схема устройства; на риг. 2 - пример реализации генератора унитарного кода.

Схема содержит сумматор 1, первый 2 и второй 3 регистры, генератор 4 унитарного кода, группа элементов И 5, группа элементов ИЛИ 6, блок 7 управления, содержащий триггер 8, элементы И 9 и ИЛИ 10, триггеры 11 (фиг.2) и элементы И 12, выход 13 и вход 14. Устройство реализует алгоритм вычисления :

0 OO

сл

00

141

и

А; + е; (Р;+ ч; - Р;/2 + El q;

чи, 8

q;/ ;,., sign A;

где А - содержимое регистра 2; P - содержимое регистра 3; q - вес унитарной единицы;

Ј- знак числа на выходе сумматора

При А -(N+1), рв- 0, qfl 2ггт)(где m 2t 0,5 log N - целое) на итерации с номером m имеем: Рт Я т 0.

Устройство работает следующим об- разом.

В исходном состоянии при высоком уровне на синхровходе с выхода первого регистра 2 па вход сумматора пос- тупает обратный код числа N, т.е. число -(N+1), на вход группы элементов И 5 с выхода генератора 1 посту- п 1ет число 22т, где га 0,5 log, (содержимое второго регистра 3 равно нулю),

Каждая итерация состоит и- двух ф ч: фазы срапненич (высоки : уровень синхросигнала) и фазы записи (низкий уровень синхросигнала). В течение фаз сравнения содержимое регистра PG 1 (итерационная переменная А) сравнивается с логической суммой содержимого о-ть -тра PG2 (итерационная перемен- ч Р) и кода генератора (итерацион- гал переменная q). Если на выходе разряда сумматора низкий у1 о- нгнь (итерационная переменная Ј пав нл 0), то в фазе записи к уменьгаешю- му вдвое содержимому PG2 добавляется число с ВЫХОДА генератора, а содержимое регистра PG1 становится равным числу на выходе сумматора в фазе сравнения. Если итерационный процесс охарактеризовать последовательностью векторов с компонентами ,p,q,Јj, то последовательность таких векторов при вычислении корня квадратного из числа 225 имеет вид:

-226 0 64 1

-126 64 16 1

-82 48 4 1

-30 28 1 1

-1 15 О 1, где результатом является вторая ком- понента последнего вектора, а признаком окончания - нулевое значение третьей компоненты.

Преимущество предлагаемого устройства заключается в том, что, во-пер- вых, требуется относительно небольшое (около 62) число транзисторов в пересчете на разряд при реализации устройства по интегральной КМОН технологии, что в сочетании с простотой межблочных связей делает возможной реализацию вычислителей на кристаллах малой пло

,

Q 5

до 5 0

Д5

п

5

0

5

щади. Сокращение площади кристалла повышает число годных микросхем, полученных по интегральной технологии с одной пластины, и, соответственно, снижает стоимость одной микросхемы.

Во-вторых, одного сумматора и малая протяженность цепей распространения сигналов как по числу логических элементов, так и по абсолютной величине линий связи делает возможным существенное сокращение периода преобразования,тем более, что время распространения переноса в сумматоре существенно лишь на последних итерациях, когда вес единицы младшего разряда читарного кода достаточно мал,

Формула изобретение

Устройство для вычисления квадратного корня, содержащее сумматор, первый и второй регистры, выход и информационный вход первого цз которых era - ;данены соответственно с первым в---р ;о и выходом сумматора, отличающееся тем, что, с цепью ПОБЪПЗГ-. быстродействия при одновременном упрг щении устройства, ц него введены гсг. ратор унитарного кода, группа элементов И, группа элементов ИЛИ и блок управления , информационный вход которого соединен с выходом знакового разряда, сумматора, а первый выход - с управляющим входом первого регистра, полнительный информационный вход которого является информационным входом устройства, вход синхронизации котс ; го подключен к управляющим входам генератора унитарного кода, блока уп- рявления и второго регистра, выходы которого соединены с первыми входами элементов ИЛИ группы, вторые входы ° элементов ИЛИ которой подключены к выходам соответствующих элементов И группы, первые входы элементов И которой поразрядно соединены с выходами генератора унитарного кода, а объединенные вторые входы подключены к второму выходу блока управления, выходы элементов ИЛИ группы поразрядно соединены с вторым входом сумматора и со сдвигом на один разряд вправо - с информационным входом второго регистра, выходы старших разрядов элементов ИЛИ группы являются выходом устройства.

5УЛ

5Ј

Цнформ 6x.

j a

,#

i C1

V W

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1988 |

|

SU1575177A1 |

| Устройство для вычисления функций @ @ @ @ и @ @ @ @ | 1990 |

|

SU1732342A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1179328A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1254477A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для вычисления синусно- косинусных функций | 1978 |

|

SU750495A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой автоматики. Целью изобретения является повышение быстродействия устройства при одновременном упрощении. Для этого в устройство, содержащее сумматор, два регистра, блок управления, введены генератор унитарного кода, группа элементов И и группа элементов ИЛИ. Группа элементов ИЛИ выполняет функцию сложения, так как в рассматриваемом алгоритме ненулевым разрядам унитарного кода соответствуют нулевые разряды содержимого второго регистра. Группа элементов И осуществляют маскирование ненулевых разрядов унитарного кода при низком уровне на соответствующем выходе устройства управления. 2 ил. а Ј /

t

Ишрорм

SYJIffx

D

15 Выход

Фиг.1

/

8

// Г/

/

/z rz

-

.J

| Устройство для извлечения квадратного корня | 1982 |

|

SU1084788A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Оранский A.M | |||

| Аппаратные методы в цифровой вычислительной технике | |||

| г | |||

| Минск, 1977, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-15—Публикация

1988-11-27—Подача