1

(21)4697163/24

(22)29.05.89

(46) 15.03.91. Бюл. № 10 (72) В.В.Баранов, А.Л.Кузьмин, В.В.Маринчук, П.Б.Поплевин, С.А.Тро- шин и П.Ю.Чекмазов

(53)681.327.66 (088.8)

(56)IEEE Journal of Solid-State Circuits, 1983, V. SC-18, 5, c. 544- 549.

IEEE Journal of Solid-State Circuits, 1988, V. SC-23, № 5, с. 1085- 1094.

(54)УЗЕЛ ПАМЯТИ

(57)Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств в интегральном исполнении с резервированием и расширенными функциональными возможностями на КМДП- транзисторах. Целью изобретения является упрощение узла памяти. Поставленная цель достигается тем, что узел памяти содержит два элемента ИЛИ-НЕ 5,6с соответствующими связями. При этом мультиплексор 1 служит для пропускания на выход 11 адреса либо с элемента 2 постоянного хранения информации, либо с элемента 3 предварительного хранения информации. Управление занесением информации в элементы 2, 3 производится с помощью элементов ИЛИ-НЕ 5, 6. 1 ил.

I

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок и резервированием | 1989 |

|

SU1709397A1 |

| Элемент памяти | 1989 |

|

SU1635214A1 |

| Элемент памяти | 1990 |

|

SU1737514A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Оперативное запоминающее устройство с резервированием строк | 1986 |

|

SU1462426A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель на кмдп-транзисторах | 1979 |

|

SU862236A1 |

| Адресный формирователь | 1988 |

|

SU1596388A1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств в интегральном исполнении с резервированием и расширенными функциональными возможностями на КМДП-транзисторах.

Цель изобретения - упрощение узла памяти.

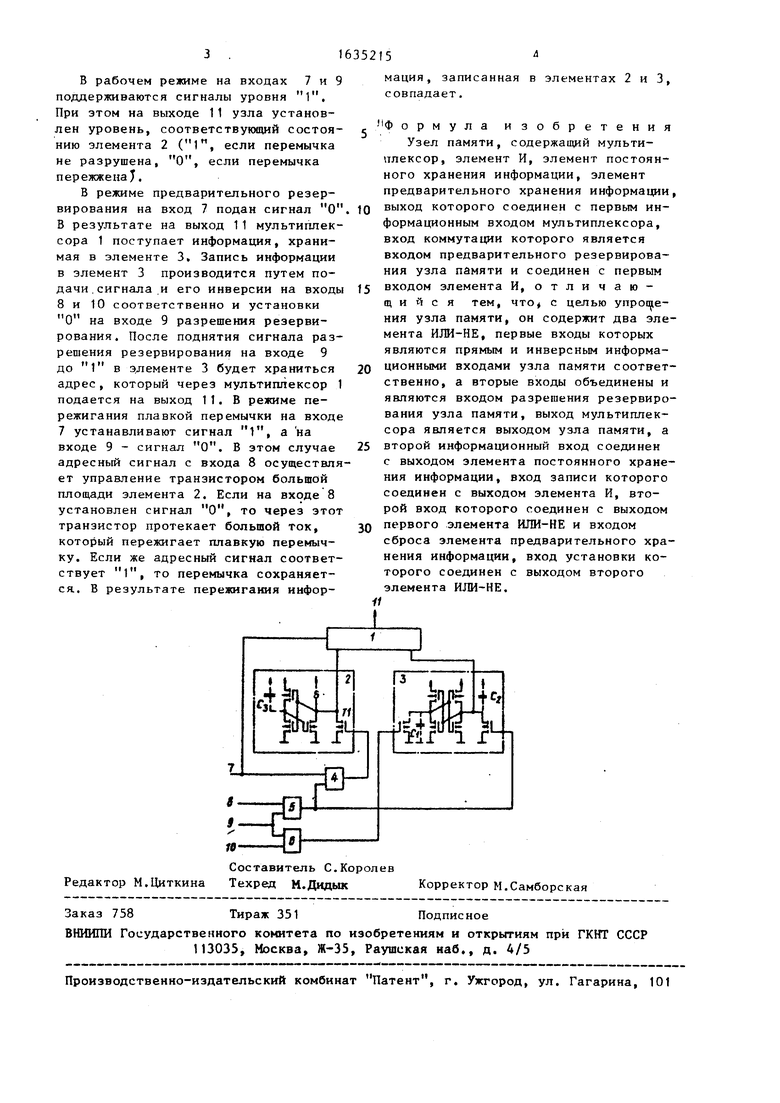

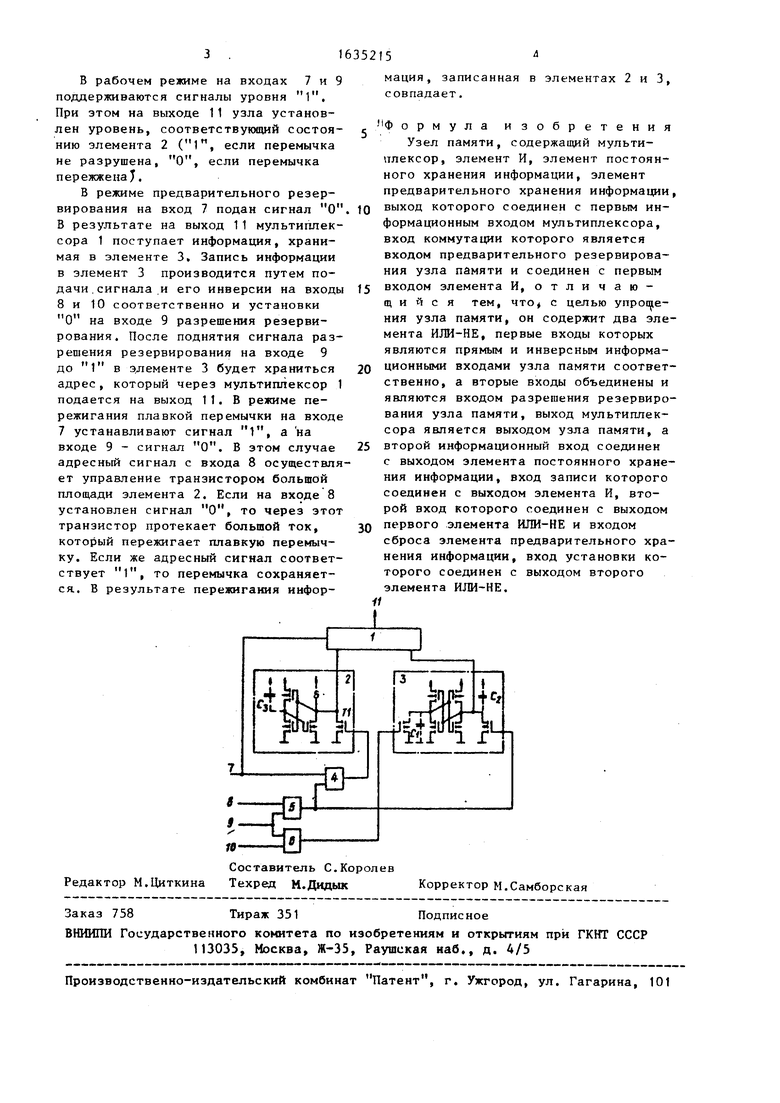

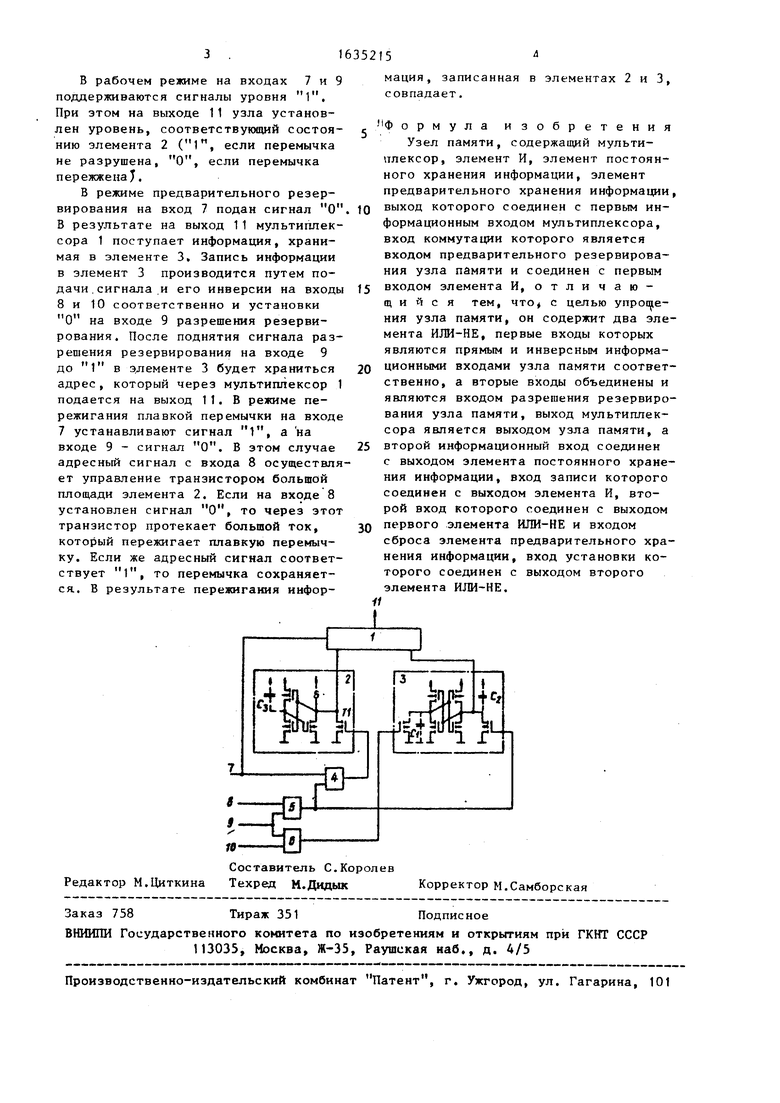

На чертеже представлена принципиальная схема узла памяти.

Узел памяти содержит мультиплексор 1, элемент 2 постоянного хранения информации, элемент 3 предварительного хранения информации, элемент И 4, два элемента ИЛИ-НЕ 5, 6, вход 7 предварительного резервирования, прямой информационный вход 8,

вход 9 разрешения резервирования, инверсный информационный вход 10, выход 1 1.

Для удобства в некоторых случаях мультиплексор 1 может использовать два дополнительных входа, на которые подаются инверсные сигналы с противоположных плечей элементов 2 и 3. Для установления соответствия начального состояния элемента 3 начальному состоянию элемента 2 можно либо использовать конденсаторы C и С, либо использовать разные топологические размеры транзисторов, образующих элемент 3.

Узел памяти работает следующим образом.

В рабочем режиме на входах 7 и 9 поддерживаются сигналы уровня 1, При этом на выходе 11 узла установлен уровень, соответствующий состоянию элемента 2 (1, если перемычка не разрушена, О, если перемычка пережжена Т.

В режиме предварительного резервирования на вход 7 подан сигнал О В результате на выход 11 мультиплексора 1 поступает информация, хранимая в элементе 3, Запись информации в элемент 3 производится путем подачи , сигнала и его инверсии на входы 8 и 10 соответственно и установки О на входе 9 разрешения резервирования. После поднятия сигнала разрешения резервирования на входе 9 до 1 в элементе 3 будет храниться адрес, который через мультиплексор 1 подается на выход 11. В режиме пережигания плавкой перемычки на входе 7 устанавливают сигнал 1, а на входе 9 - сигнал О. В этом случае адресный сигнал с входа 8 осуществляет управление транзистором большой площади элемента 2. Если на входе 8 установлен сигнал О, то через этот транзистор протекает большой ток, который пережигает плавкую перемычку. Если же адресный сигнал соответII 4 II

ствует

то перемычка сохраняется. В результате пережигания инфор/9

мация, записанная совпадает.

в элементах 2 и 3,

изобретения 1, содержащий мульти

5

0

5

0

Формула

Узел памяти, плексор, элемент И, элемент постоянного хранения информации, элемент предварительного хранения информации, выход которого соединен с первым информационным входом мультиплексора, вход коммутации которого является входом предварительного резервирования узла памяти и соединен с первым входом элемента И, отличающийся тем, что с целью упрощения узла памяти, он содержит два элемента ИЛИ-НЕ, первые входы которых являются прямым и инверсным информационными входами узла памяти соответственно, а вторые входы объединены и являются входом разрешения резервирования узла памяти, выход мультиплексора является выходом узла памяти, а второй информационный вход соединен с выходом элемента постоянного хранения информации, вход записи которого соединен с выходом элемента И, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ и входом сброса элемента предварительного хранения информации, вход установки которого соединен с выходом второго элемента ИЛИ-НЕ.

Авторы

Даты

1991-03-15—Публикация

1989-05-29—Подача