Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении.

Цель изобретения - повышение надежности устройства.

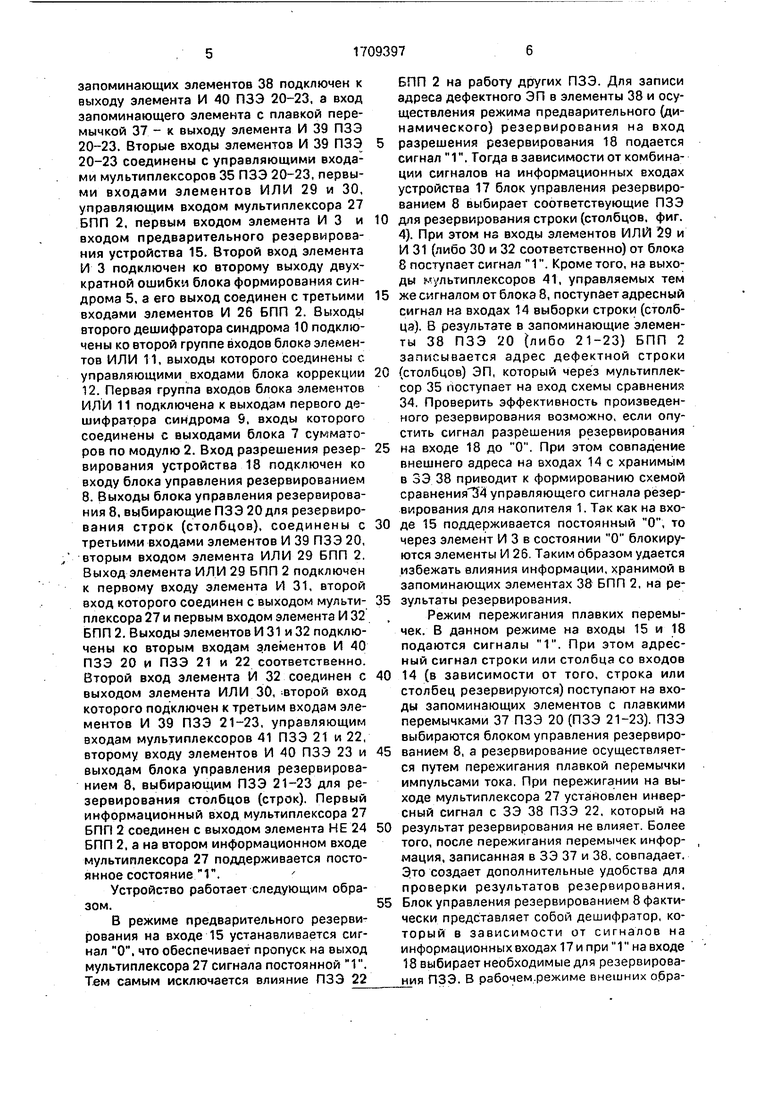

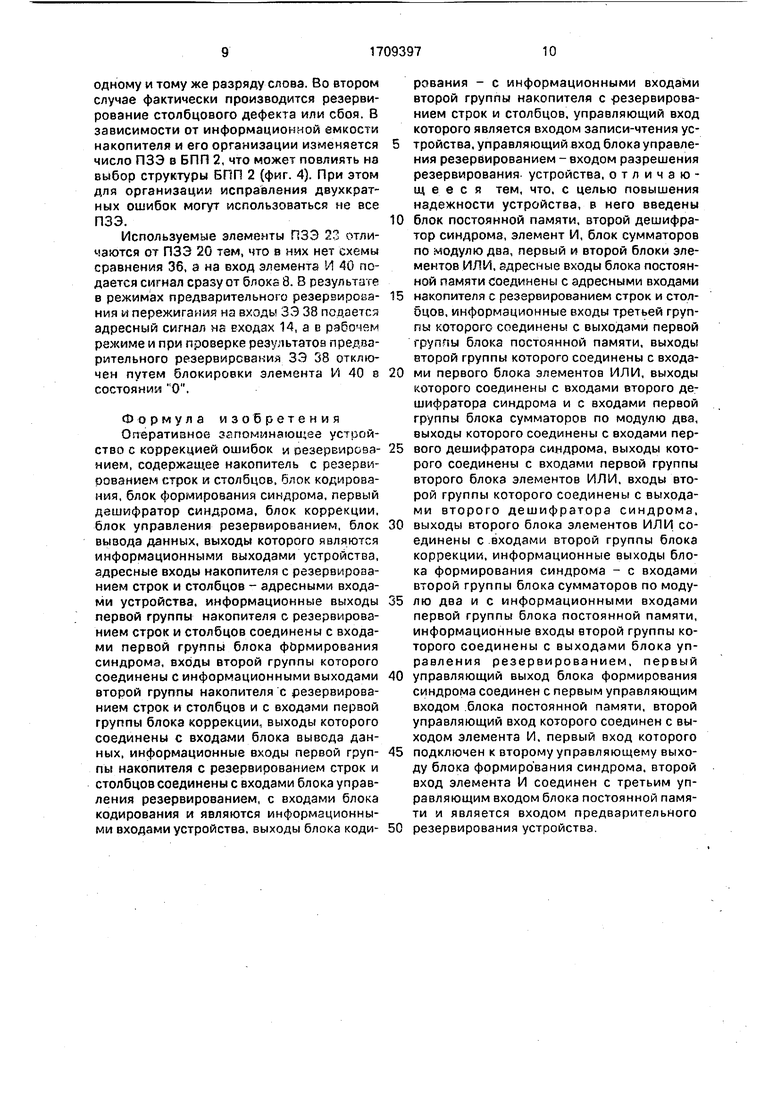

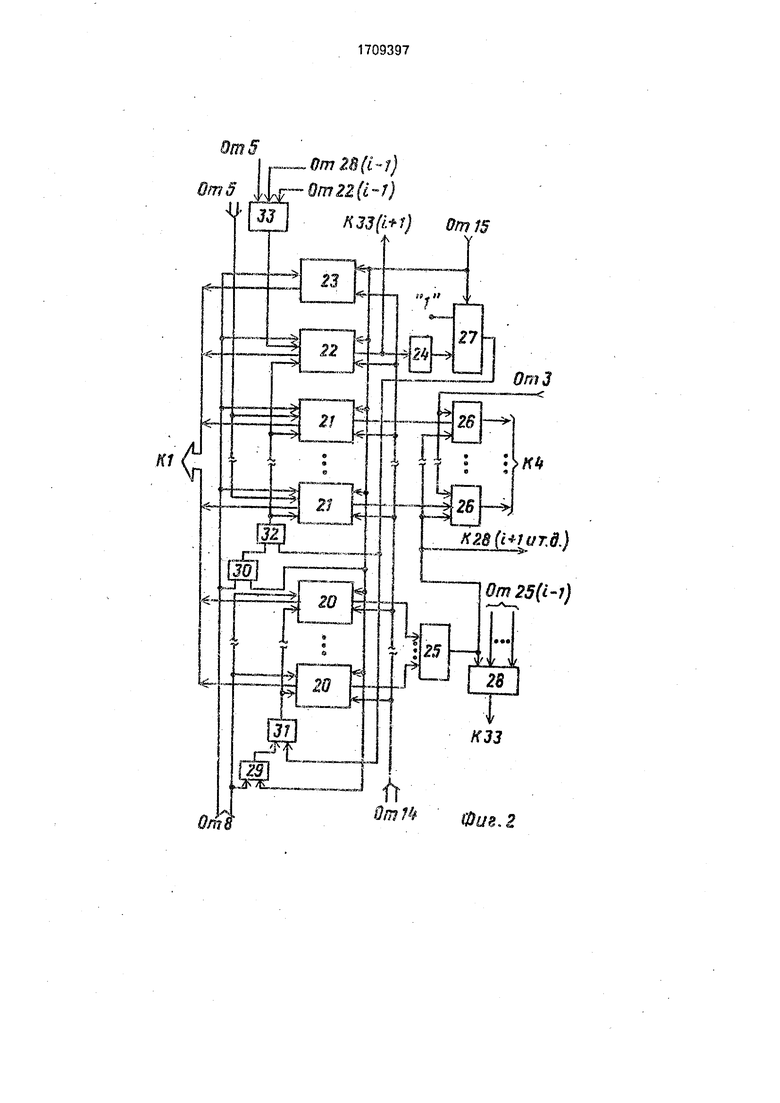

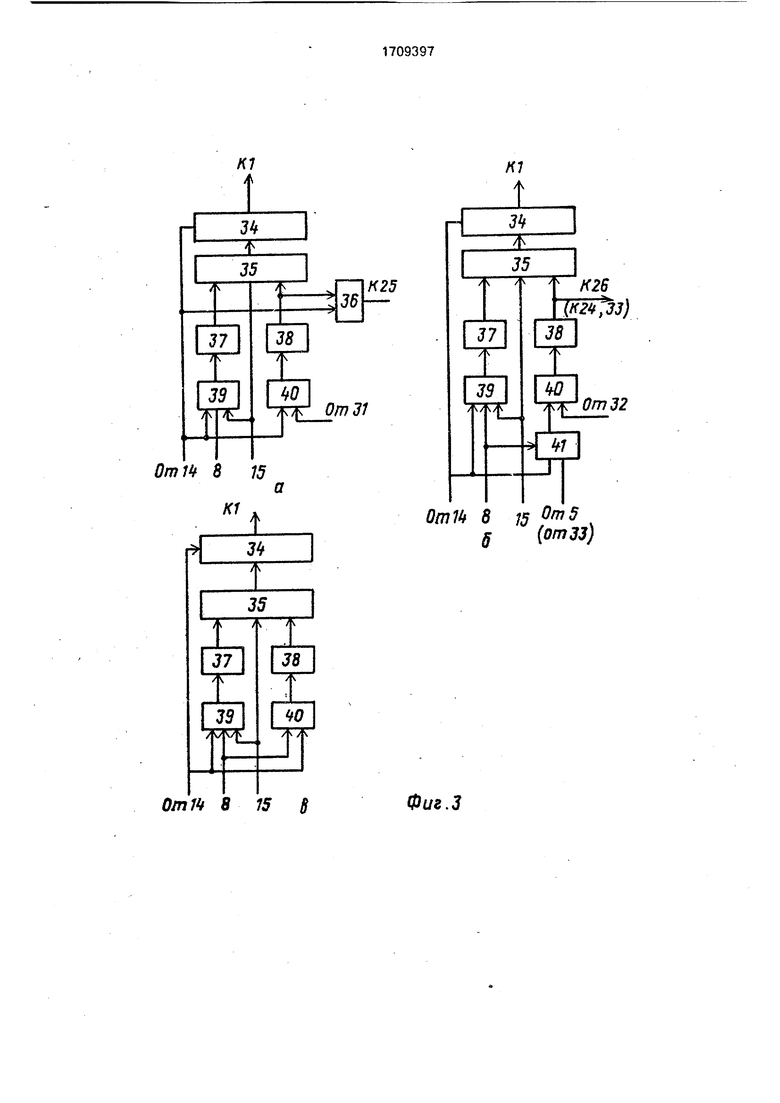

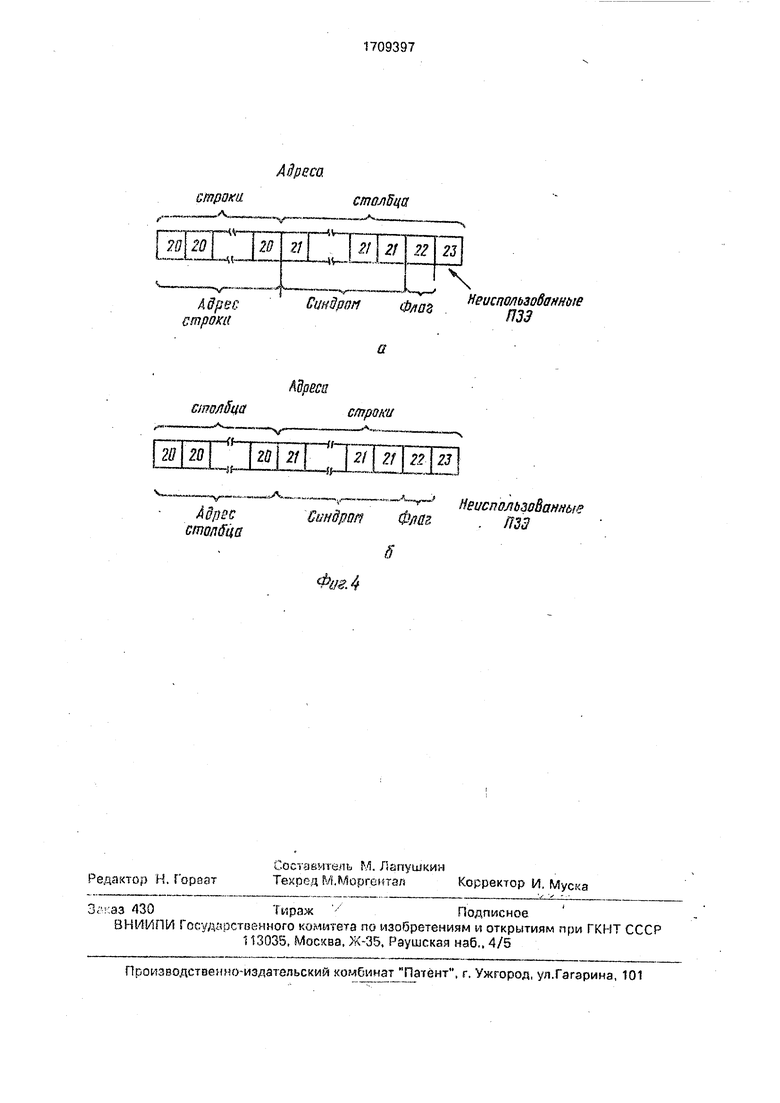

На фиг. 1 приведена структурная схема устройства; на фиг. 2-3 структурные схемы постоянного пррграммируемого накопителя и постоянных запоминающих элементов ПЗЗ. образующих БПП; на фиг, 4 схема местонахождения слов в строке и столбце.

Устройство содержит накопитель 1 с резервированием строк и столбцов, блок постоянной памяти 2 (БПП). элемент И 3, первый блок элемеитов ИЛИ 4, блок формирования синдрома 5, блок кодирования 6, блок 7 сумматоров по модулю 2, блок управления резервированием 8, первый 9 и второй 10 дешифраторы синдрома, второй блок элементов ИЛИ 11, блок коррекции 12, блок вывода данных 13. На фиг. 1 также обозначены адресные 14, вход предварительного резервирования 15, вход записи/считывания 16, информационные входы 17, вход разрешения резервирования 18 it выходы 19 уг.тройстоа.

БПП (фиг. 2) содержит ПЗЭ 20-23, элемент НЕ 24, элементы И 25, 26, мультиплексор 27, элемент ИЛИ-НЕ 28, элементы ИЛИ 29 и 30, элементы И 31-33. ПЗЭ 20-23 (фиг. За) состоит из схемы сравнения 34, мультиплексора 35, схемы сравнения 36, запоминающего элемента с плавкой перемычкой 37, запоминающего элемента 38, элементов И 39 и 40, ПЗЭ 21 включает мультиплексор 41.

Адресные входы устройства 14 соединены с адресными входами накопителя 1, первыми входами схем сравнения 34 и 36, первыми входами элементов И 39 и 40 ПЗЭ

20БПП 2, с первыми входами схем сравнения 34. элементов И 39 и первым информационным входом мультиплексора 41 ПЗЭ

21и 22 БПП, а также с входами схем сравнения 34, элементов И 39 и 40 ПЗЭ 23 БПП 2. Первая группа выходов накопителя 1 подключена к первой группе входов блока формирования синдрома 5, вторая группа входов которой соединена со второй группой выходов накопителя 1 и группой информационных входов блока коррекции и., Выходы блока коррекции 12 подключены ко входам схемы вывода данных 13, вы/оды которой являются информационными выходами устройства 19. Информационные входы устройства 17 соединены с группой входов блока управления резервированием 8, с первой группой входов накопителя 1 и группой входов блока кодирования б, выходы последнего подключены ко второй группе входов накопителя 1. Управляющий вход накопителя 1 соединен с входом записи/считывания устройства 16. Третья группа входов накопителя 1 подключена к выходам схем сравнения 34 ПЗЭ 2023 БПП 2. Второй информационный вход

0 мультиплексора 41 ПЗЭ 22 первой строки БПП 2 соединен с первым выходом однократной ошибки блока формирования синдрома 5, а мультиплексоров 41 ПЗЭ 22 остальных строк БПП 2 с выходом соответ5 ствующих элементов И 33, первый вход которых соединен с выходом однократной, ошибки блока формирования синдрома 5. Второе входы элементов И 33 соединены с выходом запоминающих элементов 38 и

0 первым информационным входом мультиплексора 35 ПЗЭ 22 предыдущей строки, Третий вход элемента И 33 соединен с выходом элемента ИЛИ-НЕ 28 предыдущей строки. Строка ПЗЭ БПП образуется ПЗЭ

5 20, отвечающих за резервирования строки (столбца) и ПЗЭ 21-23, используемых для резервирования столбца (строки). Выходы блока формирования синдрома 5 соединены со вторыми информационными входами мультиплексора 41 ПЗЭ21 БПП 2 и первой группой входов блока 7 сумматоров по модулю 2. Вторая группа входов блока 7 сумматоров по модулю 2 подключена ко входам второго дешифратора синдрома 10 и выходам блока элементов ИЛИ 4. Входы блока элементов ИЛИ 4 соединены с выходами элементов И 26 БПП 2, первые входы которых подключены к выходам запоминающих элементов 38 и первым ин0 формацмонным входам мультиплексоров 35 ПЗЭ 21 БПП 2, Вторые входы элементов И 26 соединены с выходом элемента И 25 и первым входом элемента ИЛИ-НЕ 28 БПП 2. Остальные входы элемента ИЛИ5 НЕ 28 1-ой строки соединены с (1-1) выходами элементов И 25 предыдущих (1-1) строк БПП 2. Входы элемента И 25 подключены к выходам схем сравнения 36 ПЗЭ 20 БПП 2, вторые входы которых соединены с

0 выходами запоминающих элементов 38 и первым входом мультиплексора 35 ПЗЭ 20. Выходы мультиплексоров 35 подключены ко вторым входам схемы сравнения 34 ПЗЭ 20-23. Первый информационный

55 вход мультиплексора 35 ПЗЭ 23 соединен С выходом запоминающего элемента 38 ПЗЭ 23 БПП 2, а вторые информационные входы мультиплексоров 35 соединены с выходами запоминающих элементов с плавкой перемычкой 37 ПЗЭ 20-23. Вход

запоминающих элементов 38 подключен к выходу элемента И 40 ПЗЭ 20-23. а вход запоминающего элемента с плавкой перемычкой 37 - к выходу элемента И 39 ПЗЭ 20-23. Вторые входы элементов И 39 ПЗЭ 20-23 соединены с управляющими входами мультиплексоров 35 ПЗЭ 20-23, первыми входами элементов ИЛИ 29 и 30, управляющим входом мультиплексора 27 БПП 2, первым входом элемента И 3 и входом предварительного резервирования устройства 15. Второй вход элемента И 3 подключен ко второму выходу двухкратной ошибки блока формирования синдрома 5, а его выход соединен с третьими входами элементов И 26 БПП 2. Выходы второго дешифратора синдрома 10 подключены ко второй группе входов блока элементов ИЛИ 11, выходы которого соединены с управляющими входами блока коррекции 12. Первая группа входов блока элементов ИЛИ 11 подключена к выходам первого дешифратора синдрома 9, входы которого соединены с выходами блока 7 сумматоров по модулю 2. Вход разрешения резервирования устройства 18 подключен ко входу блока управления резервированием 8. Выходы блока управления резервирования 8, выбирающие ПЗЭ 20 для резервирования стрЬк (столбцов), соединены с третьими входами элементов И 39 ПЗЭ 20, вторым входом элемента ИЛИ 29 БПП 2. Выход элемента ИЛИ 29 БПП 2 подключен к первому входу элемента И 31, второй вход которого соединен с выходом мультиплексора 27 и первым входом элемента И 32 БПП 2. Выходы элементов И 31 и 32 подключены ко вторым входам элементов И 40 ПЗЭ 20 и ПЗЭ 21 и 22 соответственно. Второй вход элемента И 32 соединен с выходом элемента ИЛИ 30, -второй вход которого подключен к третьим входам элементов И 39 ПЗЭ 21-23, управляющим входам мультиплексоров 41 ПЗЭ 21 и 22, второму входу элементов И 40 ПЗЭ 23 и выходам блока управления резервированием 8, выбирающим ПЗЭ 21-23 для резервирования столбцов (строк). Первый информационный вход мультиплексора 27 БПП 2 соединен с выходом элемента НЕ 24 БПП 2, а на втором информационном входе мультиплексора 27 поддерживается постоянное состояние 1.

Устройство работает следующим образом.

В режиме предварительного резервирования на входе 15 устанавливается сигнал О, что обеспечивает пропуск на выход мультиплексора 27 сигнала постоянной 1. Тем самым исключается влияние ПЗЭ 22

БПП 2 на работу других ПЗЭ. Для записи адреса дефектного ЭП в элементы 38 и осуществления режима предварительного (динамического) резервирования на вход разрешения резервирования 18 подается сигнал 1. Тогда в зависимости от комбинации сигналов на информационных входах устройства 17 блок управления резервированием 8 выбирает соответствующие ПЗЭ

0 для резервирования строки (столбцов, фиг. 4). При этом на входы элементов ИЛИ 29 и И 31 (либо 30 и 32 соответственно) от блока 8 поступает сигнал 1. Кроме того, на выходы мультиплексоров 41, управляемых тем

5 же сигналом от блока 8, поступает адресный сигнал на входах 14 выборки строки (столбца). В результате в запоминающие элементы 38 ПЗЭ 20 {либо 21-23) БПП 2 записывается адрес дефектной строки

0 (столбцов) ЭП, который через мультиплексор 35 поступает на вход схемы сравнения 34. Проверить эффективность произведенного резервирования возможно, если опустить сигнал разрешения резервирования

5 на входе 18 до О, При этом совпадение внешнего адреса на входах 14 с хранимь1М в ЗЭ 38 приводит к формированию схемой сравнения34 управляющего сигнала резервирования для накопителя 1. Так как на входе 15 поддерживается постоянный О, то через элемент И 3 в состоянии О блокируются элементы И 26. Таким образом удается избежать влияния информации, хранимой в запоминающих элементах 38 БПП 2, на ре5 зультаты резервирования.

Режим пережигания плавких перемычек. В данном режиме на входы 15 и 18 подаются сигналы 1. При этом адресный сигнал строки или столбца со входов

0 14 (в зависимости от того, строка или столбец резервируются) поступают на входы запоминающих элементов с плавкими перемычками 37 ПЗЭ 20 (ПЗЭ 21-23). ПЗЭ выбираются блоком управления резервированием 8, а резервирование осуществляется путем пережигания плавкой перемычки импульсами тока, При пережигании на выходе мультиплексора 27 установлен инверсный сигнал с ЗЭ 38 ПЗЭ 22, который на

0 результат резервирования не влияет. Более того, после пережигания перемычек информация, записанная в ЗЭ 37 и 38, совпадает. Это создает дополнительные удобства для проверки результатов резервирования,

5 Блок управления резервированием 8 фактически представляет собой дешифратор, который в зависимости от сигналов на информационных входах 17и при 1 на входе 18 выбирает необходимые для резервирования ПЗЭ. В рабочем.режиме внешних о.бращений на входе 15 поддерживается сигнал 1, а на входе 18 - О. Кроме того, при включении питания запоминающие элементы 38 ПЗЭ 20-22 БПП 2 устанавливаются а состояние О (в предлагаемой схеме достаточно начальной установки о О ЗЭ 38 ПЗЭ 22, схемы начальной установки не показаны). При этом элементы 34, 35, 37 ПЗЭ 20-23 образуют обычное БП, осуществляющее жесткое резервирование дефектных ЭП накопителя. В предлагаемом устройстве применяется код Хеммингэ, исправляющий однократные и выявляющий двухкратные ошибки. Используется также следующее свойство кода Хемминга, синдром двухкратной ошибки равен сумме по модулю 2, образующих ее однократных ошибок.

ПЗЭ БПП 2 разбиваются на четыре группы в зависимости от хранимой в ЗЭ 38 информации (фиг. 4). В первой группе ПЗЭ 20 хранится адрес строки или столбцов, образующих слово данных, который поступает с внешних адресных входов устройства 14. Во вторую группу ПЗЭ 21 в режиме считывания через мультиплексор 41 записывается синдром однократной ошибки с выходов блока формирования синдрома 5. Треть) группа ПЗЭ 22, во-первых, хранит флаговую информацию о том, что в ПЗЭ 20 и 21 произведена запись соответствующих данных и тем самым предотвращает повторную запись в ПЗЭ данной строки, а во-вторых, обеспечивает последовательную выборку строк БПП 2 для записи информации об обнаруженных однократных ошибках. Запись в ЗЭ 38 ПЗЭ 22 производится через мультиплексор 41 с выхода элемента И 33. Элементы И 33 всех строк БПП 2, начиная со второй, блокируются сигналами О с выходов ЗЭ 38 ПЗЭ 22 предыдущих строк в состоянии О, в то время как а элемент 38 ПЗЭ 22 первой строки запись осуществляется сразу с выхода однократной ошибки блока формирования синдрома 5. При этом лог. 1 на выходе элемента 38 ПЗЭ 22 информируется элементом НЕ 24 и через мультиплексор 27 блокирует элементы И 39 и 40 в состоянии О, тем самым предотвраш,ается дальнейшее изменение хранимой в ЗЭ 38 первой строки информации и для дальнейшей работы через элемент И 33 выбирается вторая строка БПП 2. В то же время синдром обнаруженной однократной ошибки через блок 7 сумматоров по модулю 2 без изменений поступает на входы первого дешифр,зтора синдрома 9. Результат дешифрации через элементы ИЛИ 11 поступает на управляющие входы блока коррекции 12 и производится исправление однократной ошибки.

Исправленное слово через блок вывода данных 13 передается на внешние информационные выходы устройства 19. Если в считываемом слове ошибки не обнаружено,

то запись в ЗЭ 38 ПЗЭ 20-22 первой строки не производится и устройство работает обычным образом.

При повторных считываниях информации из накопителя 1 внешний адрес на входах 14 как совпадать, так и не совпадать с хранимым в ЗЭ 38 ПЗЭ 20. Совпадение сигналов фиксируется схемами сравнения 36 и элементом И 25. Если сигналы не совпадают, то через элемент ИЛ И-НЕ

5 28 разблокируется элемент И 33 второй (1той) строки и устройство работает в соответствии с предыдущим описанием. Если сигналы совпадают, то схемами сравнения 36 вырабатываются сигналы 1, которые

0 через элемент И 25 подаются на элементы И 26 и ИЛИ-НЕ 28. При этом элементы И 33 последующих строк (начиная со второй) блокируются в состоянии О. Таким образом, удается предотвратить запись в ПЗЭ 205 22 БПП 2 информации об одной и тЬй же ошибке, что было бы возможно при нескольких обращениях по одному адресу и привело бы к снижению эффективности подобной коррекции ошибок. В то же вре0 мл если блрк формированиясиндрома 5 обнаруживает наличие двухкратной ошибки, то с ее второго входа через элемент И 3 на входы элементов И 26 поступает сигнал 1. В результате синдром однократной ошибки, хранящийся в ЗЭ 38 ПЗЭ 21, через блок элементов ИЛИ 4 передается на входы второго дешифратора синдрома 10 и блок 7 сумматоров по модулю 2. В блоке 7 вычисляется синдром второй

0 ошибки. Результаты дешифрации синдромов дешифраторами 9 и 10 складываются в блоке элементов ИЛИ 11 и передаются на управляющие входы блока коррекции 12 для исправления двухкратной ошибки. При отсутствии двухкратных ошибок в считываемом слове на соответствующем выходе схемы формирования синдрома поддерживается состояние О. В результате элементы И 26 блокируются в состоянии О и

0 устройство работает как известные устройства с коррекцией однократных ошибок.

Как показано «а фиг. 4, в ПЗЭ 20 БПП 2 для определения местонахождения слов, содержащих двойную ошибку, может записываться адрес либо строки, либо столбцов, В первом случае предлагаемая схема позволит исправлять двойные ошибки в. разных словах одной строки. Но при этом необходимо учесть, что одна ошибка является одинаковой для всех слов, т.е. она соответствует

одному и тому же разряду слова. Во втором случае фактически производится резервирование столбцового дефекта или сбоя. В зависимости от информационной емкости накопителя и его организации изменяется число ПЗЭ в БПП 2, что может повлиять из выбор структуры БПП 2 (фиг. 4). При этом для организации исправления двухкратных ошибок могут использоваться не все ПЗЭ.

Используемые элементы ПЗЭ 23 отличаются от ПЗЗ 20 тем, что в них нет схемы сравнения 36, а на вход элемента И 40 подается сигнал сразу от блока 8. В результате в режимах предварительного резервирования и пережигания на входы ЗЭ 38 подается адресный сигнал на входах 14, а в рабочем режиме и при проверке результатов предварительного резервирования ЗЭ 38 отключен путем блокировки элемента И 40 в состоянии О.

Формула изобретения Оперативное запоминающее устройство с коррекцией ошибок и оезервированием, содержащее накопитель с резервированием строк и столбцов, блок кодирования, блок формирования синдрома, первый дешифратор синдрома, блок коррекции, блок управления резервированием, блок вывода данных, выходы которого являются информационными выходами устройства, адресные входы накопителя с резервированием строк и столбцов - адресными входами устройства, информационные выходы первой группы накопителя с резервированием строк и столбцов соединены с входами первой группы блока формирования синдрома, входы второй группы которого соединены с информационными выходами второй группы накопителя с резервированием строк и столбцов и с входами первой группы блока коррекции, выходы которого соединены с входами блока вывода данных, информационные входы первой группы накопителя с резервированием строк и столбцов соединены с входами блока управления резервированием, с входами блока кодирования и являются информационными входами устройства, выходы блока кодирования - с информационными входами второй группы накопителя с -резервированием строк и столбцов, управляющий вход которого является входом записи-чтения устройства, управляющий вход блока управления резервированием - входом разрешения резервирования устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены

блок постоянной памяти, второй дешифратор синдрома, элемент И, блок сумматоров по модулю два, первый и второй блоки элементов ИЛИ, адресные входы блока постоянной памяти соединены с адресными входами

накопителя с резервированием строк и столбцов, информационные входы третьей группы которого соединены с выхо,цами первой группы блока постоянной памяти, выходы второй группы которого соединены с входами первого блока элементов ИЛИ, выходы которого соединены с входами второго дешифратора синдрома и с входами первой группы блока сумматоров по модулю два, выходы которого соединены с входами первого дешифратора синдрома, выходы которого соединены с входами первой группы второго блока элементов ИЛИ, входы второй группы которого соединены с выходами второго дешифратора синдрома,

выходы второго блока элементов ИЛИ соединены с .входами второй группы блока коррекции, информационные выходы блока формирования синдрома - с входами второй группы блока сумматоров по модулю два и с информационными входами первой группы блока постоянной памяти, информационные входы второй группы которого соединены с выходами блока управления резервированием, первый

управляющий выход блока формирования синдрома соединен с первым управляющим входом .блока постоянной памяти, второй управляющий вход которого соединен с выходом элемента И, первый вход которого

подключен к второму управляющему выходу блока формирования синдрома, второй вход элемента И соединен с третьим управляющим входом блока постоянной памяти и является входом предварительного

резервирования устройства.

5

От 28 (I-f) (1-/)

S

JJ

23

52

/fJJf/ fj

It

27

2-&

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1644233A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Оперативное запоминающее устройство с резервированием строк | 1986 |

|

SU1462426A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1709396A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

Изобретение относится к вычислительной технике, в частности к запоминающимустройствам, и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Целью изобретения является повышение надежности устройства. Устройство содержит накопитель 1 с резервированием строк и столбцов, блок 2 постоянной памяти, элемент И 3, первый 4 и второй 11 блоки элементов ИЛИ, блок 5 формирования синдрома, блок кодирования 6. блок 7 сумматоров по модулю два, блок управления 8- резервированием, первый 9 и второй 10 дешифраторы син^дрома, блок коррекции 12, блок 13 вывода данных. Устройство позволяет 8 ходе работы выявить двухкратные ошибки и исправить их. 4 ил. /«?.Н>&слсvj о юО)о ^/б Фиг.1

15

2/

«.

1

-

2;

„Jn-«

1751

f iJiC.

J

10

Я«

Ч

25

K.,d.)

0m 25(1)

20

««w

т

,

гж

,N,,

25 4 U

.Л

/fJJ

A

Qmify

у

« e«

Omlif 8 75 8

Qml 8 15 OmS $ (ОГГ133)

Фиг.З

Aipeca

сшрохи.

Ewdpofi фш ользованнш

Адрес строки

столбца

А,.

0

20

21}

21

s

ASjiss

CuHdpw Фмг . ПЗЗ столбца

Фиг 4

cmojiBiis

™.

cmpQKu

Неиспользованные

| Авторское свидетельство СССР NS 1156144 | |||

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| - кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

Авторы

Даты

1992-01-30—Публикация

1989-07-06—Подача