Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти | 1984 |

|

SU1163356A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Устройство для программирования дешифратора | 1987 |

|

SU1531165A1 |

| Дешифратор для запоминающего устройства с резервированием | 1986 |

|

SU1429166A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Способ считывания информации из элементов памяти на полевых транзисторах и формирователь сигналов считывания | 1989 |

|

SU1697118A1 |

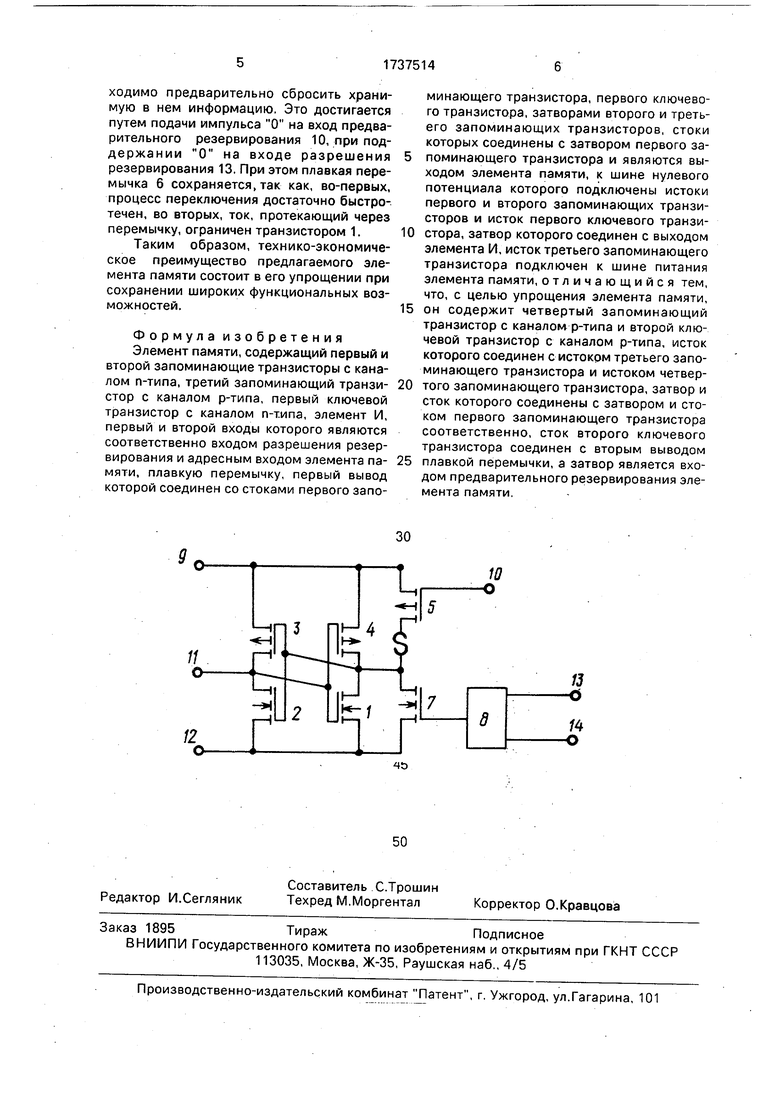

Изобретение относится к вычислительной технике и можег быть использовано при создании запоминающих устройств с повышенным выходом годных и расширенными функциональными возможностями. Целью изобретения является упрощение элемента памяти Поставленная цель достигается тем что элемент памяти содержит четвертый запоминающий транзистор 4 и второй ключевой транзистор 5 с соответствующими связями. При поступлении высокого потенциала ча затвор транзистора 5 плавкая перемычка 6 отключается от шины 9 питания. Это допускает возможность записи в элемент памяти по входам 13,14, т.е. реализовать режим предварительного резервирования 1 ил.

Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств с повышенным выходом годных и расширенными функциональными возможностями

Известен запоминающий элемент на КМДП транзисторах, содержащий плавкую перемычку, управляющий транзистор, запоминающий элемент.

Недостатком этого элемента являются большие аппаратурные затраты на его реализацию.

Наиболее близким к предлагаемому является программируемый постоянный запоминающий элемент, содержащий первый и второй запоминающие транзисторы с каналом N-типа, третий запоминающий транзистор с каналом р-типа, первый ключевой транзистор с каналом N-типа, элемент И, первый и второй входы которого являются соответственно входом разрешения резервирования и адресным входом элемента памяти, плавкую перемычку, первый вывод которой соединен со стоками первого запоминающего транзистора, первого ключевого транзистора, затворами второго и третьего запоминающих транзисторов, стоки которых соединены с затвором первого запоминающего транзистора и являются в-ыходом элемента памяти, к шине нулевого потенциала которого подключены истоки первого и второго запоминающих транзисторов и исток первого ключевого транзистора, затвор которого соединен с выходом элемента И исток третьего запоминающего транзистора подключен к шине питания элемента памяти

Недостаток этого элемента состоит в его повышенной сложности и ограниченных функциональных возможностях, так как для реализации функции предварительного резервирования в данном устройстве необходимо использовать второй запоминающий элемент с соответствующими связями.

XI СА) СЛ

Ј

Цель изобретения -упрощение элемента памяти.

Поставленная цель достигается тем, что в элемент памяти, содержащий первый и второй запоминающие транзисторы с каналом N-типа, третий запоминающий транзистор с каналом р-типа, первый ключевой транзистор с каналом N-типа, элемент И, первый и второй входы которого являются соответственно входом разрешения резервирования и адресным входом элемента памяти, плавкую перемычку, первый вывод которой соединен со стоками первого запоминающего транзистора, первого ключевого транзистора, затворами второго и третьего запоминающих транзисторов, стоки которых соединены с затворами первого запоминающего транзистора и являются выходом элемента памяти, к шине нулевого потенциала которого подключены истоки первого и второго запоминающих транзисторов и исток первого ключевого транзистора, затвор которого соединен с выходом элемента И, исток третьего запоминающего транзистора подключен к шине питания элемента памяти, введен четвертый запоминающий транзистор с каналом р-типа и второй ключевой транзистор с каналом р- типа, исток которого соединен с истоком третьего запоминающего транзистора и истоком четвертого запоминающего транзистора, затвор и сток которого соединены с затвором и стоком первого запоминающего транзистора соответственно, сток вюрого ключевого транзистора соединен со вторым выводом плавкой перемычки, а затвор является входом предварительного резервирования элемента памяти.

По сравнению с известным в предлагаемом техническом решении введены четвертый запоминающий и второй ключевой транзисторы р-типа, а также новые связи между перечисленными и известными элементами.

Введение запоминающего и ключевого транзисторов р-типа и новых связей между новыми элементами и известными позволяет использовать предполагаемый элемент в режиме предварительного резервирования, значительно упростив его по сравнению с известным.

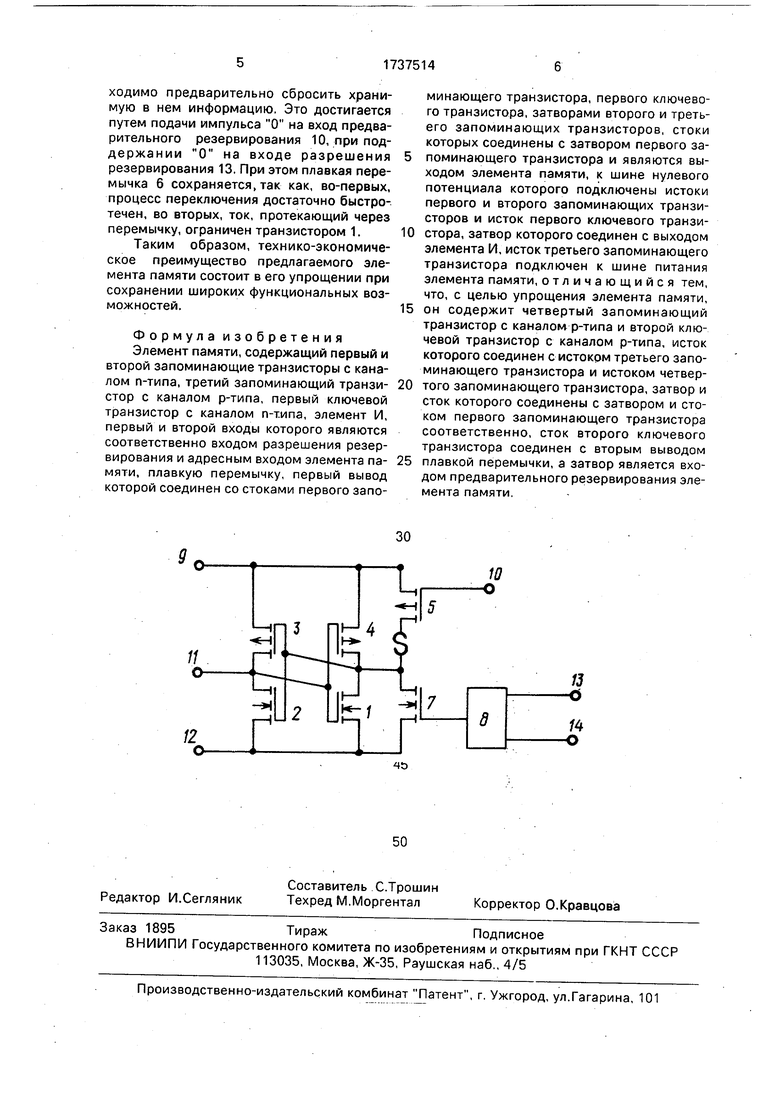

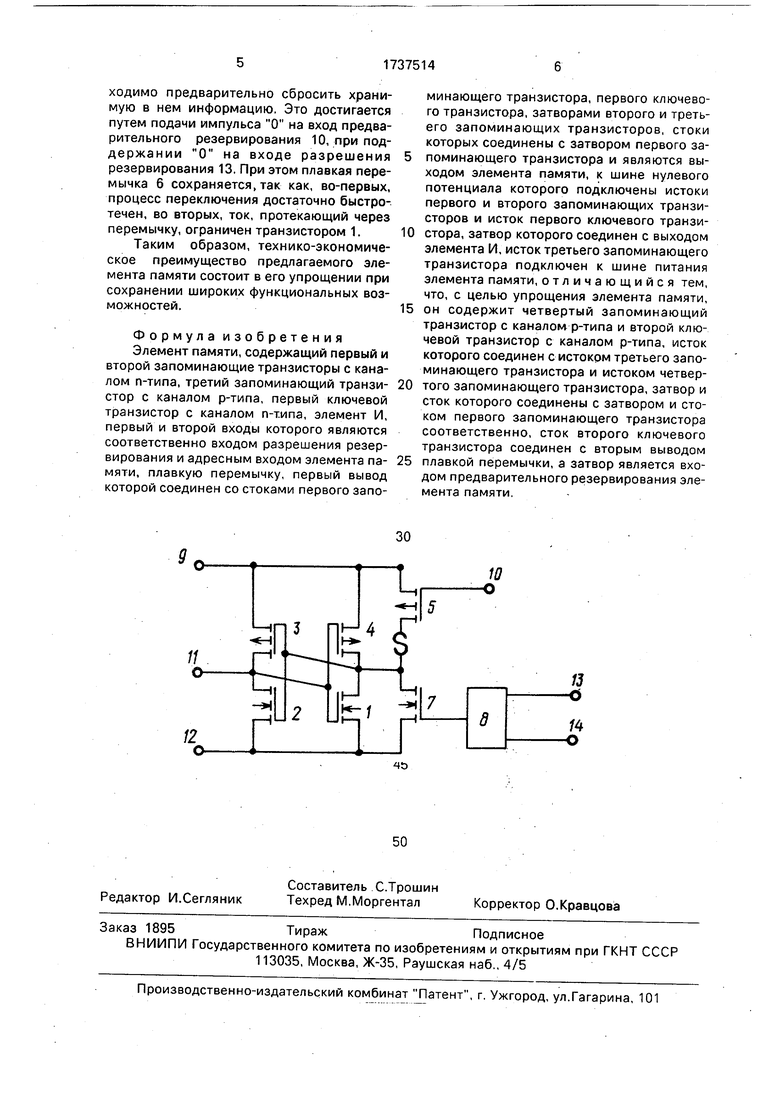

На чертеже приведена схема предлагаемого элемента памяти.

Элемент памяти содержит транзисторы 1-4, образующие запоминающий элемент, второй ключевой транзистор 5, плавкую перемычку 6, первый ключевой транзистор 7, элемент И 8, шину питания 9, вход предварительного резервирования 10,выход 11, шину нулевого потенциала 12, вход

разрешения резервирования 13, адресный вход 14.

Истоки 3 и 4 транзисторов запоминающего элемента соединены с шиной питания

9, а стоки транзисторов 2 и 3 с затворами транзисторов 1 и 4 и выходом элемента 11. Истоки транзисторов 1 и 2 запоминающего элемента подключены к шине нулевого потенциала 12 и истоку первого ключевого

0 транзистора 7, сток которого соединен со стоками транзисторов 1 и 4, затворами транзисторов 2 и 3 и первым выводом плавкой перемычки 6. Затвор первого ключевого транзистора 7 подключен к выходу элемента

5 И 8, первый и второй входы которого соединены с входом разрешения резервирования 13 и адресным входом 14 соответственно. Второй вывод плавкой перемычки 6 подключен к стоку второго ключевого транзистора

0 5. затвор и исток которого соединены с входом предварительного резервирования 10 и шиной питания 9 соответственно.

Элемент памяти работает следующим образом,

5В рабочем режиме на входы предварительного резервирования 10 и разрешения резервирования 13 поданы сигналы О. В результате транзистор 5 открыт, а транзистор 7 закрыт и состояние элемента опреде0 ляется состоянием перемычки 6. После пережигания перемычки 6 на выходе элемента 11 устанавливается 1, что обеспечивается асимметрией запоминающего элемента. Асимметрия запоминающего эле5 мента может быть достигнута за счет различной ширины каналов, образующих его транзисторов 1-4. Если перемычка 6 сохранена, то узловая стоковая емкость транзисторов 1,4 и 7 заряжается до напряжения

0 питания и на выходе элемента 11 устанавливается состояние О.

При подаче сигнала 1 на вход предварительного резервирования 10 элемент переходит в режим предварительного

5 резервирования. В этом случае транзистор 5 закрывается и наличие плавкой перемычки на работе элемента не сказывается. Запись в запоминающий элемент 1-4 адреса дефектного элемента памяти производится

0 при подаче сигнала 1 на вход разрешения резервирования 13. При этом в зависимости от значения адреса остается закрытым либо открывается транзистор 7 так, что при адресном сигнале 1 (О) на выходе 11 также

5 устанавливается 1 (О). Проверка результатов резервирования может быть проведена при понижении сигнала на входе разрешения резервирования 13 до уровня О. Для перепрограммирования запоминающего элемента на транзисторах 1-4 необходимо предварительно сбросить хранимую в нем информацию. Это достигается путем подачи импульса О на вход предварительного резервирования 10, при поддержании О на входе разрешения резервирования 13. При этом плавкая перемычка 6 сохраняется, так как, во-первых, процесс переключения достаточно быстротечен, во вторых, ток, протекающий через перемычку, ограничен транзистором 1.

Таким образом, технико-экономическое преимущество предлагаемого элемента памяти состоит в его упрощении при сохранении широких функциональных возможностей.

Формула изобретения Элемент памяти, содержащий первый и второй запоминающие транзисторы с каналом n-типа, третий запоминающий транзи- стор с каналом р-типа, первый ключевой транзистор с каналом n-т.ипа, элемент И, первый и второй входы которого являются соответственно входом разрешения резервирования и адресным входом элемента па- мяти, плавкую перемычку, первый вывод которой соединен со стоками первого запоминающего транзистора, первого ключевого транзистора, затворами второго и третьего запоминающих транзисторов, стоки которых соединены с затвором первого запоминающего транзистора и являются выходом элемента памяти, к шине нулевого потенциала которого подключены истоки первого и второго запоминающих транзисторов и исток первого ключевого транзистора, затвор которого соединен с выходом элемента И, исток третьего запоминающего транзистора подключен к шине питания элемента памяти, отличающийся тем, что, с целью упрощения элемента памяти, он содержит четвертый запоминающий транзистор с каналом р-типа и второй ключевой транзистор с каналом р-типа, исток которого соединен с истоком третьего запоминающего транзистора и истоком четвертого запоминающего транзистора, затвор и сток которого соединены с затвором и стоком первого запоминающего транзистора соответственно, сток второго ключевого транзистора соединен с вторым выводом плавкой перемычки, а затвор является входом предварительного резервирования элемента памяти.

31Г

| Патент США № 4571707, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Узел памяти | 1989 |

|

SU1635215A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-05-30—Публикация

1990-01-26—Подача