Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля многомодульных логических блоков Дискрет- .ных устройств.

Цель изобретения - увеличение достоверности и глубины контроля,

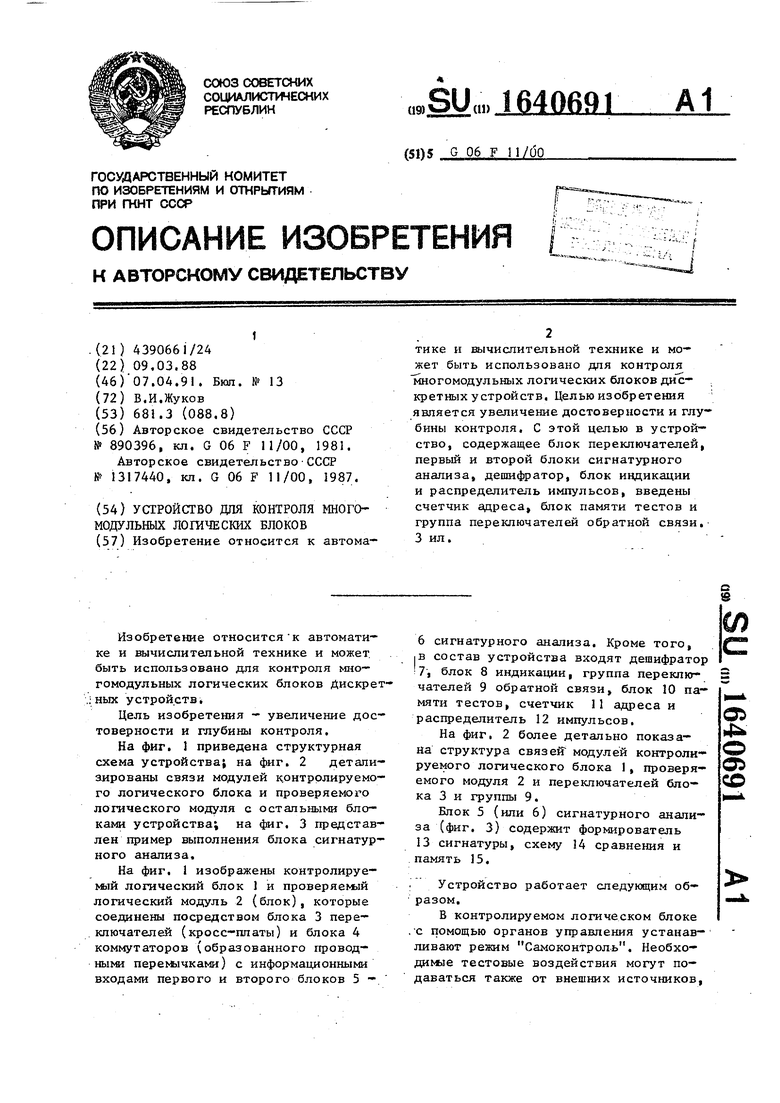

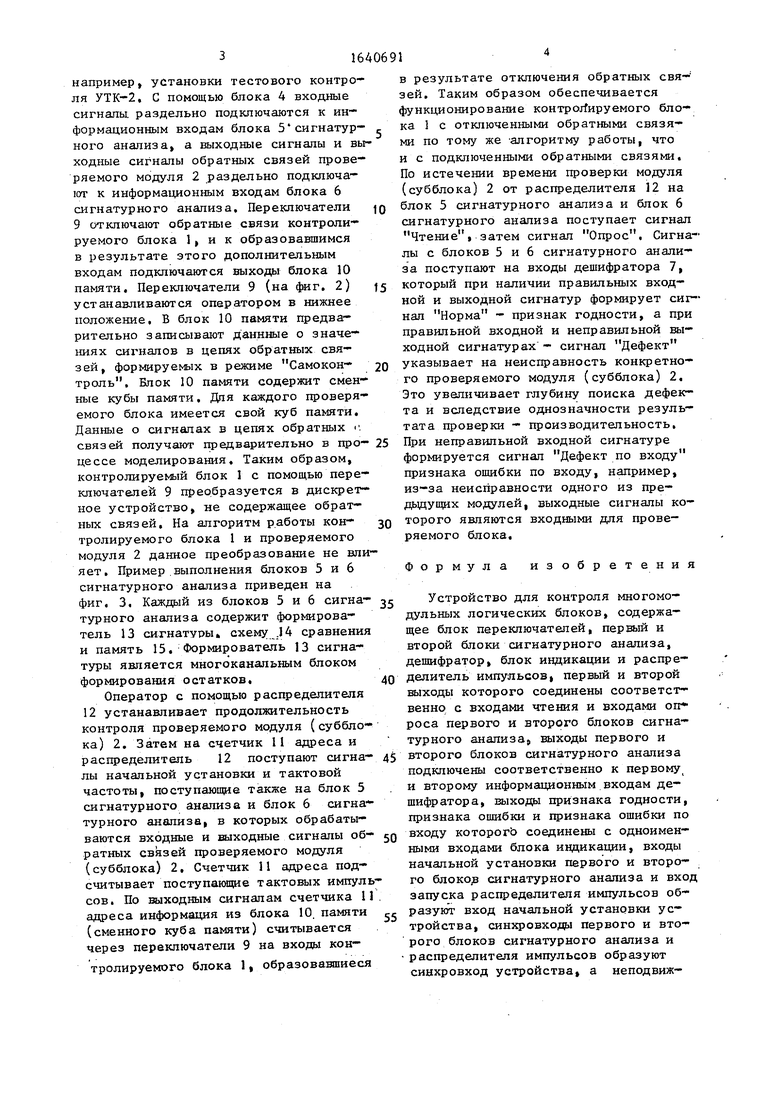

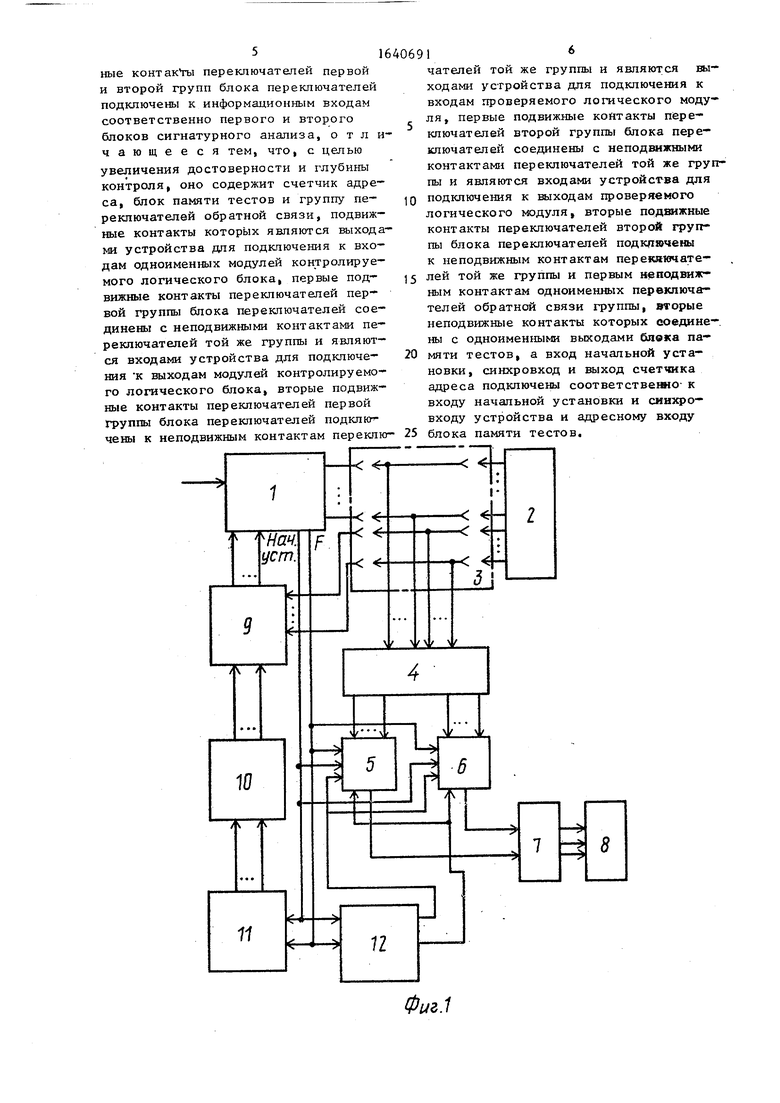

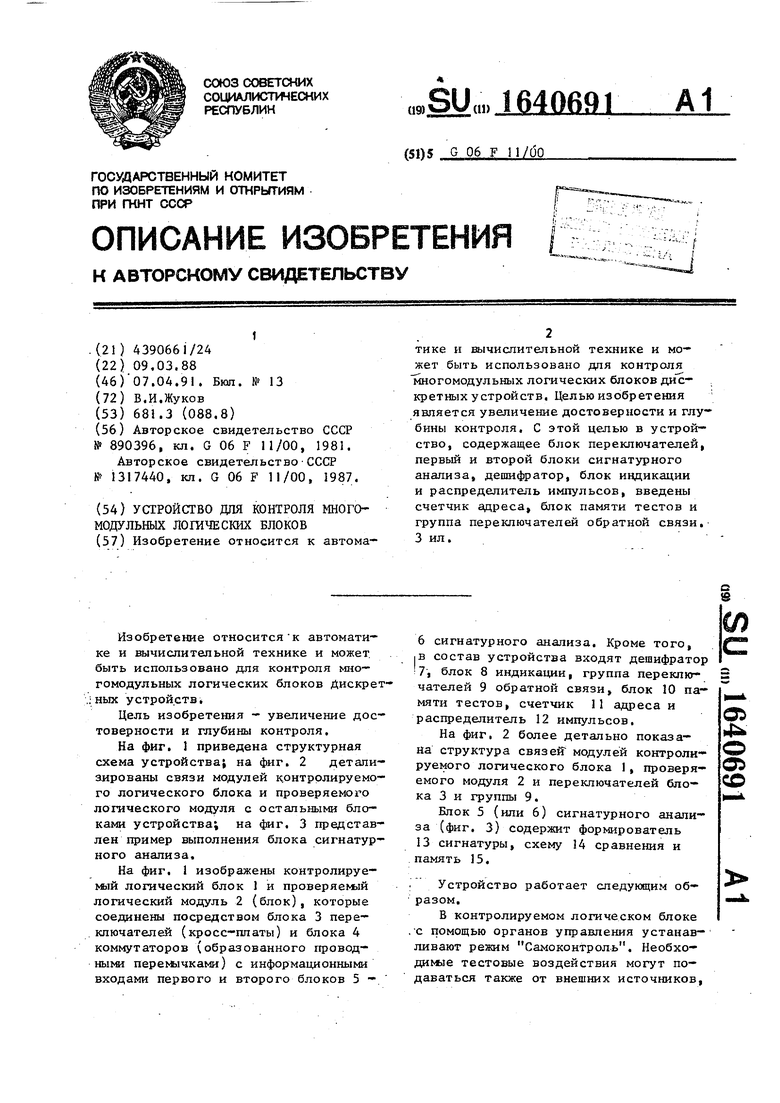

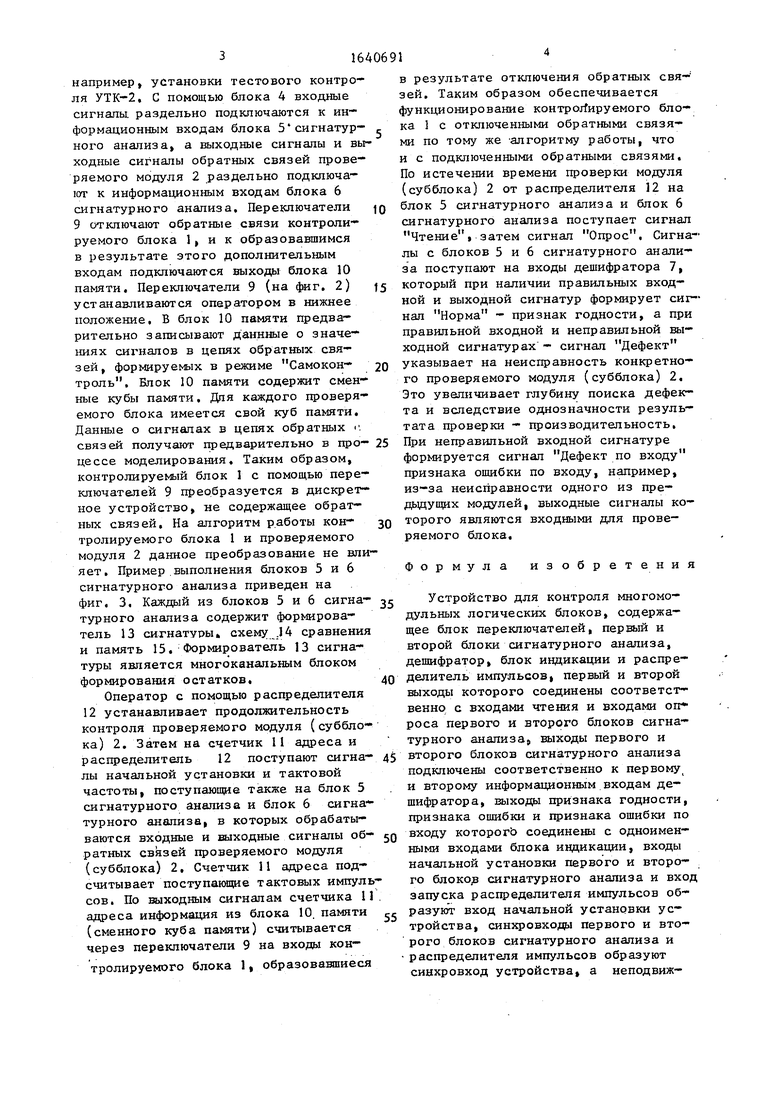

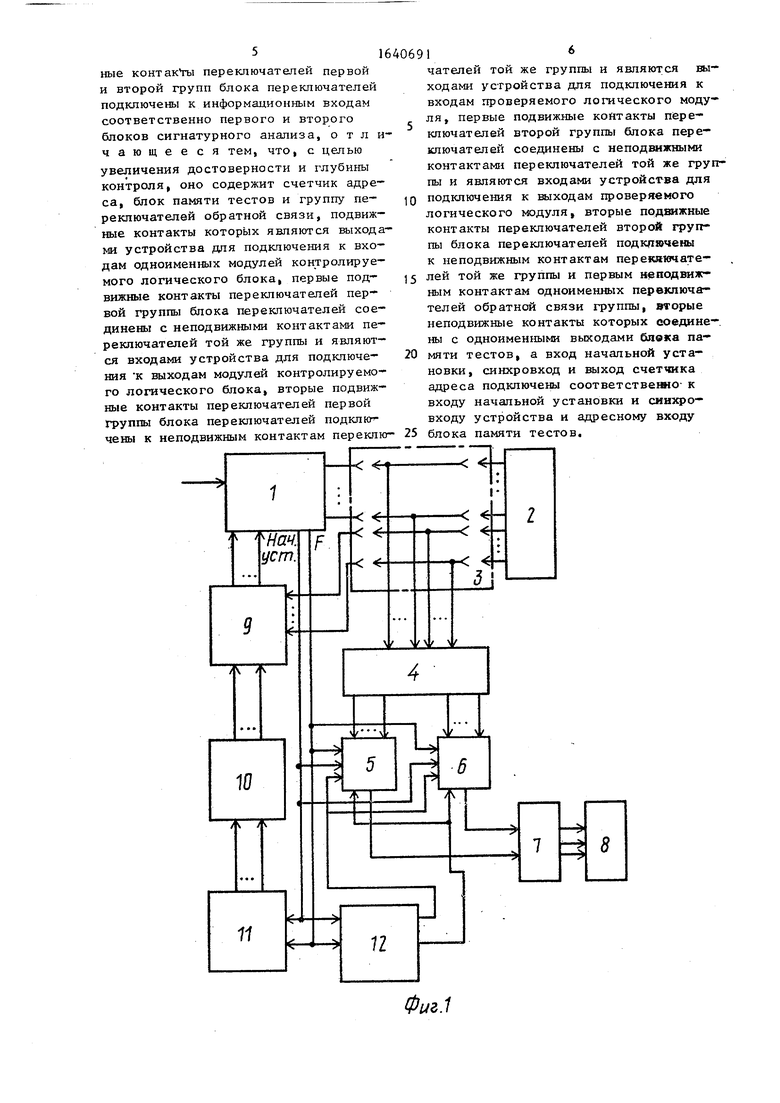

На фиг. 1 приведена структурная схема устройства; на фиг. 2 детализированы связи модулей контролируемого логического блока и проверяемого логического модуля с остальными блоками устройства; на фиг. 3 представлен пример выполнения блока сигнатурного анализа.

На фиг, 1 изображены контролируемый логический блок 1 и проверяемый логический модуль 2 (блок), которые соединены посредством блока 3 переключателей (кросс-платы) и блока 4 коммутаторов (образованного проводными перемычками) с информационными входами первого и второго блоков 5 6 сигнатурного анализа. Кроме того, IB состав устройства входят дешифратор 7, блок 8 индикации, группа переключателей 9 обратной связи, блок 10 памяти тестов, счетчик 11 адреса и распределитель 12 импульсов.

На фиг, 2 более детально показана структура связей модулей контролируемого логического блока 1, проверяемого модуля 2 и переключателей блока 3 и группы 9.

Блок 5 (или 6) сигнатурного анализа (фиг. 3) содержит формирователь 13 сигнатуры, схему 14 сравнения и память 15.

Устройство работает следующим образом.

В контролируемом логическом блоке ,с помощью органов управления устанавливают режим Самоконтроль. Необходимые тестовые воздействия могут подаваться также от внешних источников,

ОЭ 4

О 0 СО

например, установки тестового контроля УТК-2, С помощью блока 4 входные сигналы раздельно подключаются к информационным входам блока 5 сигнатур- ного анализа, а выходные сигналы и выходные сигналы обратных связей проверяемого модуля 2 раздельно подключают к информационным входам блока 6 сигнатурного анализа. Переключатели 9 отключают обратные связи контролируемого блока 1, и к образовавшимся в результате этого дополнительным входам подключаются выходы блока 10 памяти. Переключатели 9 (на фиг. 2) устанавливаются оператором в нижнее положение, В блок 10 памяти предварительно записывают даннные о значениях сигналов в цепях обратных связей, формируемых в режиме Самокон- троль. Блок 10 памяти содержит сменные кубы памяти. Дня каждого проверяемого блока имеется свой куб памяти. Данные о сигналах в цепях обратных связей получают предварительно в про- цессе моделирования. Таким образом, контролируемый блок 1 с помощью переключателей 9 преобразуется в дискретное устройство, не содержащее обратных связей. На алгоритм работы кон- тролируемого блока 1 и проверяемого модуля 2 данное преобразование не влияет . Пример выполнения блоков 5 и 6 сигнатурного анализа приведен на фиг. 3, Каждый из блоков 5 и 6 сигнатурного анализа содержит формирователь 13 сигнатуры схему 14 сравнения и память 15. Формирователь 13 сигнатуры является многоканальным блоком формирования остатков.

Оператор с помощью распределителя 12 устанавливает продолжительность контроля проверяемого модуля (субблока) 2. Затем на счетчик 11 адреса и распределитель 12 поступают сигна лы начальной установки и тактовой частоты, поступающие также на блок 5 сигнатурного анализа и блок 6 сигнатурного анализа, в которых обрабатываются входные и выходные сигналы об- ратных связей проверяемого модуля (субблока) 2, Счетчик 11 адреса подсчитывает поступающие тактовых импульсов. По выходным сигналам счетчика 11 адреса информация из блока 10 памяти (сменного куба памяти) считывается через переключатели 9 на входы контролируемого блока 1, образовавшиеся

а-

JQ15 20 2530

JQ„

35

40

45

в результате отключения обратных связей. Таким образом обеспечивается функционирование контролируемого блока 1 с отключенными обратными связями по тому же алгоритму работы, что и с подключенными обратными связями. По истечении времени проверки модуля (субблока) 2 от распределителя 12 на блок 5 сигнатурного анализа и блок 6 сигнатурного анализа поступает сигнал Чтение, затем сигнал Опрос, Сигналы с блоков 5 и 6 сигнатурного анализа поступают на входы дешифратора 7, который при наличии правильных входной и выходной сигнатур формирует сигнал Норма - признак годности, а при правильной входной и неправильной выходной сигнатурах - сигнал Дефект указывает на неисправность конкретного проверяемого модуля (субблока) 2. Это увеличивает глубину поиска дефекта и вследствие однозначности результата проверки - производительность. При неправильной входной сигнатуре формируется сигнал Дефект по входу признака ошибки по входу, например, из-за неисправности одного из предыдущих модулей, выходные сигналы которого являются входными для проверяемого блока.

Формула изобретения

Устройство для контроля многомодульных логических блоков, содержащее блок переключателей, первый и второй блоки сигнатурного анализа, дешифратор, блок индикации и распределитель импульсов, первый и второй выходы которого соединены соответственно с входами чтения и входами опроса первого и второго блоков сигнатурного анализа выходы первого и второго блоков сигнатурного анализа подключены соответственно к первому и второму информационным входам дешифратора, выходы признака годности, признака ошибки и признака ошибки по входу которого соединены с одноименными входами блока индикации, входы начальной установки первого и второго блоков сигнатурного анализа и вход запуска распределителя импульсов образуют вход начальной установки устройства, синхровходы первого и второго блоков сигнатурного анализа и распределителя импульсов образуют синхровход устройства, а неподвижиные контакты переключателей первой и второй групп блока переключателей подключены к информационным входам соответственно первого и второго блоков сигнатурного анализа, о т л чающееся тем, что, с целью увеличения достоверности и глубины контроля, оно содержит счетчик адреса, блок памяти тестов и группу переключателей обратной связи, подвижные контакты которых являются выходами устройства для подключения к входам одноименных модулей контролируемого логического блока, первые подвижные контакты переключателей первой группы блока переключателей соединены с неподвижными контактами переключателей той же группы и являются входами устройства для подключения -к выходам модулей контролируемого логического блока, вторые подвижные контакты переключателей первой Группы блока переключателей подключены к неподвижным контактам переклю640691

чателей той же группы и являются выходами устройства для подключения к входам проверяемого логического модуля, первые подвижные контакты переключателей второй группы блока переключателей соединены с неподвижными контактами переключателей той же группы и являются входами устройства для

Ю подключения к выходам проверяемого логического модуля, вторые подвижные контакты переключателей второй группы блока переключателей подключены к неподвижным контактам перекиючате15 лей той же группы и первым неподвижным контактам одноименных переключателей обратной связи группы, вторые неподвижные контакты которых соединены с одноименными выходами блока па-

20 мяти тестов, а вход начальной установки, синхровход и выход счетчика адреса подключены соответственно к входу начальной установки и синхро- входу устройства и адресному входу

25 блока памяти тестов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1317440A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля многомодульных логических блоков дискретных устройств. Целью из обретения является увеличение достоверности и глубины контроля. С этой целью в устройство, содержащее блок переключателей, первый и второй блоки сигнатурного анализа, дешифратор, блок индикации и распределитель импульсов, введены счетчик адреса, блок памяти тестов и группа переключателей обратной связи. 3 ил.

Фиг.1

4

Руст

|У

тт

з

10

FT

От счетчика 11 адреса

«h

4

уст.

У

т

U Ф

«r

ЛерВая группа быхоаоо

Вторая группа выходов

К блоку 4

От 5л ока 4

О/п второго Выхода распределителя 12

| Логический анализатор | 1980 |

|

SU890396A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1317440A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-07—Публикация

1988-03-09—Подача